Les contenus liés au tag TSMC

Afficher sous forme de : Titre | FluxDes détails sur le 7nm à l'ISSCC 2017

ASML investit dans Carl Zeiss SMT pour l'EUV

Samsung annonce de futurs process 14 et 10nm

Résultats AMD pour le troisième trimestre

Le 10nm LPE en production chez Samsung

Epyc, ThreadRipper, AMD détaille sa roadmap CPU

AMD tenait ce soir son "Financial Analyst Day", l'occasion de quelques annonces pour le constructeur.

La première concerne le nom commercial de Naples, la déclinaison serveur de Zen. AMD ne réutilisera pas la marque Opteron, la société opposera donc aux Xeon d'Intel des... Epyc. AMD semble avoir prix goût à la stylisation de ses marques à coup de Y ! Certains y verront par contre une référence - probablement non voulue - à l'Itanium d'Intel ...

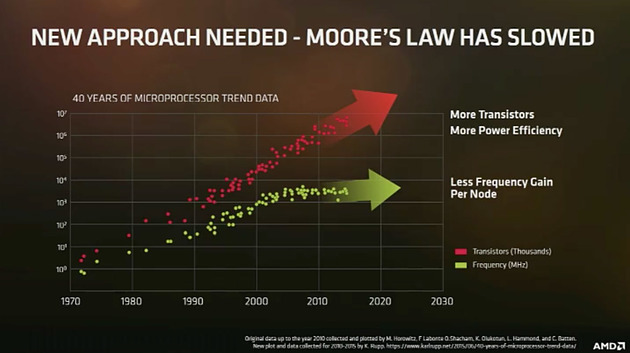

AMD est revenu également sur le ralentissement de la loi de Moore, ou plus exactement le ralentissement des gains apportés par chaque nouveau node. La situation n'est pas nouvelle, ni liée à AMD et ses partenaires fondeurs (Intel a également livré une vision plutôt pessimiste de son 10nm !). AMD reconnaît que les gains de densité et de performances apportés par les nodes vont se réduire, en plus des plafonds de fréquences qui eux ne sont pas nouveaux.

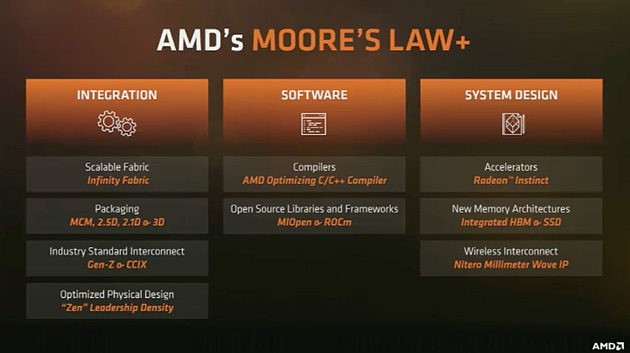

Pour compenser cela AMD met en avant ses initiatives, insistant par exemple son data fabric pour relier des blocs (sur un même die, comme pour Ryzen) ou des dies entre eux (sous le nom Infinity Fabric). Nous admettrons avoir toussé devant le slide ou il était écrit "low latency". Pour le reste AMD mise sur le logiciel, comme sur un nouveau compilateur "optimisé" pour Zen. Baptisé AMD Optimizing C/C++ Compiler (AOCC pour faire court), il s'agit en pratique d'une version "optimisée" de Clang/LLVM 4.0 disponible pour Linux et visant plus spécifiquement la plateforme serveur. Nous n'avons pour le moment pas plus de détails sur les changements effectués par AMD, ni à savoir si ces modifications seront portées dans LLVM (ce qui serait probablement plus utile). La version 1.0 est disponible sur cette page .

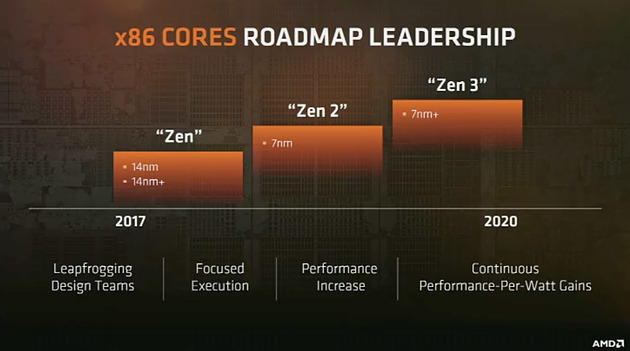

En ce qui concerne la roadmap, AMD ne s'est pas trop avancé avec ce slide assez flou au niveau des dates. On note qu'une version "14nm+" de Zen est prévue ce qui est assez curieux. Officiellement GlobalFoundries propose son 14LPP (Low Power Plus) et bien qu'AMD ne l'ait pas confirmé, on pouvait penser que c'est cette version (et non le 14LPE, E pour Early) qui était utilisée pour Zen étant donné qu'elle l'était déjà pour Polaris. Difficile donc de savoir ce qu'AMD entend par "14+", on pense à une version optimisée du 14LPP à venir (une sorte d'équivalent du 14LPC chez Samsung, même si les deux sociétés ont depuis divergé sur leurs process).

L'autre point à noter est l'absence de 10nm. Là encore ce n'est pas une totale surprise, Global Foundries ne proposera pas de 10nm et si TSMC en proposera un, il sera réservé aux clients gros volume (Apple en particulier). Si AMD reste chez Global Foundries pour Zen2, il faudra attendre fin 2018 si la société tient ses délais. AMD s'est cependant ouvert la possibilité de produire des CPU chez d'autres fondeurs en renégociant le wafer supply agreement qui les lie à Global Foundries. Malheureusement aucune information supplémentaire n'a été donnée sur les timings ou les changements à venir.

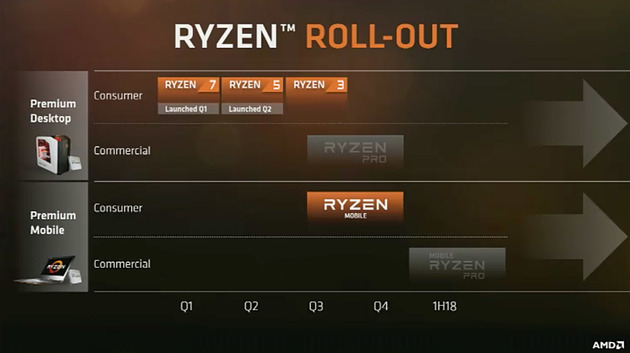

On passera très rapidement sur l'arrivée des versions "Pro" de Ryzen, qui seront simplement des versions destinées à l'entreprise (avec on l'imagine des fonctionnalités manageability comme celles d'Intel) et sur lesquelles aucun détail n'a été donné.

Le constructeur confirme par contre l'arrivée des versions mobiles pour le troisième trimestre. AMD confirme qu'il s'agira bien d'APU basées à la fois sur Zen côté CPU, et sur Vega pour le GPU. Sur le papier l'architecture Zen devrait pouvoir être très compétitive sur ce segment et il sera intéressant de voir si AMD est capable de proposer des produits qui séduiront les OEM.

AMD a enfin confirmé l'existence de Threadripper dont nous vous parlions il y a peu. A l'image d'Intel, AMD utilisera ses puces serveurs pour créer des plateformes desktop haut de gamme. Sur le serveur, AMD proposera avec Naples des puces qui relient quatre dies Zeppelin (le die utilisé pour Ryzen) pour proposer jusqu'a 32 coeurs. Des versions double Zeppelin sont également au programme et c'est celles-ci qui seront utilisées pour la plateforme desktop haut de gamme d'AMD que l'on connaissait sous le nom de code Threadripper. AMD a confirmé le nom de code mais n'en aura pas dit plus. Ces puces utiliseront le monstrueux socket SP3r2 (4094 contacts !). Le lancement interviendra cet été selon AMD et le nom commercial utilisera la marque Ryzen (et non Epyc).

En bref

Cette conférence aux investisseurs, pour la partie CPU, n'a pas été très riche en surprises. AMD est concentré sur le lancement des versions mobiles de Ryzen et est beaucoup moins prolixe sur les évolutions à venir qu'il a pu l'être ces dernières années où communiquer était essentiel pour faire oublier la dette technique accumulée par les FX. On restera curieux d'une éventuelle version de "Zen 1" dans un process 14nm optimisé (que ce soit sous la forme de nouveaux SKU, ou plus simplement pour les APU), même si les gros changements n'interviendront pas avant le 7nm qui, chez Global Foundries, n'est prévu que fin 2018.

La confirmation de ThreadRipper reste une annonce qui embarrassera, au moins sur le papier, son concurrent qui ne pourra plus se vanter du titre - certes un peu futile - du plus grand nombre de coeurs dans un CPU desktop. On retiendra au final surtout la confirmation de l'utilisation de l'architecture graphique Vega sur les APU qui pourrait permettre à AMD, pour le coup, de proposer des produits réellement embarrassants pour son concurrent dont les iGP restent assez modestes, particulièrement depuis qu'Intel semble abandonner ses versions les plus haut de gamme, les GT4e.

Focus : Intel Technology and Manufacturing Day 2017

Intel tenait aujourd'hui son « Technology and Manufacturing Day », l'occasion d'apporter quelques détails sur ses process actuels et à venir. Cette présentation se fait dans un contexte assez compliqué pour le constructeur sur un sujet qu'il dominait pourtant assez largement il y a encore quelques années.

On se souvient en effet qu'Intel a accumulé les retards sur son 14nm, une situation qui ne s'est pas arrangée puisque le 10nm [a lui...

[+] Lire la suite

Le 12FFC de TSMC officialisé

TSMC tenait la semaine dernière son Technology Symposium, l'occasion pour le fondeur taiwanais d'officialiser la dernière version de son process 16nm, le 12FFC. Il s'agit de la quatrième version du 16nm de TSMC après le 16FF, le 16FF+, et le 16FFC, un process qui avait été vaguement évoqué en janvier dernier.

La nomenclature des process est toujours un grand débat, ce "12nm" apporte une bibliothèque de design optimisée (6T contre 7.5/9T précédemment) par rapport au 16FFC qui peut permettre de diminuer jusqu'à 20% la taille des puces qui ne dépassent pas 2.4 GHz. En général, par rapport au 16FFC les gains "moyens" de densité seraient de 9 à 12%, avec une baisse de la consommation de 15%. La production "risque" démarrera en juin. Cette quatrième version du process pourrait être exploitée par les différents clients de TSMC qui n'utiliseront pas le 10nm actuellement en production (ce 10nm, comme le 20nm avant lui, ne sera utilisé que par de très gros clients en volume, comme Apple) et qui attendront le 7nm, le vrai remplaçant en volume de l'actuel 16nm.

A propos du 7nm, TSMC a donné quelques détails supplémentaires. Le constructeur a indiqué avoir obtenu des yields de 76% sur des puces de SRAM de 256 Mbit sur ce nouveau process. Plus intéressant, TSMC aurait produit lors de ses essais un Cortex A72 à plus de 4 GHz. La production risque débutera en avril et la production en volume est prévue pour la première moitié de 2017, sans date précise. Le blog Semiwiki a également confirmé qu'une des différences principales entre le 10nm et le 7nm sera l'introduction du quadruple patterning, en plus de bibliothèques optimisées 6T.

Le fondeur à enfin confirmé qu'il a toujours l'intention de proposer une version EUV de son 7nm à la toute fin de 2018, ce qui semble optimiste. La question de la puissance de la source lumineuse semble se régler, atteignant aujourd'hui 125 watts (on était à 80W l'année dernière) avec en ligne de mire 250 watts pour la production volume. Lors de la conférence SPIE Advanced Lithography Symposium fin février, le blog SemiWiki avait la aussi noté un léger optimisme sur la plupart des questions techniques qui semblent enfin trouver une solution, même si cela risque de provoquer une augmentation des coûts.

12nm et EUV à 7nm pour TSMC

TSMC a publié hier ses résultats financiers pour le dernier trimestre 2016. Le fondeur taiwannais a annoncé pour ce trimestre un revenu brut de près de 7.8 milliards d'euros, en hausse de 28.8% par rapport à la même période sur l'année précédente. Sur la totalité de l'année 2016, TSMC aura augmenté son revenu de 12.4% par rapport à 2015.

Pour 2017, TSMC s'attend à voir ses revenus progresser de "seulement" 5 à 10% (ce qui n'a pas manqué de décevoir les analystes financiers). Lors de la présentation des résultats, quelques informations supplémentaires ont été données.

Morris Chang, Chairman de TSMC s'est lancé dans quelques prédictions pour le marché 2017, s'attendant à voir le marché des smartphones grimper de 6% en unités, et celui du PC se contracter de 5% en unités également (il envisage également un déclin de 7% sur les tablettes tout en voyant le marché Internet of Things progresser de 34%).

Sur le 16/14nm, Morris Chang estime que la part de marché de TSMC est entre 65 et 70%, en dessous de ses attentes (TSMC dispose encore de 80% du marché sur le 28nm par exemple). Toujours poétique, le Chairman voit dans le 10 et le 7nm un "ciel bleu" par rapport à la compétition.

Quelques détails plus techniques ont été donnés, notamment par rapport à un "12nm" qui avait été évoqué ici ou là dans la presse. En pratique, TSMC travaille sur une nouvelle version de son process 16nm (une quatrième après les 16FF, 16FF+ et 16FFC) qui incorpore des améliorations importantes de densité. L'appellation commerciale exacte n'a pas été donnée, et on ne sait pas exactement quand elle sera disponible. On s'attendra dans quelques semaines à une annonce officielle, même si TSMC à confirmé aujourd'hui l'existence de ce "12nm".

Pour le 10nm, si le début de production est bien en cours, le gros du volume se situera sur la seconde partie de l'année (coïncidant avec le lancement des prochains iPhones dont le SoC utilisera le 10nm TSMC).

Sur le 7nm, plus de 20 sociétés travailleraient déjà sur des designs pour l'année prochaine, un chiffre qui devrait doubler dans l'année. Sur la question du 7nm en lui même, nous nous étions interrogés sur la manière dont le constructeur augmenterait la densité. Pour rappel, TSMC s'engage à lancer la production du 7nm dès la fin de l'année, il s'agira du node qu'utiliseront la majorité de ses clients, le 10nm devrait avoir une durée de vie courte et être réservé à quelques gros clients.

Le 10nm rappelle d'une certaine manière le 20nm de TSMC, lui aussi utilisé par des gros clients uniquement avant un passage rapide au 16nm. Cependant, avec une augmentation de la densité de 1.63x entre le 10 et le 7nm, la recette utilisée est plus complexe que pour le passage 20/16nm (qui ne proposait qu'une augmentation de densité de 1.15x). Nos confrères de SemiWiki, très au fait des détails, ont confirmé il y a quelques jours que des changements sur les tailles minimales des cellules sont en grande partie à l'origine des gains de densité et que pour réduire les coûts, TSMC évitera au maximum de généraliser le quadruple patterning (SAQP). Le 10 et le 7nm auront donc bel et bien des similarités techniques.

Pour essayer d'y voir un peu plus clair, et étant donné que plus aucun constructeur ne suit de règles équivalentes pour parler de densité, SemiWiki a publié ce graphique intéressant qui montre une "estimation" de la densité comparée de tous les fondeurs :

D'après SemiWiki, le 10nm d'Intel et le 7nm de TSMC auraient, après ajustement, une densité comparable. Il s'agit bien entendu d'estimations qui valent ce qu'elles valent, vous pouvez retrouver l'explication de la formule utilisée ici , mais elles donnent un bon ordre d'idée de ce à quoi il faut s'attendre (un seul bémol à cette analyse : les prévisions concernant GlobalFoundries nous semblent excessivement optimistes, en grande partie à cause des annonces de GlobalFoundries qui nous paraissent déconnectées de leur capacité d'exécution ces dernières années).

En pratique le 10nm de TSMC disposera tout de même d'une meilleure densité que l'actuel 14nm d'Intel, TSMC pourra donc se targuer d'avoir dépassé Intel côté process lorsque les premiers produits 10nm seront disponibles plus tard dans l'année. Et si Intel reprendra l'avantage avec "son" 10nm, TSMC sera effectivement - et pour la première fois - à parité dès la fin de l'année en lançant la production de son 7nm. Une situation qui durera un moment, et pour la première fois les constructeurs "fabless" pourront disposer d'un process équivalent en densité à celui d'Intel.

On notera enfin, concernant le 7nm, que TSMC a confirmé qu'ils inséreront l'EUV au bout d'un an de production à 7nm (soit fin 2018) pour créer une nouvelle version du 7nm (à l'image des multiples 16nm). Des propos plutôt optimistes concernant la lithographie EUV qui sera, Mark Liu le rappelle, indispensable à 5nm. Et un timing qui coïncide exactement avec le lancement de la production du 7nm de Samsung qui utilisera elle, dès le début, l'EUV !

Le 10nm de TSMC est bien à l'heure

Il y a quelques jours de cela, le site Digitimes avait fait circuler une rumeur par laquelle TSMC et Samsung disposeraient de yields trop bas pour leur production 10nm. De quoi lancer multiples spéculations sur des retards de production.

Pour rappel, TSMC et Samsung ont annoncé avoir commencé la production en volume (des puces qui se retrouveront donc dans des produits commerciaux) de leurs nouveaux process 10nm au quatrième trimestre.

Pour tenter de couper l'herbe sous le pied des rumeurs, TSMC a confirmé une fois de plus au Taipei Times que non seulement la production avait bien commencé au quatrième trimestre, mais que le 10nm générerait des revenus pour TSMC dès le mois prochain - ce qui signifie en pratique que TSMC aura livré des puces à ses clients.

Sur la question des clients, Digitimes avait spéculé qu'en plus d'Apple (client traditionnel en début de disponibilité de node pour TSMC), MediaTek et HiSilicon seraient parmi les premiers clients 10nm de TSMC. Des informations plutôt surprenantes pour les deux sociétés qui produisent (en grand volume) des SoC ARM à prix réduit, utilisant les blocs d'IP génériques (les "Cortex-A") dessinés par ARM.

Qualcomm, l'autre client habituel des débuts de nodes chez TSMC aurait cette fois ci misé sur Samsung pour le 10nm. Samsung n'a pas réagit aux rumeurs lancées par Digitimes. On notera cependant qu'il y a quelques semaines de cela, Samsung avait évoqué l'idée de mieux séparer ses activités. En effet, la marque coréenne entre assez régulièrement en conflit d'intérêts avec les éventuels clients de son activité "fabrication". Une situation que l'on a vue à de nombreuses reprises avec Apple par exemple.

Qualcomm, l'autre client habituel des débuts de nodes chez TSMC aurait cette fois ci misé sur Samsung pour le 10nm. Samsung n'a pas réagit aux rumeurs lancées par Digitimes. On notera cependant qu'il y a quelques semaines de cela, Samsung avait évoqué l'idée de mieux séparer ses activités. En effet, la marque coréenne entre assez régulièrement en conflit d'intérêts avec les éventuels clients de son activité "fabrication". Une situation que l'on a vue à de nombreuses reprises avec Apple par exemple.

Une restructuration qui séparerait les équipes de design de puces utilisées par Samsung (LSI et SoC) de l'activité "fab" serait donc envisagée selon nos confrères de Business Korea . Une séparation qui servirait surtout à rassurer d'éventuels clients car en pratique Samsung ne compte pas se séparer de son activité "fab".