Les derniers contenus liés aux tags TSMC et ASML

Afficher sous forme de : Titre | Flux16nm à l'heure, EUV en retard pour TSMC

ASML vend 15 machines EUV à Intel

Quelques (bonnes !) nouvelles de l'EUV

TSMC va céder sa participation dans ASML

L'EUV prêt chez ASML pour 2015 ?

TSMC confiant sur l'EUV en volume pour 2019

ASML investit dans Carl Zeiss SMT pour l'EUV

L'EUV possiblement pour le 7nm ?

TSMC vise 2020 pour le 5nm via l'EUV

ASML confirme les retards sur l'EUV

TSMC confiant sur l'EUV en volume pour 2019

TSMC a également annoncé ses résultats un peu plus tôt dans le mois, l'occasion d'une conférence auprès des analystes qui aura été la dernière de Morris Chang, le Chairman et fondateur de TSMC. Il avait annoncé en fin d'année dernière qu'il prendrait sa retraite en juin 2018.

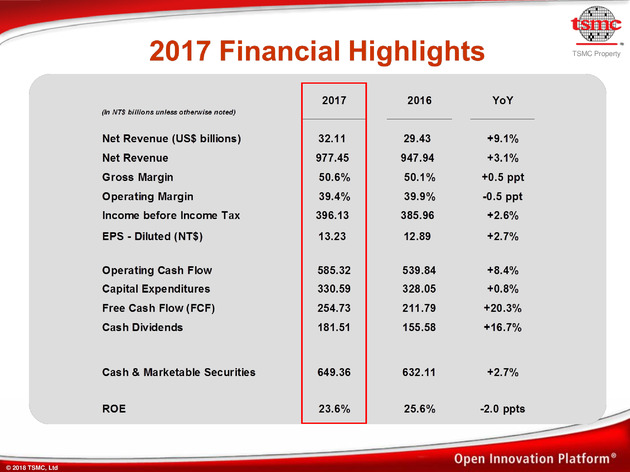

Sur l'année 2017, TSMC a réalisé un chiffre d'affaire de 32.1 milliards de dollars pour un résultat net de 11.2 milliards. Des chiffres qui progressent modestement en apparence par rapport à 2016, +3.1% et +2.6% en New Taiwan Dollar (+9.1% en dollars US, avec les effets du change).

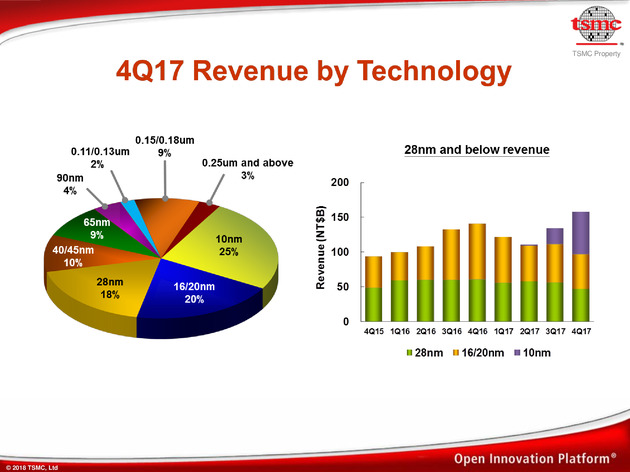

On notera que sur le dernier trimestre, le 10nm (utilisé quasi exclusivement par Apple) représente 25% du chiffre réalisé ce qui est assez massif. Sur 2017, le 10nm aura compté pour 10% du chiffre de TSMC. Les technologies "avancées", à savoir le 28nm et les nodes suivant ont compté pour 58% du chiffre d'affaire engrangé par les ventes de wafers, contre 54% en 2016.

Les futurs process ont été évoqués, le 5nm (qui utilisera l'EUV chez TSMC) est prévu pour une production risque au premier trimestre 2019. TSMC indique avoir déjà atteint de bons yields sur des puces test de SRAM, et le niveau de développement est aussi avancé que pour le 7nm.

En ce qui concerne l'EUV, TSMC s'est félicité d'avoir obtenu des yields élevés en 7nm+ (la version EUV du 7nm de TSMC qui sera introduite dans un second temps) et 5nm. La question des sources lumineuses semble en passe d'être réglée, TSMC indiquant utiliser actuellement des sources 160 watts (on était à 125W l'année dernière), tandis que les sources 250W (annoncées par ASML l'été dernier) sont installées en voie de production. TSMC dit également être optimiste autour des questions compliquées autour du pelliculage avec des défauts bas. La société s'attend donc à ce que la production en volume du 7nm+ en EUV soit lancée au second trimestre 2019, et en 2020 pour le 5nm.

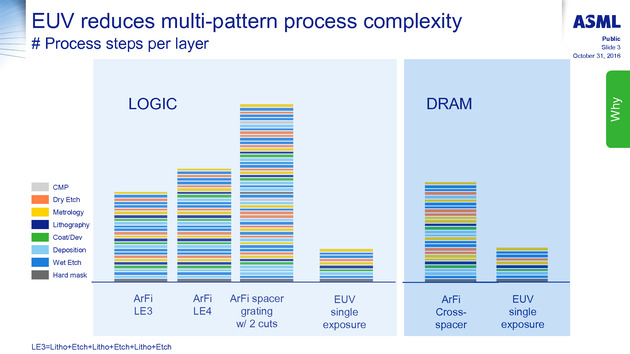

Le 7nm+ est annoncé comme 10% plus performant que le 7nm, et proposera des puces 10% plus petites en moyenne. TSMC n'a pas détaillé les gains directs obtenus en termes de réduction de couches, indiquant simplement un cas ou trois couches immersion peuvent être remplacées par une seule EUV.

Pour l'avenir proche, TSMC a annoncé avoir effectué le tapeout de 10 produits pour le 7nm (avec 10 tapeouts supplémentaires attendus au premier trimestre, et 50 attendus d'ici fin 2018), avec des qualifications en cours qui s'effectuent en parallèle dans deux fabs. Contrairement au 10nm qui n'a été utilisé que par Apple, le 7nm sera utilisé par tous les clients de TSMC. La production en volume commencera en juin et comme toujours, Apple devrait avoir la priorité (quelques produits au compte goutte pourraient être annoncés en 7nm vers la fin de l'année chez les plus petits clients de TSMC, C.C Wei indiquant qu'un décalage entre "smartphone" et HPC de quelques trimestre est attendu).

En 2018 c'est surtout en "12nm" (le 12FFC qui est la quatrième version du 16nm de TSMC) que l'on verra arriver des produits dans le monde du PC. Plus de 120 tapeouts de produits sont encore attendus sur ce node en 2018. A noter que TSMC ouvrira en mai son usine de Nanjing, en Chine, avec un peu d'avance sur son planning suite à une forte demande.

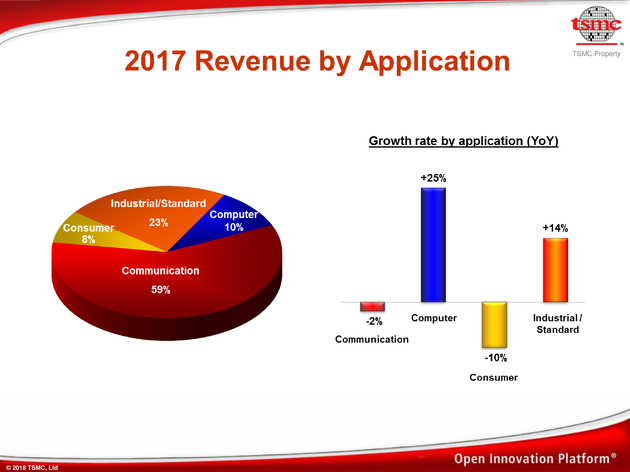

On note qu'en 2018, TSMC s'attend à ce que l'essentiel de sa croissance vienne de sa branche "high performance computing" et pointe particulièrement les GPU (...et les ASIC utilisés pour les crypto-monnaies). Morris Chang aura indiqué s'attendre à une hausse du marché du semi conducteur en 2018 comprise entre 6 et 8%.

La question de l'enquête anti-trust de la commission européenne , poussée par GlobalFoundries aura été vite balayée, TSMC indiquant rejeter les accusations de son concurrent. TSMC continue de se présenter comme la "Foundry de tout le monde" pour contrer l'argument, et tacler au passage Samsung en sous entendant qu'ils ne sont pas en compétition avec leurs clients. On terminera par un mot sur le 3nm, TSMC a indiqué qu'il continuait l'exploration de la technologie et que ces derniers mois, le manager du programme était de plus en plus positif, ne doutant plus de la simple faisabilité comme cela pouvait être le cas l'année dernière.

ASML investit dans Carl Zeiss SMT pour l'EUV

ASML a annoncé hier qu'il comptait s'offrir un quart de Carl Zeiss SMT (24.9%) pour un montant de près de un milliard d'euros. Zeiss SMT est la filiale "Semiconductor Manufacturing Technology" du groupe allemand Zeiss spécialisé dans l'optique.

ASML indique dans son communiqué qu'il s'agit de renforcer la collaboration entre les deux sociétés, Zeiss SMT fournissant les systèmes optiques utilisés notamment dans les machines de lithographie EUV.

ASML investira en prime 220 millions d'euros dans le centre de recherche et développement de Zeiss SMT, et financera 540 millions d'investissements sur les 6 prochaines années.

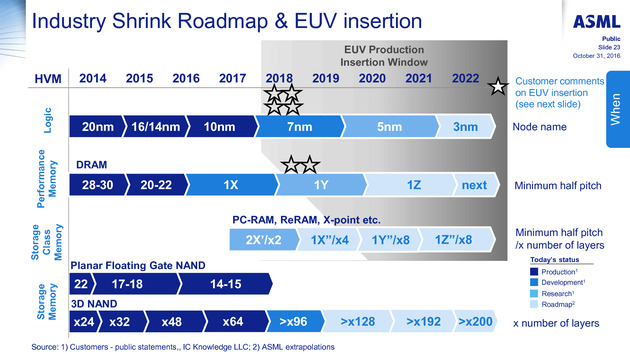

L'enjeu de l'investissement, selon ASML, concerne les futures générations d'EUV avec la possibilité d'étendre la durée de vie de la technologie. Car si certains fabricants de semiconducteurs comme Samsung disent désormais (enfin !) qu'ils utiliseront l'EUV à 7nm, les très nombreux retards de la technologie font qu'elle court le risque de voir sa fenêtre d'utilisation réduite, au risque d'être remplacée par d'autres technologies.

Des systèmes optiques plus complexes avec une ouverture numérique de 0.5 (contre 0.33 pour les premières générations d'EUV) est ce que vise ASML dans cet investissement, qui ne devrait porter ses fruits que d'ici 2024. Il permettrait cependant d'étendre la durée de vie de l'EUV sous les 5nm et pour "plusieurs générations". On sait - en parallèle - qu'autour de 5nm, on atteindra les limites du silicium et l'utilisation d'autres matériaux deviendra nécessaire.

L'intérêt de la lithographie EUV est pour rappel de remplacer la source lumineuse utilisée actuellement par les scanners (elle est générée par des lasers à exciplexe Argon/Fluor avec une longueur d'onde de 193nm) par une source dont la longueur d'onde n'est que de 13.5nm, améliorant fortement les possibilités et réduisant le nombre d'étapes nécessaires pour arriver a fabriquer les puces en évitant la généralisation du multi-patterning.

ASML aurait réitéré à nos confrères d'EEtimes que quatre fabricants de puces, et deux fabricants de mémoires, se sont engagés à faire entrer l'EUV en production en 2018, quelque chose que la firme avait également indiqué dans une présentation aux investisseurs (qui évoquait 2018/2019). Une affirmation qui nous parait bien optimiste !

Aujourd'hui, seuls Samsung et GlobalFoundries se sont engagés publiquement à 7nm, pour des dates qui coïncident. En ce qui concerne TSMC, il faudra attendre le 5nm pour le voir arriver de manière extensive, sa production risque est prévue pour 2019 uniquement. Intel avait annoncé de son côté qu'il n'utiliserait pas l'EUV à 10nm, et qu'au mieux l'EUV était "une option" pour le 7nm. Le 7nm d'Intel utilisera une solution de lithographie a immersion classique. Et côté dates, 2019 semble extrêmement optimiste considérant l'exécution d'Intel ces dernières années (retards massifs sur le 14nm, introduction de Kaby Lake pour retarder le 10nm, lancement du 10nm repoussé à fin 2017 et uniquement sur des références mobiles, sans parler de l'introduction dans la roadmap de Coffee Lake en 2018... et en 14nm !).

En ce qui concerne les fabricants mémoire, Samsung avait évoqué la possibilité sans pour autant s'engager fermement. SK Hynix évoquait l'utilisation de l'EUV vers 2019.

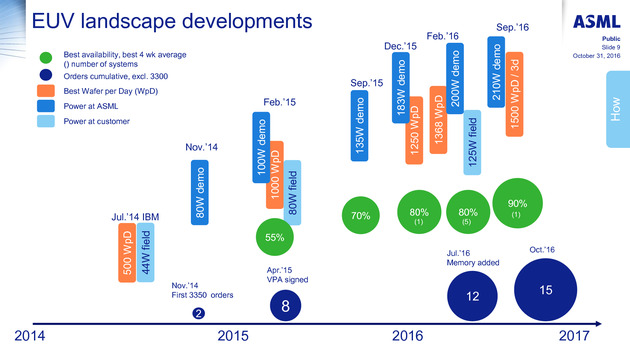

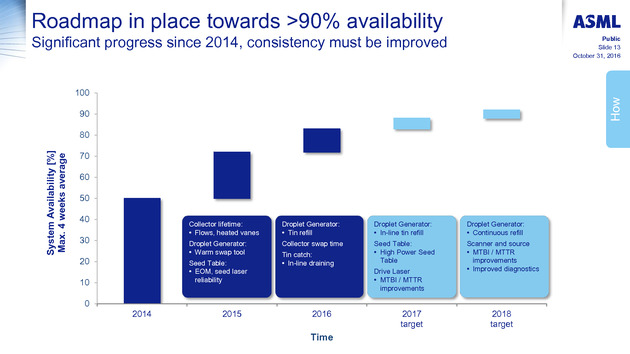

Les machines qui seront utilisées en production, les NXE:3400B, atteindraient d'après ASML un débit de 125 wafers/heure, un progrès notable par rapport à mars 2015 ou ASML se félicitait de 42 wafers/heure (entre 50 et 100 wafers/heure étaient considérés comme le minimum pour éventuellement utiliser la technologie d'après Mark Bohr d'Intel). Pour arriver à ce chiffre, ASML devra augmenter fortement la puissance de la source lumineuse. Le constructeur aurait livré des sources 125W à ses clients cette année qui ont permis d'atteindre 85 wafers/heure.

La question de la disponibilité des machines semble également être meilleure, de seulement 55% à l'époque, ASML atteint aujourd'hui entre 70 et 80%, avec l'objectif d'être a 90% en 2018.

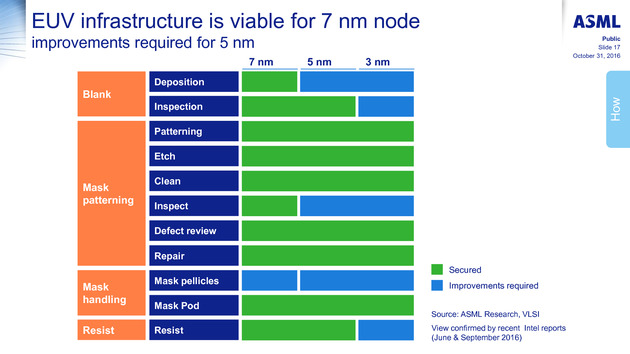

L'enthousiasme d'ASML - le seul à se lancer dans l'EUV - est forcément élevé pour sa technologie mais il faut une fois de plus rappeler que les scanners ne sont qu'une partie de la chaîne de fabrication. Les progrès réalisés, bien qu'importants, ne veulent pas dire que l'EUV est "prêt", loin de là.

La question des masques (la plaque transparente qui contient l'image de la puce à graver) et de l'inspection de leurs éventuels défauts n'a pas encore été résolue. Et si là aussi ASML tente d'apporter sa propre réponse, en pratique le problème reste complexe a solutionner avec des conséquences massives sur la viabilité de la technologie en production (plus de détails dans cet excellent article ).

L'EUV possiblement pour le 7nm ?

Le site SemiWiki nous rapporte quelques informations sur l'état de la fabrication EUV, en provenance de la conférence SPIE Advanced Lithography qui se tient actuellement à San José.

Lors de la même conférence l'année dernière, les nouvelles étaient pour rappel plutôt bonnes (voir le lien pour un rappel complet sur la fabrication des processeurs et l'importance capitale de l'EUV !) et l'on espérait une introduction en cours de process pour le 10nm, et une introduction complète à 7nm. Malheureusement, on le rappelait en janvier, TSMC avait calmé les ardeurs en indiquant qu'il faudrait attendre le 5nm pour une éventuelle introduction de cette technologie.

SemiWiki confirme certains chiffres donnés lors de la dernière conférence aux investisseurs de TSMC, à savoir que la machine avait atteint sur une période de quatre semaines une production de 518 wafers/jour, un niveau encore largement insuffisant. Intel a partagé également quelques chiffres, un peu inférieurs à ceux de TSMC, à savoir entre 2000 et 3000 wafers par semaine (285-428 par jour).

On notera quand même que le taux de disponibilité des scanners de la société ASML a augmenté, passant de 55 à 70% chez TSMC (Intel rapportant une disponibilité identique) ! On notera que s'il est question d'une introduction en début de node à 5nm, TSMC laisse la porte ouverte pour le 7nm si jamais des progrès étaient effectués. Intel de son côté n'a pas donné d'information. Samsung envisagerait l'introduction à 7nm selon les présentations, sans plus de précisions.

Si la question de la disponibilité est importante, celle de la puissance de la source lumineuse l'est encore plus. Après avoir été limité à 40 watts l'année dernière, les machines actuellement en évaluation chez TSMC disposent désormais de sources 80 watts. C'est mieux, mais cela reste loin des 250 watts promis par ASML pour fin 2015. Les dernières prédictions sont désormais de 250 watts en 2016-2017, et au delà en 2018-2019, des plages particulièrement larges.

Atteindre les 250 watts de puissance permettrait d'augmenter significativement la cadence de production, atteignant 170 wafers/heure en théorie. ASML a effectué des démonstrations que TSMC et Intel semblent juger prometteuses de 185 et 200 watts. Reste à les voir en production, bien évidemment. Les challenges de cette technologie restent complexes et ne se limitent pas à ces deux points cruciaux, la question des défauts dans les masques est elle aussi importante même si là aussi TSMC et Intel ont visiblement noté quelques progrès. Vous pouvez retrouver plus de détails sur ces points dans l'article de SemiWiki .

TSMC vise 2020 pour le 5nm via l'EUV

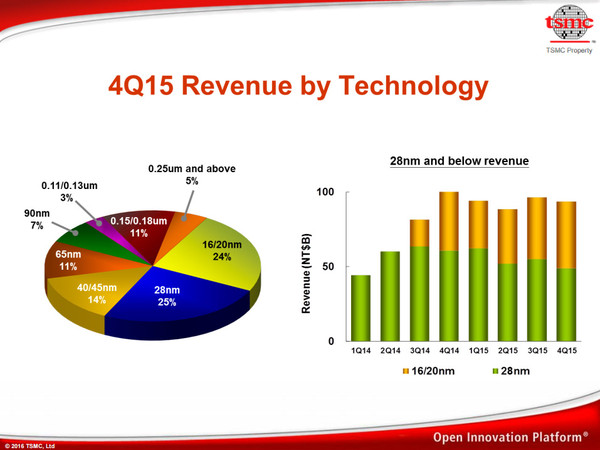

TSMC a présenté ses résultats pour le dernier trimestre 2015, pour une fois ils sont en baisse avec des ventes et un bénéfice qui baissent respectivement de 8.5 et 8.9%. La part du 16/20nm dans les revenus est en hausse, passant sur trois mois de 21 à 24%, ce qui se fait surtout au dépend du 28nm qui passe de 27 à 25%.

Le fondeur se montre confiant pour l'année à venir, indiquant qu'il devrait passer de 40% de parts de marché sur les process 16/14nm à plus de 70% en 2016. Cela se fera via 16FF+ (FinFet+) destiné aux produits les plus performants mais aussi nouveau 16FFC (FinFet Compact) pour le moyen de gamme et la basse consommation.

Pour le reste TSMC a confirmé le 10nm pour 2017, sans donner de date précise. Il y a trois mois il était question d'un début de la production en volume au dernier trimestre 2016 et de premiers revenus au premier trimestre 2017. La production en volume en 7nm a été annoncée pour le premier semestre 2018, et il faudra attendre 2 années supplémentaires avant de voir débarquer le 5nm. Le 5nm devrait finalement être le premier à utiliser l'EUV, mais TSMC travaille encore avec ASML à fiabiliser les machines : il a ainsi pu atteindre sur une période de 4 mois une moyenne de 500 wafer exposés par jour on est assez loin des 1000 wafer qu'elle peut atteindre en pointe.

ASML confirme les retards sur l'EUV

Après Intel, c'est ASML qui dévoile à son tour ses résultats sur le troisième trimestre. L'occasion pour les dirigeants de la société de revenir sur la question de la lithographie EUV, technologie importante pour la fabrication des semi-conducteurs dans les prochaines années, et sur laquelle ASML a massivement misé.

En début d'année l'optimisme était de mise, évoquant un déploiement de l'EUV en cours de vie du node 10nm, et un déploiement complet à 7nm. ASML s'était même félicité d'avoir vendu 15 machines à Intel. Cependant en juillet TSMC avait refroidit les espoirs, indiquant que l'EUV était exclu à 10nm, et n'arriverait peut être qu'en cours de process 7nm.

Nous notions hier qu'Intel avait repoussé la livraison de certaines machines-outils de deux trimestres et il était facile de lire entre les lignes que l'EUV était en cause. Dans leur présentation aux analystes, ASML a indiqué qu'effectivement la livraison de plusieurs machines avait été repoussée, et que seulement 4 machines EUV seraient livrées en 2016 contre sept annoncées. Le choix de repousser l'insertion a 7 et 5nm fait que les commandes ont été repoussées, modifiées vers de nouvelles machines. Derrière la raison des reports, ASML évoque « l'incertitude de ses clients » sur le timing de leurs nodes à venir, ainsi que sur « leurs priorités à court terme ». On y verrait presque un petit tacle envers Intel dont la priorité principale est effectivement les yields en 14nm qui ont été confirmés comme en dessous des attentes hier par le constructeur.

ASML indique que cinq clients sont concernés par les livraisons de machines EUV dans les années à venir pour un total de 11 machines sur les générations 10 et 7nm. Un chiffre plus bas que le nombre de machines supposément vendues à Intel, il s'agissait cependant d'un contrat à long terme basé sur un certain nombre de critères de performances. Une partie de la commande d'Intel sera donc vraisemblablement repoussée sur le 5nm. Au milieu des questions/réponses, le CEO Peter Wennink a confirmé qu'ASML avait misé sur le fait que le 10nm serait un node EUV, ce qui ne sera pas le cas et décale de 6 à 12 mois les demandes de ses clients. Etant donné que l'écart entre deux nodes est plus proche de 24 mois en moyenne, on doutera un peu de cette assertion. En pratique Peter Wennink à confirmé que le déploiement de l'EUV se ferait à partir de 2018/2019 avec des livraisons pour les machines de production courant 2017.

En ce qui concerne les avancées sur les points bloquants derrière l'introduction de l'EUV, ASML est resté relativement muet. La question principale reste la vitesse d'exposition, qui était de 1000 wafers sur une période de 24h (il faut de nombreuses expositions pour réaliser une puce, dont la fabrication prend plusieurs semaines, la vitesse d'exposition est donc un point critique !), un peu en dessous du seuil minimal acceptable (50 à 100 exposition par heure, les machines « classiques » en font 250/h à titre de comparaison). Si ces chiffres semblent proche, l'autre problème est le taux de disponibilité des machines, nous notions la dernière fois que le générateur de goutes d'étain devait être changé tous les quatre jours et que sur une période de 8 semaines, le taux de disponibilité mesuré n'était que de 55%.

Côté rendement, les choses n'ont visiblement pas évolué puisque le même chiffre de 1000 sur une journée a été de nouveau évoqué. ASML indique cependant que sur des périodes de quatre semaines, plusieurs de ses clients ont atteint une disponibilité de plus de 70%. Si l'on pourrait y voir un progrès, le CEO d'ASML a noté qu'il s'agissait de meilleures situations et que la moyenne totale reste plus basse. Peter Wennink a également évoqué que les dernières générations de laser ont posé problème même si ces problèmes seraient résolus.

Le CEO s'est également félicité du fait que deux clients avaient indiqué la « nécessité » de l'EUV à 7nm, même si l'on notera que toutes les annonces que ce soit chez TSMC ou Intel étaient empruntes de prudence, quelque chose de compréhensible vu que des annonces identiques avaient été faites pour le 10nm ! On notera sur la question du 10nm qu'ASML a confirmé que Samsung, TSMC et Intel seront « proches » avec des livraisons à partir du second trimestre. Il a cependant été confirmé que le passage au 10nm serait « complexe » de par le fait que le multiple patterning était généralisé pour de nombreuses couches critiques et qu'il ne faudrait pas sous-estimer le temps nécessaire avant de voir en production ces puces sur le marché.