Les derniers contenus liés aux tags TSMC et 16/14nm

Afficher sous forme de : Titre | Flux16nm à l'heure, EUV en retard pour TSMC

TSMC, résultats et point sur les 20nm, 16nm et 10nm

Le 16nm de TSMC en avance sur son retard

Intel précise son process 14nm

Le 16nm en retard chez TSMC

12nm et EUV à 7nm pour TSMC

Des détails sur le 7nm à l'ISSCC 2017

AMD valide le 14nm LPP de GloFo

Résultats TSMC, 16 FinFET+ dans l'iPhone 6s

L'A9 d'Apple produit par Samsung et TSMC

12nm et EUV à 7nm pour TSMC

TSMC a publié hier ses résultats financiers pour le dernier trimestre 2016. Le fondeur taiwannais a annoncé pour ce trimestre un revenu brut de près de 7.8 milliards d'euros, en hausse de 28.8% par rapport à la même période sur l'année précédente. Sur la totalité de l'année 2016, TSMC aura augmenté son revenu de 12.4% par rapport à 2015.

Pour 2017, TSMC s'attend à voir ses revenus progresser de "seulement" 5 à 10% (ce qui n'a pas manqué de décevoir les analystes financiers). Lors de la présentation des résultats, quelques informations supplémentaires ont été données.

Morris Chang, Chairman de TSMC s'est lancé dans quelques prédictions pour le marché 2017, s'attendant à voir le marché des smartphones grimper de 6% en unités, et celui du PC se contracter de 5% en unités également (il envisage également un déclin de 7% sur les tablettes tout en voyant le marché Internet of Things progresser de 34%).

Sur le 16/14nm, Morris Chang estime que la part de marché de TSMC est entre 65 et 70%, en dessous de ses attentes (TSMC dispose encore de 80% du marché sur le 28nm par exemple). Toujours poétique, le Chairman voit dans le 10 et le 7nm un "ciel bleu" par rapport à la compétition.

Quelques détails plus techniques ont été donnés, notamment par rapport à un "12nm" qui avait été évoqué ici ou là dans la presse. En pratique, TSMC travaille sur une nouvelle version de son process 16nm (une quatrième après les 16FF, 16FF+ et 16FFC) qui incorpore des améliorations importantes de densité. L'appellation commerciale exacte n'a pas été donnée, et on ne sait pas exactement quand elle sera disponible. On s'attendra dans quelques semaines à une annonce officielle, même si TSMC à confirmé aujourd'hui l'existence de ce "12nm".

Pour le 10nm, si le début de production est bien en cours, le gros du volume se situera sur la seconde partie de l'année (coïncidant avec le lancement des prochains iPhones dont le SoC utilisera le 10nm TSMC).

Sur le 7nm, plus de 20 sociétés travailleraient déjà sur des designs pour l'année prochaine, un chiffre qui devrait doubler dans l'année. Sur la question du 7nm en lui même, nous nous étions interrogés sur la manière dont le constructeur augmenterait la densité. Pour rappel, TSMC s'engage à lancer la production du 7nm dès la fin de l'année, il s'agira du node qu'utiliseront la majorité de ses clients, le 10nm devrait avoir une durée de vie courte et être réservé à quelques gros clients.

Le 10nm rappelle d'une certaine manière le 20nm de TSMC, lui aussi utilisé par des gros clients uniquement avant un passage rapide au 16nm. Cependant, avec une augmentation de la densité de 1.63x entre le 10 et le 7nm, la recette utilisée est plus complexe que pour le passage 20/16nm (qui ne proposait qu'une augmentation de densité de 1.15x). Nos confrères de SemiWiki, très au fait des détails, ont confirmé il y a quelques jours que des changements sur les tailles minimales des cellules sont en grande partie à l'origine des gains de densité et que pour réduire les coûts, TSMC évitera au maximum de généraliser le quadruple patterning (SAQP). Le 10 et le 7nm auront donc bel et bien des similarités techniques.

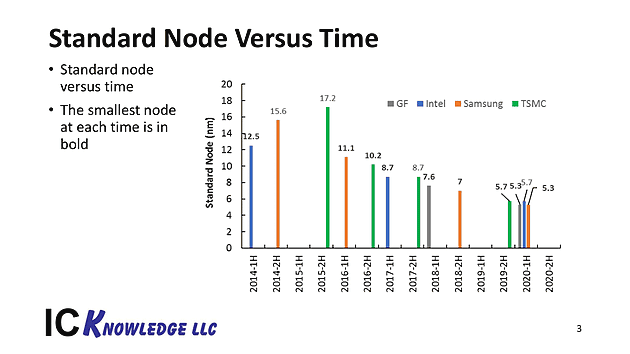

Pour essayer d'y voir un peu plus clair, et étant donné que plus aucun constructeur ne suit de règles équivalentes pour parler de densité, SemiWiki a publié ce graphique intéressant qui montre une "estimation" de la densité comparée de tous les fondeurs :

D'après SemiWiki, le 10nm d'Intel et le 7nm de TSMC auraient, après ajustement, une densité comparable. Il s'agit bien entendu d'estimations qui valent ce qu'elles valent, vous pouvez retrouver l'explication de la formule utilisée ici , mais elles donnent un bon ordre d'idée de ce à quoi il faut s'attendre (un seul bémol à cette analyse : les prévisions concernant GlobalFoundries nous semblent excessivement optimistes, en grande partie à cause des annonces de GlobalFoundries qui nous paraissent déconnectées de leur capacité d'exécution ces dernières années).

En pratique le 10nm de TSMC disposera tout de même d'une meilleure densité que l'actuel 14nm d'Intel, TSMC pourra donc se targuer d'avoir dépassé Intel côté process lorsque les premiers produits 10nm seront disponibles plus tard dans l'année. Et si Intel reprendra l'avantage avec "son" 10nm, TSMC sera effectivement - et pour la première fois - à parité dès la fin de l'année en lançant la production de son 7nm. Une situation qui durera un moment, et pour la première fois les constructeurs "fabless" pourront disposer d'un process équivalent en densité à celui d'Intel.

On notera enfin, concernant le 7nm, que TSMC a confirmé qu'ils inséreront l'EUV au bout d'un an de production à 7nm (soit fin 2018) pour créer une nouvelle version du 7nm (à l'image des multiples 16nm). Des propos plutôt optimistes concernant la lithographie EUV qui sera, Mark Liu le rappelle, indispensable à 5nm. Et un timing qui coïncide exactement avec le lancement de la production du 7nm de Samsung qui utilisera elle, dès le début, l'EUV !

Des détails sur le 7nm à l'ISSCC 2017

La conférence ISSCC (International Solid-State Circuits Conference) se tiendra pour son édition 2017 du 5 au 9 février à San Francisco, et nos confrères d'EEtimes ont eu accès à l'avant programme.

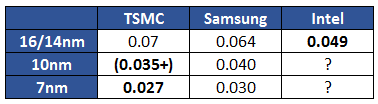

Comme tous les ans les acteurs du milieu des semi conducteurs y présenterons leurs nouveautés, et l'on notera que TSMC et Samsung présenterons leurs cellules SRAM (utilisées notamment pour la mémoire cache dans les puces). L'année dernière, Samsung avait proposé deux versions distinctes pour son process 10nm, optimisées pour la densité ou les performances, de 0.040 µm² et 0.049 µm².

D'après nos confrères, TSMC présentera une cellule SRAM 7nm de seulement 0.027µm², tandis que Samsung présentera une cellule SRAM 7nm de 0.030µm², mais fabriquée en EUV. D'après Samsung, l'EUV permettrait de diminuer la tension minimale nécessaire de 39.9mV (TSMC indique aussi des optimisations basse tension, on attendra la conférence pour comparer l'impact ou non de l'EUV).

La SRAM est un composant fondamental des puces et sa taille permet en général de se donner une bonne idée des process. Cependant il faut être assez méfiant, les constructeurs annonçant parfois des "records" de densité qu'ils n'utilisent pas forcément en production. Nous avons rapporté dans le tableau ci dessous les chiffres les plus bas (correspondant aux bibliothèques "hautes densité") pour TSMC, Samsung et Intel :

Par rapport au tableau, on notera qu'Intel n'utilise pas cette SRAM haute densité dans ses processeurs, mais de la SRAM 0.059 µm². Même en prenant cela en compte, Intel garde la meilleure densité à 16/14nm pour la SRAM. Le constructeur ne fournit pas encore d'infos sur ses futurs process.

TSMC n'a pas donné non plus de chiffre exact pour son 10nm, estimant simplement 50% de réduction par rapport à son 16nm sur la SRAM, ce qui nous vaut un chiffre entre parenthèses. Selon toutes vraisemblances, et conformément aux autres annonces sur la densité (2.1x d'après le constructeur), on estimera que TSMC devrait avoir une SRAM d'une taille légèrement inférieure à celle de Samsung.

Intel ne devrait pas effectuer d'annonce sur ce sujet lors de l'ISSCC, ce qui est assez dommage. Le constructeur devrait présenter les FPGA Altera Stratix 10 (14nm) tandis qu'AMD proposera une présentation plus en détails de Zen.

On notera aussi que Western Digital/Toshiba, ainsi que Samsung, présenterons des puces 3D NAND 512 Gbit TLC 64 couches. Dans le cas de Samsung, cette puce avait été annoncée cet été, plus de détails techniques devraient être disponibles. Pour Western Digital/Toshiba, cette puce avait été évoquée cet été comme objectif.

On notera que nos confrères pointent à raison un grand absent : une fois de plus, ni Intel, ni Micron, n'effectueront de présentation technique de leur mémoire 3D Xpoint !

AMD valide le 14nm LPP de GloFo

GlobalFoundries vient d'annoncer dans un communiqué qu'il avait livré à AMD des puces fonctionnelles gravées avec le process 14nm LPP (Low Power Plus), la version la plus avancée du procédé de fabrication Samsung 14nm FinFet (l'Apple A9 utilisant le 14nm LPE Low Power Early) qui est pour rappel également déployé chez GF.

Le fondeur précise qu'AMD a "taped out" plusieurs produit chez GF en 14nm LPP et qu'il est actuellement en train de valider les échantillons produit. Il semble donc qu'un premier produit ai été validé, GF parlant de "silicon success". AMD indique au passage qu'il compte utiliser le process 14nm LPP sur des produits CPU, APU mais aussi GPU. Jusqu'alors les GPU AMD étaient comme ceux de Nvidia fabriqués par TSMC, mais sachant qu'AMD a toujours des engagements contractuels sur des volumes avec GF qu'il peine à remplir il est logique qu'il favorise ce dernier si le process est à la hauteur. On devrait donc avoir droit en 2016 à une bataille d'architecture entre AMD et Nvidia combinée à une bataille de fondeurs avec d'un côté le 16nm FinFET+ de TSMC et de l'autre le 14nm LPP de Samsung/GlobalFoundries !

GlobalFoundries indique que le 14nm LPP a été qualifié au cours du troisième trimestre pour la production, cette dernière va débuter au cours de ce quatrième trimestre et arrivera à plein débit en 2016, sans plus de précision. Difficile pour le moment de savoir quand les premières puces AMD produites en 14nm LPP seront lancées en 2016, mais il serait étonnant que ce soit avant le second trimestre côté GPU et le dernier trimestre côté CPU. Vivement !

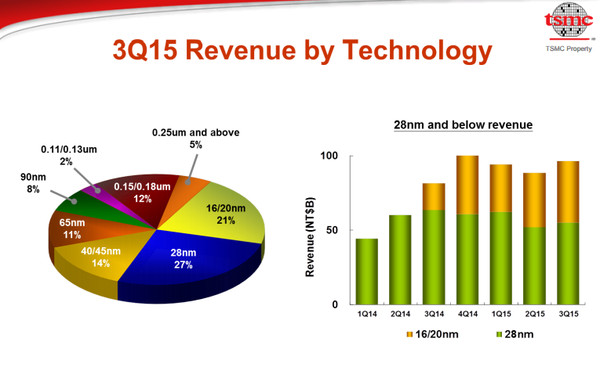

Résultats TSMC, 16 FinFET+ dans l'iPhone 6s

TSMC présentait cette nuit également ses résultats qui, sans trop de surprises, sont bons et au-dessus des estimations. Une des raisons se trouve derrière le fait que TSMC est, contrairement aux spéculations, le fournisseur majoritaire de SoC d'Apple pour l'iPhone 6s. TSMC a également glissé au passage que ces SoC livrés par TSMC étaient bel et bien 16 FinFET+ (la version avancée du process 16nm de TSMC), ce qui explique peut-être l'avantage de consommation en charge lourde que l'on voit dans les versions TSMC des iPhones face aux versions Samsung, comme noté par nos confrères d'Ars Technica .

On aura noté quelques sourires lorsque la question de la différence a été posée clairement à TSMC, le fondeur se contentant de rapporter les propos d'Apple (qui indique 2 à 3% de variations selon les puces en usage normal) et qu'ils étaient « très confiants » sur leur technologie. Dans tous les cas, cela confirme qu'effectivement le 16 FinFET+ de TSMC est déjà prêt, ce qui est une bonne nouvelle pour tous les clients du fondeur !

Par rapport au troisième trimestre 2013 les revenus du fondeur sont en hausse de 1.7%. La marge brute est en baisse cependant, principalement suite à la vente de l'activité solaire du groupe. La société mélange les revenus 16 et 20nm dans ses résultats, les deux nodes représentent 21% des revenus de TSMC. La proportion du 16nm devrait augmenter significativement au quatrième trimestre même si la société n'a pas donné de détails. Au second trimestre, le 20nm, utilisé quasi exclusivement par Apple et Qualcomm représentait 20% des revenus de TSMC.

TSMC s'attend à voir ses revenus progresser sur l'année 2015 de 11%, porté par le marché des smartphones qui globalement profiterait d'une hausse de 10% sur l'année quand tous les autres secteurs sont en baisse. La société se félicite de sa place sur le marché haut de gamme qui, s'il n'évolue pas massivement en volume, contient de plus en plus desilicium TSMC.

L'un des co-CEO de TSMC Mark Liu insiste sur le rôle à venir de TSMC sur le marché du « computing » en général, quelque chose qui fait écho aux propos de Morris Chang, le chairman qui au trimestre dernier voyait TSMC jouer un rôle plus important sur les PC portables et les serveurs, mais aussi l'arrivée de SoC dans de nouveaux marchés qui n'existent pas encore. TSMC a indiqué travailler avec certains de ses partenaires sur les automobiles autonomes, nécessitant beaucoup de silicium pour des puces spécialisées dans les traitements d'images pour simuler la vision.

Sur le 10nm, TSMC dit être en bon chemin sur le développement indiquant que le process apportera un gain de densité de 2.1x par rapport au 16 FinFET+, 20% de performances supplémentaires ou 40% d'économie d'énergie à performances égales. Des chiffres qui ont légèrement évolué, plutôt dans le bon sens par rapport à ce qui était indiqué le trimestre dernier (2.2x, +15% et -35% respectivement). TSMC compte freezer la phase de développement ce trimestre et commencer les phases de qualifications avec des premiers tapeout clients attendus au printemps prochain. Des délais agressifs qui correspondent à ce que la société avait promis jusqu'ici.

Pour le 7nm, TSMC sous-entend que le process profitera de l'apprentissage des yields du 10nm. Nous continuons de penser, même si TSMC ne le dit pas clairement, que le BEOL (la partie interconnexion de la puce) du 10 et du 7nm seront communs à l'image de ce qui s'est passé entre le 20 et le 16nm, même si des gains de densités ont été évoqués (mais non quantifiés !). Le développement est lui aussi « en bonne voie » et devrait apporter des gains substantiels de performances face au 10 même s'ils n'ont pas été précisés non plus. Le 7nm sera en tout cas le prochain node « long » (après le 16 FinFET+) ce qui laisse penser qu'effectivement la situation 20/16 se réitèrera en 10/7. Mark Liu a en prime indiqué avoir déjà produit de la SRAM fonctionnelle en 7nm.

L'autre co-CEO de TSMC, C.C. Wei, a indiqué que la demande sur le 20nm était plus faible qu'attendue, en partie du fait de la disponibilité un peu plus tôt que prévue du 16nm. Le fondeur s'attend tout de même à produire deux fois plus de puces 20nm en 2015 qu'en 2014. Cependant la conversion des usines 20nm en 16nm va continuer, le 20nm étant voué à disparaitre. 100 produits de 40 clients sont attendus en 2016. Sur le packaging type InFO (Intergrated Fan-Out Wafer Level Packaging) le fondeur s'attend à ce qu'il soit disponible en 2016 pour ses clients sur son process 16nm.

Les yields 16 FinFET+ continuent en tout cas de battre tous les records internes d'après le constructeur, confirmant que le choix d'avoir utilisé un BEOL commun, même si cela n'apporte pas un gain de densité massif, permet d'être plus rapidement présent sur le marché avec un process performant.

MAJ : A la toute fin du (long !) webcast, TSMC est revenu sur l'EUV, indiquant que durant ces trois derniers mois, les progrès de l'EUV ont été très bon et qu'à compter de janvier, de nouvelles machines devraient être livrées pour préparer le travail sur le 5nm !

L'A9 d'Apple produit par Samsung et TSMC

La société Chipworks a confirmé via son blog une semi surprise : l'A9, le SoC ARM custom présent dans l'iPhone 6s d'Apple existe en deux variantes, une produite par Samsung et l'autre par TSMC. Selon Chipworks, ils ont trouvé ces deux puces dans « deux modèles identiques », tandis que iFixit a trouvé la version Samsung dans un iPhone 6s et la version TSMC dans le modèle 6s Plus .

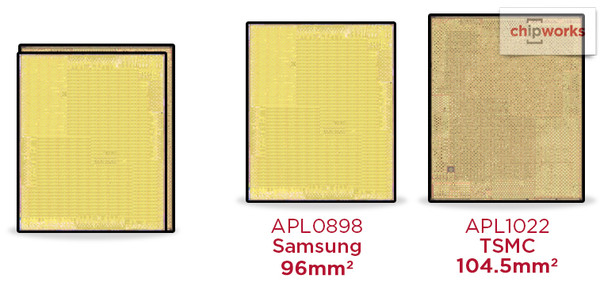

Les deux puces portent une référence différente (APL0898 et APL1022) et mesurent respectivement 96 mm2 et 104.5 mm2 (l'A8 en 20nm mesurait 89mm2 à titre de comparaison). Le nombre de transistor est inconnu, il était de 2 milliards sur l'A8. Le process de Samsung (partagé sous licence avec GlobalFoundries) est un 14nm FinFET tandis que celui de TSMC est un 16nm FinFET même si en pratique les nomenclatures ne veulent plus dire grand-chose. Samsung semble avoir tout de même un avantage de densité, quelque chose que l'on attendait, TSMC avait déjà annoncé dès l'année dernière qu'ils proposeraient une seconde version de leur process 16nm en 2016 (le 16 FinFET Plus) afin d'améliorer la densité et être plus compétitif avec la concurrence.

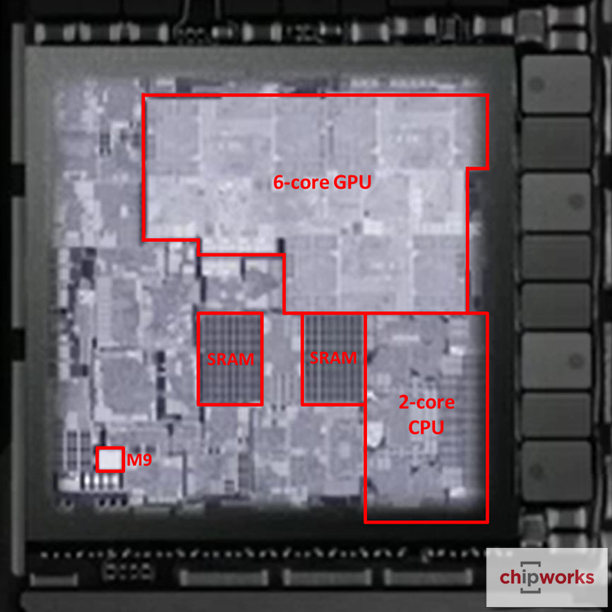

Au-delà de leurs tailles différentes, les puces semblent se comporter de manière similaire dans les premiers benchmarks que l'on a pu croiser, même s'il est encore tôt pour se faire une idée complète. Techniquement l'A9 est un SoC composé pour sa partie CPU d'un dual core basé sur une architecture ARM 64 bit custom et cadencé à 1.8 GHz accompagné de 3 Mo de cache L2. Un GPU issu de chez PowerVR avec « six cores » s'occupe de la partie graphique, le CPU et le GPU partageraient possiblement 8 Mo de cache L3. Apple annonçait +70% de performance CPU et +90% de performances graphiques par rapport à sa génération précédente gravée en 20nm par TSMC, des chiffres qui se vérifient à peu près dans les premiers benchmarks. Le SoC est de type PoP avec 2 Go de mémoire LPDDR4 au-dessus (et l'on notera pour l'anecdote la présence d'un contrôleur NAND PCIe/NVMe dans l'iPhone 6s !)

Si l'on s'attendait à voir Samsung et TSMC produire la nouvelle génération de puces d'Apple, beaucoup pensaient que Samsung aurait récupéré la production de l'A9 et TSMC celle de l'A9X (la version iPad du SoC). En juillet dernier, TSMC avait cependant semé le doute indiquant avoir déjà réalisé ses premières livraisons de puces à ses clients.

Le choix d'utiliser deux process distincts pour produire une même puce est original de la part d'Apple qui n'a toutefois pas les mêmes problèmes que tout le monde. Le volume de l'iPhone (13 millions vendus en un weekend, 200 millions attendus sur l'année) permet à la marque de justifier aisément le cout double de développements séparés pour deux process différents (les process sont incompatibles dans leurs règles et les designs doivent être adaptés pour chaque fondeur).

Cela permet également d'améliorer le volume de disponibilité dès le lancement - un problème particulièrement important sur des process de toute dernière génération, il suffit de regarder la disponibilité anémique des Skylake d'Intel pour s'en convaincre - et de minimiser les problèmes de yields que pourraient avoir l'un ou l'autre de ses fournisseurs.