Les derniers contenus liés aux tags TSMC et GlobalFoundries

Afficher sous forme de : Titre | FluxRésultats AMD pour le troisième trimestre

7nm fin 2018 pour GlobalFoundries ?

Nouvel accord WSA entre AMD/GlobalFoundries

Intel Custom Foundry prend une licence ARM !

AMD valide le 14nm LPP de GloFo

TSMC confiant sur l'EUV en volume pour 2019

Epyc, ThreadRipper, AMD détaille sa roadmap CPU

12nm et EUV à 7nm pour TSMC

ASML investit dans Carl Zeiss SMT pour l'EUV

Samsung annonce de futurs process 14 et 10nm

TSMC confiant sur l'EUV en volume pour 2019

TSMC a également annoncé ses résultats un peu plus tôt dans le mois, l'occasion d'une conférence auprès des analystes qui aura été la dernière de Morris Chang, le Chairman et fondateur de TSMC. Il avait annoncé en fin d'année dernière qu'il prendrait sa retraite en juin 2018.

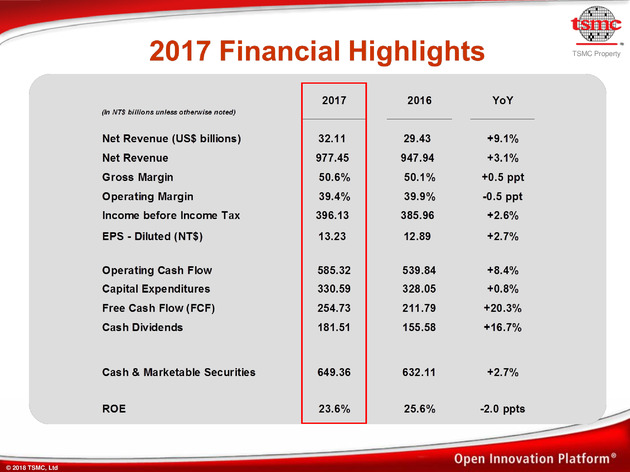

Sur l'année 2017, TSMC a réalisé un chiffre d'affaire de 32.1 milliards de dollars pour un résultat net de 11.2 milliards. Des chiffres qui progressent modestement en apparence par rapport à 2016, +3.1% et +2.6% en New Taiwan Dollar (+9.1% en dollars US, avec les effets du change).

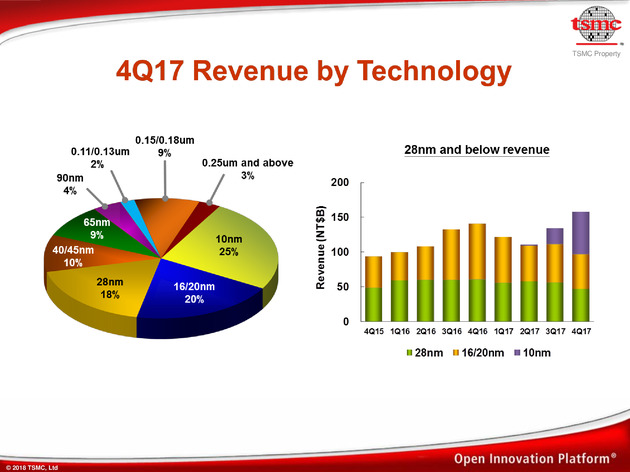

On notera que sur le dernier trimestre, le 10nm (utilisé quasi exclusivement par Apple) représente 25% du chiffre réalisé ce qui est assez massif. Sur 2017, le 10nm aura compté pour 10% du chiffre de TSMC. Les technologies "avancées", à savoir le 28nm et les nodes suivant ont compté pour 58% du chiffre d'affaire engrangé par les ventes de wafers, contre 54% en 2016.

Les futurs process ont été évoqués, le 5nm (qui utilisera l'EUV chez TSMC) est prévu pour une production risque au premier trimestre 2019. TSMC indique avoir déjà atteint de bons yields sur des puces test de SRAM, et le niveau de développement est aussi avancé que pour le 7nm.

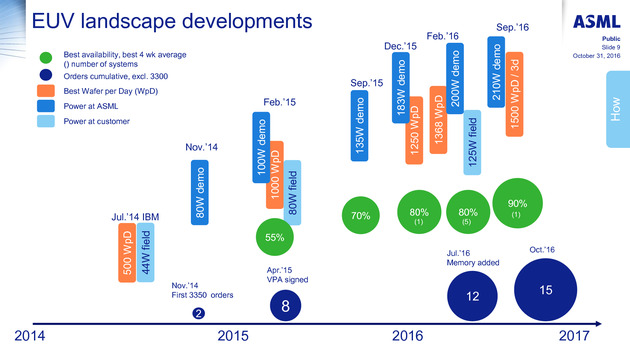

En ce qui concerne l'EUV, TSMC s'est félicité d'avoir obtenu des yields élevés en 7nm+ (la version EUV du 7nm de TSMC qui sera introduite dans un second temps) et 5nm. La question des sources lumineuses semble en passe d'être réglée, TSMC indiquant utiliser actuellement des sources 160 watts (on était à 125W l'année dernière), tandis que les sources 250W (annoncées par ASML l'été dernier) sont installées en voie de production. TSMC dit également être optimiste autour des questions compliquées autour du pelliculage avec des défauts bas. La société s'attend donc à ce que la production en volume du 7nm+ en EUV soit lancée au second trimestre 2019, et en 2020 pour le 5nm.

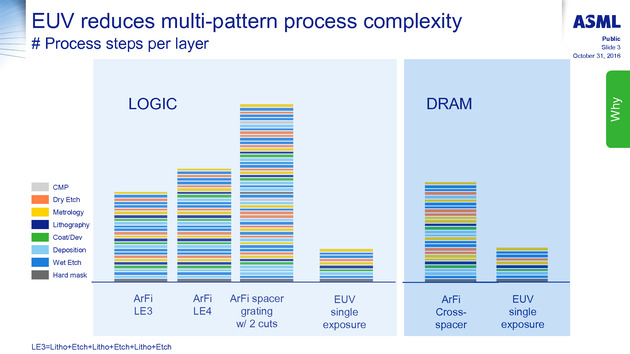

Le 7nm+ est annoncé comme 10% plus performant que le 7nm, et proposera des puces 10% plus petites en moyenne. TSMC n'a pas détaillé les gains directs obtenus en termes de réduction de couches, indiquant simplement un cas ou trois couches immersion peuvent être remplacées par une seule EUV.

Pour l'avenir proche, TSMC a annoncé avoir effectué le tapeout de 10 produits pour le 7nm (avec 10 tapeouts supplémentaires attendus au premier trimestre, et 50 attendus d'ici fin 2018), avec des qualifications en cours qui s'effectuent en parallèle dans deux fabs. Contrairement au 10nm qui n'a été utilisé que par Apple, le 7nm sera utilisé par tous les clients de TSMC. La production en volume commencera en juin et comme toujours, Apple devrait avoir la priorité (quelques produits au compte goutte pourraient être annoncés en 7nm vers la fin de l'année chez les plus petits clients de TSMC, C.C Wei indiquant qu'un décalage entre "smartphone" et HPC de quelques trimestre est attendu).

En 2018 c'est surtout en "12nm" (le 12FFC qui est la quatrième version du 16nm de TSMC) que l'on verra arriver des produits dans le monde du PC. Plus de 120 tapeouts de produits sont encore attendus sur ce node en 2018. A noter que TSMC ouvrira en mai son usine de Nanjing, en Chine, avec un peu d'avance sur son planning suite à une forte demande.

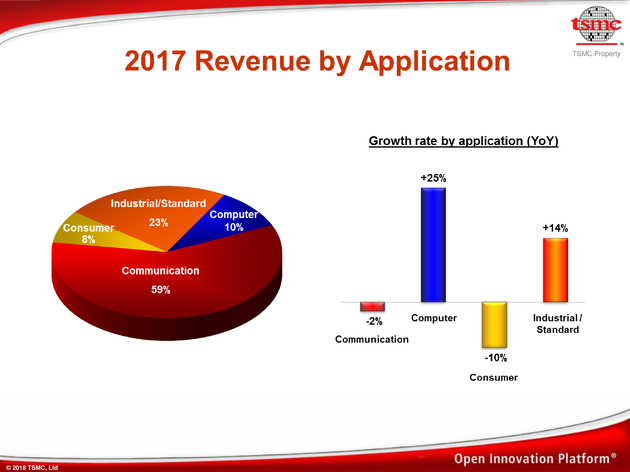

On note qu'en 2018, TSMC s'attend à ce que l'essentiel de sa croissance vienne de sa branche "high performance computing" et pointe particulièrement les GPU (...et les ASIC utilisés pour les crypto-monnaies). Morris Chang aura indiqué s'attendre à une hausse du marché du semi conducteur en 2018 comprise entre 6 et 8%.

La question de l'enquête anti-trust de la commission européenne , poussée par GlobalFoundries aura été vite balayée, TSMC indiquant rejeter les accusations de son concurrent. TSMC continue de se présenter comme la "Foundry de tout le monde" pour contrer l'argument, et tacler au passage Samsung en sous entendant qu'ils ne sont pas en compétition avec leurs clients. On terminera par un mot sur le 3nm, TSMC a indiqué qu'il continuait l'exploration de la technologie et que ces derniers mois, le manager du programme était de plus en plus positif, ne doutant plus de la simple faisabilité comme cela pouvait être le cas l'année dernière.

Epyc, ThreadRipper, AMD détaille sa roadmap CPU

AMD tenait ce soir son "Financial Analyst Day", l'occasion de quelques annonces pour le constructeur.

La première concerne le nom commercial de Naples, la déclinaison serveur de Zen. AMD ne réutilisera pas la marque Opteron, la société opposera donc aux Xeon d'Intel des... Epyc. AMD semble avoir prix goût à la stylisation de ses marques à coup de Y ! Certains y verront par contre une référence - probablement non voulue - à l'Itanium d'Intel ...

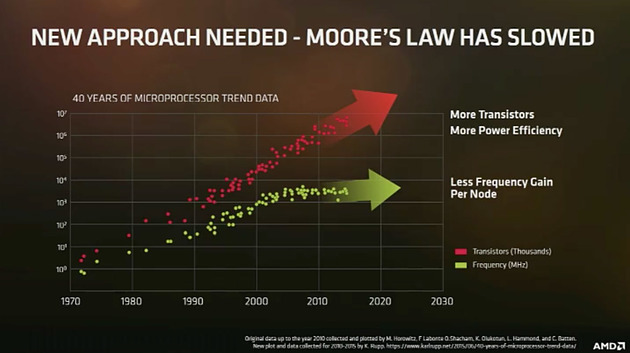

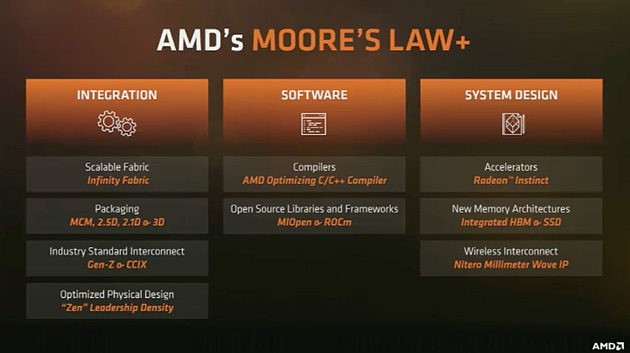

AMD est revenu également sur le ralentissement de la loi de Moore, ou plus exactement le ralentissement des gains apportés par chaque nouveau node. La situation n'est pas nouvelle, ni liée à AMD et ses partenaires fondeurs (Intel a également livré une vision plutôt pessimiste de son 10nm !). AMD reconnaît que les gains de densité et de performances apportés par les nodes vont se réduire, en plus des plafonds de fréquences qui eux ne sont pas nouveaux.

Pour compenser cela AMD met en avant ses initiatives, insistant par exemple son data fabric pour relier des blocs (sur un même die, comme pour Ryzen) ou des dies entre eux (sous le nom Infinity Fabric). Nous admettrons avoir toussé devant le slide ou il était écrit "low latency". Pour le reste AMD mise sur le logiciel, comme sur un nouveau compilateur "optimisé" pour Zen. Baptisé AMD Optimizing C/C++ Compiler (AOCC pour faire court), il s'agit en pratique d'une version "optimisée" de Clang/LLVM 4.0 disponible pour Linux et visant plus spécifiquement la plateforme serveur. Nous n'avons pour le moment pas plus de détails sur les changements effectués par AMD, ni à savoir si ces modifications seront portées dans LLVM (ce qui serait probablement plus utile). La version 1.0 est disponible sur cette page .

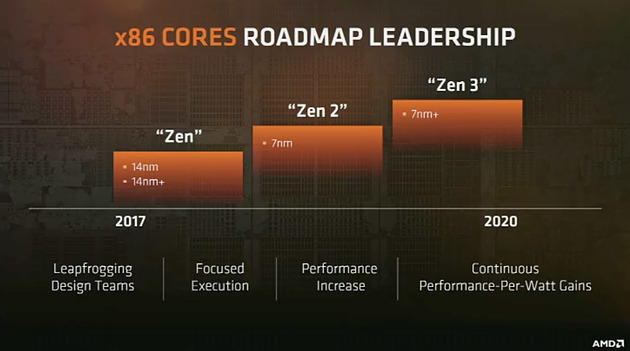

En ce qui concerne la roadmap, AMD ne s'est pas trop avancé avec ce slide assez flou au niveau des dates. On note qu'une version "14nm+" de Zen est prévue ce qui est assez curieux. Officiellement GlobalFoundries propose son 14LPP (Low Power Plus) et bien qu'AMD ne l'ait pas confirmé, on pouvait penser que c'est cette version (et non le 14LPE, E pour Early) qui était utilisée pour Zen étant donné qu'elle l'était déjà pour Polaris. Difficile donc de savoir ce qu'AMD entend par "14+", on pense à une version optimisée du 14LPP à venir (une sorte d'équivalent du 14LPC chez Samsung, même si les deux sociétés ont depuis divergé sur leurs process).

L'autre point à noter est l'absence de 10nm. Là encore ce n'est pas une totale surprise, Global Foundries ne proposera pas de 10nm et si TSMC en proposera un, il sera réservé aux clients gros volume (Apple en particulier). Si AMD reste chez Global Foundries pour Zen2, il faudra attendre fin 2018 si la société tient ses délais. AMD s'est cependant ouvert la possibilité de produire des CPU chez d'autres fondeurs en renégociant le wafer supply agreement qui les lie à Global Foundries. Malheureusement aucune information supplémentaire n'a été donnée sur les timings ou les changements à venir.

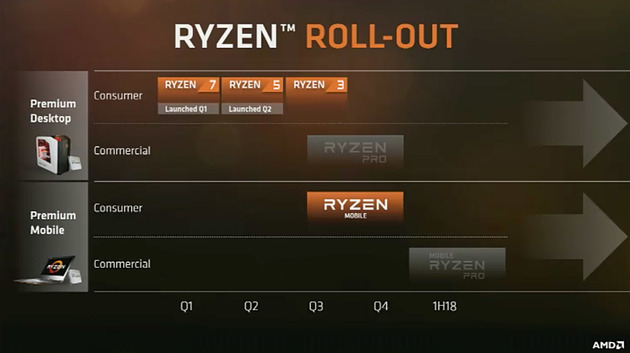

On passera très rapidement sur l'arrivée des versions "Pro" de Ryzen, qui seront simplement des versions destinées à l'entreprise (avec on l'imagine des fonctionnalités manageability comme celles d'Intel) et sur lesquelles aucun détail n'a été donné.

Le constructeur confirme par contre l'arrivée des versions mobiles pour le troisième trimestre. AMD confirme qu'il s'agira bien d'APU basées à la fois sur Zen côté CPU, et sur Vega pour le GPU. Sur le papier l'architecture Zen devrait pouvoir être très compétitive sur ce segment et il sera intéressant de voir si AMD est capable de proposer des produits qui séduiront les OEM.

AMD a enfin confirmé l'existence de Threadripper dont nous vous parlions il y a peu. A l'image d'Intel, AMD utilisera ses puces serveurs pour créer des plateformes desktop haut de gamme. Sur le serveur, AMD proposera avec Naples des puces qui relient quatre dies Zeppelin (le die utilisé pour Ryzen) pour proposer jusqu'a 32 coeurs. Des versions double Zeppelin sont également au programme et c'est celles-ci qui seront utilisées pour la plateforme desktop haut de gamme d'AMD que l'on connaissait sous le nom de code Threadripper. AMD a confirmé le nom de code mais n'en aura pas dit plus. Ces puces utiliseront le monstrueux socket SP3r2 (4094 contacts !). Le lancement interviendra cet été selon AMD et le nom commercial utilisera la marque Ryzen (et non Epyc).

En bref

Cette conférence aux investisseurs, pour la partie CPU, n'a pas été très riche en surprises. AMD est concentré sur le lancement des versions mobiles de Ryzen et est beaucoup moins prolixe sur les évolutions à venir qu'il a pu l'être ces dernières années où communiquer était essentiel pour faire oublier la dette technique accumulée par les FX. On restera curieux d'une éventuelle version de "Zen 1" dans un process 14nm optimisé (que ce soit sous la forme de nouveaux SKU, ou plus simplement pour les APU), même si les gros changements n'interviendront pas avant le 7nm qui, chez Global Foundries, n'est prévu que fin 2018.

La confirmation de ThreadRipper reste une annonce qui embarrassera, au moins sur le papier, son concurrent qui ne pourra plus se vanter du titre - certes un peu futile - du plus grand nombre de coeurs dans un CPU desktop. On retiendra au final surtout la confirmation de l'utilisation de l'architecture graphique Vega sur les APU qui pourrait permettre à AMD, pour le coup, de proposer des produits réellement embarrassants pour son concurrent dont les iGP restent assez modestes, particulièrement depuis qu'Intel semble abandonner ses versions les plus haut de gamme, les GT4e.

12nm et EUV à 7nm pour TSMC

TSMC a publié hier ses résultats financiers pour le dernier trimestre 2016. Le fondeur taiwannais a annoncé pour ce trimestre un revenu brut de près de 7.8 milliards d'euros, en hausse de 28.8% par rapport à la même période sur l'année précédente. Sur la totalité de l'année 2016, TSMC aura augmenté son revenu de 12.4% par rapport à 2015.

Pour 2017, TSMC s'attend à voir ses revenus progresser de "seulement" 5 à 10% (ce qui n'a pas manqué de décevoir les analystes financiers). Lors de la présentation des résultats, quelques informations supplémentaires ont été données.

Morris Chang, Chairman de TSMC s'est lancé dans quelques prédictions pour le marché 2017, s'attendant à voir le marché des smartphones grimper de 6% en unités, et celui du PC se contracter de 5% en unités également (il envisage également un déclin de 7% sur les tablettes tout en voyant le marché Internet of Things progresser de 34%).

Sur le 16/14nm, Morris Chang estime que la part de marché de TSMC est entre 65 et 70%, en dessous de ses attentes (TSMC dispose encore de 80% du marché sur le 28nm par exemple). Toujours poétique, le Chairman voit dans le 10 et le 7nm un "ciel bleu" par rapport à la compétition.

Quelques détails plus techniques ont été donnés, notamment par rapport à un "12nm" qui avait été évoqué ici ou là dans la presse. En pratique, TSMC travaille sur une nouvelle version de son process 16nm (une quatrième après les 16FF, 16FF+ et 16FFC) qui incorpore des améliorations importantes de densité. L'appellation commerciale exacte n'a pas été donnée, et on ne sait pas exactement quand elle sera disponible. On s'attendra dans quelques semaines à une annonce officielle, même si TSMC à confirmé aujourd'hui l'existence de ce "12nm".

Pour le 10nm, si le début de production est bien en cours, le gros du volume se situera sur la seconde partie de l'année (coïncidant avec le lancement des prochains iPhones dont le SoC utilisera le 10nm TSMC).

Sur le 7nm, plus de 20 sociétés travailleraient déjà sur des designs pour l'année prochaine, un chiffre qui devrait doubler dans l'année. Sur la question du 7nm en lui même, nous nous étions interrogés sur la manière dont le constructeur augmenterait la densité. Pour rappel, TSMC s'engage à lancer la production du 7nm dès la fin de l'année, il s'agira du node qu'utiliseront la majorité de ses clients, le 10nm devrait avoir une durée de vie courte et être réservé à quelques gros clients.

Le 10nm rappelle d'une certaine manière le 20nm de TSMC, lui aussi utilisé par des gros clients uniquement avant un passage rapide au 16nm. Cependant, avec une augmentation de la densité de 1.63x entre le 10 et le 7nm, la recette utilisée est plus complexe que pour le passage 20/16nm (qui ne proposait qu'une augmentation de densité de 1.15x). Nos confrères de SemiWiki, très au fait des détails, ont confirmé il y a quelques jours que des changements sur les tailles minimales des cellules sont en grande partie à l'origine des gains de densité et que pour réduire les coûts, TSMC évitera au maximum de généraliser le quadruple patterning (SAQP). Le 10 et le 7nm auront donc bel et bien des similarités techniques.

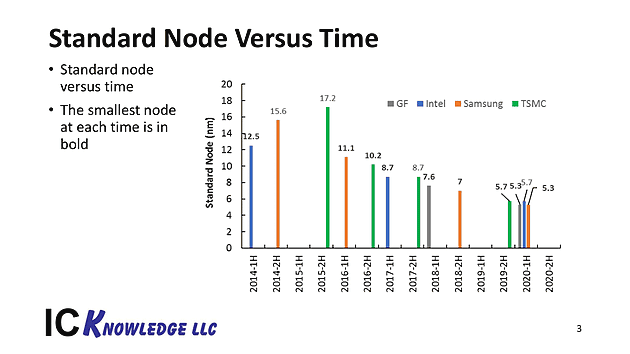

Pour essayer d'y voir un peu plus clair, et étant donné que plus aucun constructeur ne suit de règles équivalentes pour parler de densité, SemiWiki a publié ce graphique intéressant qui montre une "estimation" de la densité comparée de tous les fondeurs :

D'après SemiWiki, le 10nm d'Intel et le 7nm de TSMC auraient, après ajustement, une densité comparable. Il s'agit bien entendu d'estimations qui valent ce qu'elles valent, vous pouvez retrouver l'explication de la formule utilisée ici , mais elles donnent un bon ordre d'idée de ce à quoi il faut s'attendre (un seul bémol à cette analyse : les prévisions concernant GlobalFoundries nous semblent excessivement optimistes, en grande partie à cause des annonces de GlobalFoundries qui nous paraissent déconnectées de leur capacité d'exécution ces dernières années).

En pratique le 10nm de TSMC disposera tout de même d'une meilleure densité que l'actuel 14nm d'Intel, TSMC pourra donc se targuer d'avoir dépassé Intel côté process lorsque les premiers produits 10nm seront disponibles plus tard dans l'année. Et si Intel reprendra l'avantage avec "son" 10nm, TSMC sera effectivement - et pour la première fois - à parité dès la fin de l'année en lançant la production de son 7nm. Une situation qui durera un moment, et pour la première fois les constructeurs "fabless" pourront disposer d'un process équivalent en densité à celui d'Intel.

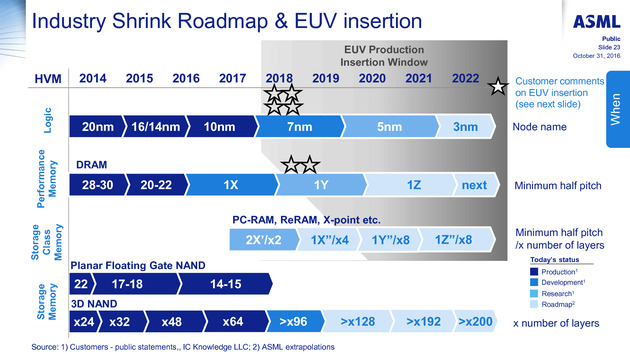

On notera enfin, concernant le 7nm, que TSMC a confirmé qu'ils inséreront l'EUV au bout d'un an de production à 7nm (soit fin 2018) pour créer une nouvelle version du 7nm (à l'image des multiples 16nm). Des propos plutôt optimistes concernant la lithographie EUV qui sera, Mark Liu le rappelle, indispensable à 5nm. Et un timing qui coïncide exactement avec le lancement de la production du 7nm de Samsung qui utilisera elle, dès le début, l'EUV !

ASML investit dans Carl Zeiss SMT pour l'EUV

ASML a annoncé hier qu'il comptait s'offrir un quart de Carl Zeiss SMT (24.9%) pour un montant de près de un milliard d'euros. Zeiss SMT est la filiale "Semiconductor Manufacturing Technology" du groupe allemand Zeiss spécialisé dans l'optique.

ASML indique dans son communiqué qu'il s'agit de renforcer la collaboration entre les deux sociétés, Zeiss SMT fournissant les systèmes optiques utilisés notamment dans les machines de lithographie EUV.

ASML investira en prime 220 millions d'euros dans le centre de recherche et développement de Zeiss SMT, et financera 540 millions d'investissements sur les 6 prochaines années.

L'enjeu de l'investissement, selon ASML, concerne les futures générations d'EUV avec la possibilité d'étendre la durée de vie de la technologie. Car si certains fabricants de semiconducteurs comme Samsung disent désormais (enfin !) qu'ils utiliseront l'EUV à 7nm, les très nombreux retards de la technologie font qu'elle court le risque de voir sa fenêtre d'utilisation réduite, au risque d'être remplacée par d'autres technologies.

Des systèmes optiques plus complexes avec une ouverture numérique de 0.5 (contre 0.33 pour les premières générations d'EUV) est ce que vise ASML dans cet investissement, qui ne devrait porter ses fruits que d'ici 2024. Il permettrait cependant d'étendre la durée de vie de l'EUV sous les 5nm et pour "plusieurs générations". On sait - en parallèle - qu'autour de 5nm, on atteindra les limites du silicium et l'utilisation d'autres matériaux deviendra nécessaire.

L'intérêt de la lithographie EUV est pour rappel de remplacer la source lumineuse utilisée actuellement par les scanners (elle est générée par des lasers à exciplexe Argon/Fluor avec une longueur d'onde de 193nm) par une source dont la longueur d'onde n'est que de 13.5nm, améliorant fortement les possibilités et réduisant le nombre d'étapes nécessaires pour arriver a fabriquer les puces en évitant la généralisation du multi-patterning.

ASML aurait réitéré à nos confrères d'EEtimes que quatre fabricants de puces, et deux fabricants de mémoires, se sont engagés à faire entrer l'EUV en production en 2018, quelque chose que la firme avait également indiqué dans une présentation aux investisseurs (qui évoquait 2018/2019). Une affirmation qui nous parait bien optimiste !

Aujourd'hui, seuls Samsung et GlobalFoundries se sont engagés publiquement à 7nm, pour des dates qui coïncident. En ce qui concerne TSMC, il faudra attendre le 5nm pour le voir arriver de manière extensive, sa production risque est prévue pour 2019 uniquement. Intel avait annoncé de son côté qu'il n'utiliserait pas l'EUV à 10nm, et qu'au mieux l'EUV était "une option" pour le 7nm. Le 7nm d'Intel utilisera une solution de lithographie a immersion classique. Et côté dates, 2019 semble extrêmement optimiste considérant l'exécution d'Intel ces dernières années (retards massifs sur le 14nm, introduction de Kaby Lake pour retarder le 10nm, lancement du 10nm repoussé à fin 2017 et uniquement sur des références mobiles, sans parler de l'introduction dans la roadmap de Coffee Lake en 2018... et en 14nm !).

En ce qui concerne les fabricants mémoire, Samsung avait évoqué la possibilité sans pour autant s'engager fermement. SK Hynix évoquait l'utilisation de l'EUV vers 2019.

Les machines qui seront utilisées en production, les NXE:3400B, atteindraient d'après ASML un débit de 125 wafers/heure, un progrès notable par rapport à mars 2015 ou ASML se félicitait de 42 wafers/heure (entre 50 et 100 wafers/heure étaient considérés comme le minimum pour éventuellement utiliser la technologie d'après Mark Bohr d'Intel). Pour arriver à ce chiffre, ASML devra augmenter fortement la puissance de la source lumineuse. Le constructeur aurait livré des sources 125W à ses clients cette année qui ont permis d'atteindre 85 wafers/heure.

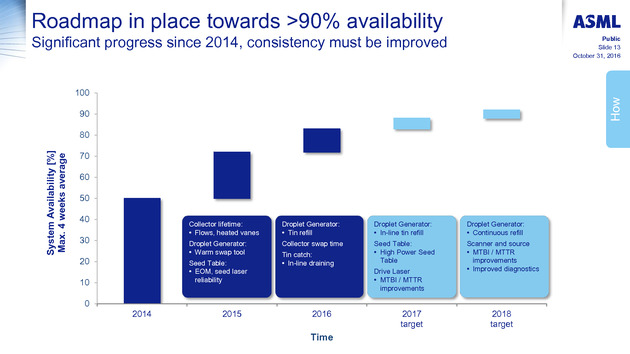

La question de la disponibilité des machines semble également être meilleure, de seulement 55% à l'époque, ASML atteint aujourd'hui entre 70 et 80%, avec l'objectif d'être a 90% en 2018.

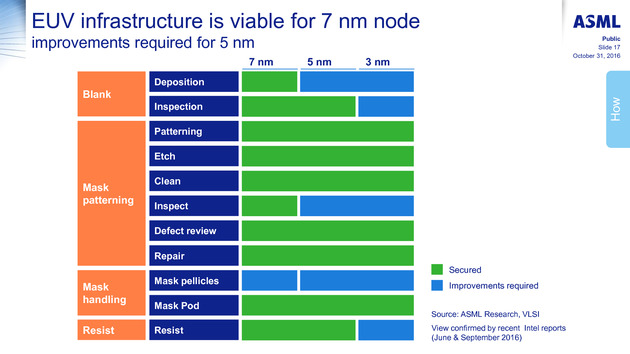

L'enthousiasme d'ASML - le seul à se lancer dans l'EUV - est forcément élevé pour sa technologie mais il faut une fois de plus rappeler que les scanners ne sont qu'une partie de la chaîne de fabrication. Les progrès réalisés, bien qu'importants, ne veulent pas dire que l'EUV est "prêt", loin de là.

La question des masques (la plaque transparente qui contient l'image de la puce à graver) et de l'inspection de leurs éventuels défauts n'a pas encore été résolue. Et si là aussi ASML tente d'apporter sa propre réponse, en pratique le problème reste complexe a solutionner avec des conséquences massives sur la viabilité de la technologie en production (plus de détails dans cet excellent article ).

Samsung annonce de futurs process 14 et 10nm

Samsung vient d'indiquer par un communiqué de presse qu'il proposera une quatrième version de son process 14nm. Baptisée 14PLU, elle fait suite au 14LPE (Low Power Early, la première version dispo lorsque les yields étaient faibles), 14LPP (Low Power Plus, version un peu plus optimisée lorsque les yields étaient stabilisés), 14LPC (possiblement Low Power Compact, la version réduit les couts et fait écho au 16FFC de TSMC, tout en ajoutant la possibilité de pouvoir fabriquer des radios, indispensable pour la fabrication de modems par exemple).

Samsung vient d'indiquer par un communiqué de presse qu'il proposera une quatrième version de son process 14nm. Baptisée 14PLU, elle fait suite au 14LPE (Low Power Early, la première version dispo lorsque les yields étaient faibles), 14LPP (Low Power Plus, version un peu plus optimisée lorsque les yields étaient stabilisés), 14LPC (possiblement Low Power Compact, la version réduit les couts et fait écho au 16FFC de TSMC, tout en ajoutant la possibilité de pouvoir fabriquer des radios, indispensable pour la fabrication de modems par exemple).

Comme souvent, ces "variantes" de process sont des itérations autour d'une même technologie. Elles sont l'occasion d'annoncer des gains obtenus par l'optimisation de l'exploitation des process. Dans le cas de la version U, Samsung annonce des performances "plus élevées" à consommation égale, avec des règles de design identiques à son process 14LPC. Pour Samsung, le 14LPU est adapté aux utilisations "hautes performances" qui requièrent "beaucoup de calculs".

Un appel du pied à peine voilé aux fabricants de GPU et de SoC haut de gamme. Si Samsung a réussi a obtenir la fabrication de quelques GPU Nvidia (notamment les GP107 des GTX 1050), il s'agit de puces plus petites avec des niveaux de performances moindres par rapport au haut de gamme, qui reste toujours fabriqué chez TSMC. De la même manière, si AMD a fabriqué Polaris chez GlobalFoundries (sur un process techniquement identique à celui utilisé par Samsung, GlobalFoundries utilisant le process de Samsung sous licence), il ne s'agit pas non plus du haut de gamme (les raisons d'AMD étant beaucoup plus complexes).

La compétition avec TSMC est excessivement rude pour Samsung, qui tente avec cette quatrième version de s'attirer de nouveaux marchés. Le dernier "gros coup" du fondeur avait été la co-fabrication des SoC A9 d'Apple, un marché obtenu grâce au retard annoncé de TSMC. Un retard comblé en dernière minute par le fondeur Taiwanais. Les comparaisons directes sont toujours à double tranchant, et si Samsung avait bel et bien un avantage de densité sur son concurrent, sur le plan des performances TSMC restait, malgré la précipitation, en tête.

Cette version 14LPU tentera de combler ce déficit d'image même si selon toutes vraisemblances, TSMC gardera une main mise sur le haut de gamme sur ce node.

En parallèle, Samsung annonce également un 10LPU, qui sera cette fois la troisième version du 10nm de Samsung. Contrairement au 14LPU, le 10LPU augmentera la densité par rapport aux 10LPE/LPP, et Samsung le présente comme le 10nm proposant le cout le plus faible "de l'industrie". Le nom de 10LPC aurait probablement été plus adapté pour décrire ce process mais peu importe !

Dans les deux cas, il s'agit d'annonces puisque les kits de développement (PDK) pour le 14LPU et le 10LPU ne seront disponibles qu'au second trimestre 2017 ! On ne s'attendra donc pas a voir des produits les exploiter rapidement, le 10LPP entrera en production en volume pour rappel mi-2017.

On notera enfin que Samsung confirme une fois de plus sa volonté d'utiliser la lithographie EUV à 7nm, pour au moins une partie des couches de la puce. On rappellera que le 7nm de Samsung devrait arriver plus tard que le celui de son concurrent, la société ayant sous entendu à plusieurs reprises ces dernières semaines que le 10nm aurait une durée de vie plus longue qu'annoncée par certains.

TSMC tente en effet de lancer la production 7nm volume avec un an de décalage par rapport au 10nm (soit respectivement Q4 2016 pour le 10nm, et Q4 2017 pour le 7nm). Un rythme infernal qui ne sera suivi par personne d'autre (et largement financé, faut-il le rappeler, par Apple), mais sur lequel TSMC semble extrêmement confiant.