Les contenus liés au tag Micron

Afficher sous forme de : Titre | FluxMicron et Elpida, c'est fait

Micron annonce sa MLC 16nm

Hynix signe un accord de licence avec Rambus

Computex: La DDR4 gagne 4 pins et de la Flash

Des pertes pour Micron, malgré la hausse côté DRAM

ReRAM rapide chez Micron et Sony

Micron et Sony ont profité de l'ISSCC pour annoncer avoir produit un prototype de ReRAM (Resistive RAM) qui sur le papier semble particulièrement intéressant. Pour rappel, la ReRAM est un nouveau type de mémoire non-volatile, basée sur le Memristor d'Hewlett Packard qui permet en théorie de faire le lien en terme de coûts et de performances entre la mémoire classique (DRAM) et celle utilisée dans les SSD (NAND).

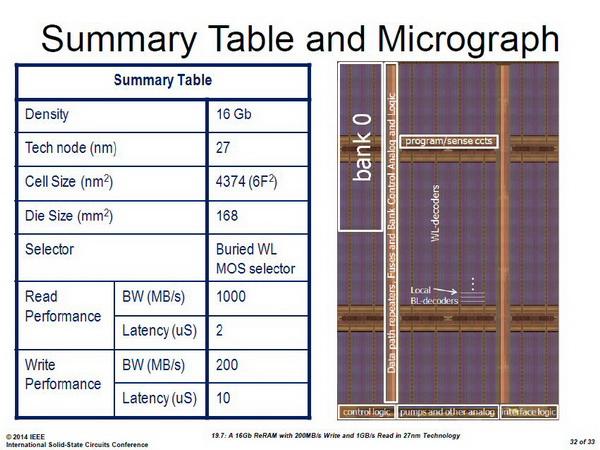

Côté caractéristiques, la puce de Micron/Sony est assez alléchante sur le papier. Fabriquée en 27nm, cette puce utilise une surface de 168mm2 et propose 16 Gbit de stockage - parmi les plus grosses annoncées jusqu'ici (Sandisk et Toshiba avaient annoncé l'année dernière une puce 32 Gbit). C'est en prime l'une des plus rapides avec des taux de transferts de 1 Go/s en lecture et 200 Mo/s en écriture et des latences très basses (2 et 10 microseconde).

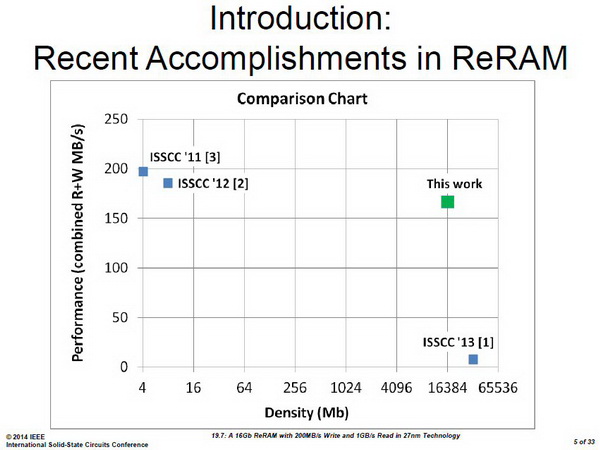

Produire des puces ReRAM qui soient à la fois de large capacité et rapides était jusqu'ici un challenge, la plupart des puces rapides présentées jusqu'ici ayant une densité en Mbit plutôt qu'en Gbit. Micron et Sony n'ont pas donné de détails sur l'éventuelle arrivée de ces puces sur le marché, qui pourraient par exemple trouver leur place dans un premier temps comme cache dans un SSD pour améliorer les performances.

Micron abdique contre Rambus

Après Nvidia l'année dernière et SK Hynix en juin c'est aujourd'hui au tour de Micron d'abdiquer dans la guerre des brevets qui opposait la majeure partie de l'industrie à Rambus.

Pour rappel, ce feuilleton juridique avait démarré en 1991 lors des meetings du JEDEC (le comité de standardisation des formats de mémoire) autour du futur standard SDRAM. Entre 1991 et 1995, Rambus avait pris part au développement de la SDRAM et avait transmis les informations techniques du format en discussion à son département légal afin qu'il « solidifie et étende » les brevets de Rambus pour couvrir le standard SDRAM (une pratique interdite par les status du JEDEC qui réclamait que tous les brevets soient annoncés et proposés via une licence type FRAND Fair, Reasonable And Non Discriminatory, en français des termes raisonnables et non discriminatoires, c'est-à-dire semblables pour tous les acteurs).

Rambus avait alors claqué la porte du JEDEC en 1996 après avoir signé un accord avec Intel pour l'utilisation de la RDRAM, tout en préparant « un champ de mine de brevets » pour empêcher toute traction autour du standard SDRAM. Le début d'une longue bataille qui se termine finalement aujourd'hui. Si vous souhaitez plus de détails historiques sur ce sujet, nous vous conseillons vivement la lecture (PDF a partir de la page 3, en anglais) de ce verdict qui continent un rappel des faits très bien documenté et très complet.

Malgré de multiples invalidations de brevets , pertes de procès anti trust et encore d'autres invalidations de brevets pour destruction de preuves (voir le PDF au-dessus), la plupart des acteurs ont tout de même signé un accord à minima - avec Rambus.

Dans le cas de SK Hynix et Micron (les termes de l'accord de Nvidia ne sont pas connus) il s'agit d'accords bien loin de ce que pouvait réclamer jusqu'ici Rambus puisqu'aucun dommage n'est versé pour d'éventuelles violations de brevets durant les années passées, les deux sociétés ont simplement négocié un accord de licence : 12 millions de dollars par trimestre pour Hynix sur cinq années et aujourd'hui une licence flottante pour Micron ne pouvant pas dépasser 10 millions de dollars par trimestre pour une durée de 7 ans et qui inclut à son terme une licence perpétuelle sur « certains produits » non précisés. Des sommes certes non-négligeables, mais bien loin des 3.95 milliards de pertes évalués par Rambus lors de sa tentative perdue de procès anti trust contre Micron et Hynix.

A titre de rappel, Micron avait annoncé un chiffre d'affaire de 2.84 milliards de dollars sur le troisième trimestre de cette année. De quoi rendre négligeable le cout de la licence cédée à Rambus, même si Micron perd ce qui était ici une bataille de principes.

Un résultat record pour Micron ''grâce'' à Elpida

Micron vient d'annoncer ses chiffres pour son trimestre fiscal qui prenait fin le 29 août dernier. Le fabricant de mémoire annonce des ventes à hauteur de 2,84 milliards de $ et une marge brute de 24,6%, contre 1,96 milliards et 11,1% sur la même période il y a un an. Il faut noter que durant un mois sur ce dernier trimestre les revenus d'Elpida sont ajoutés du fait de la finalisation de l'acquisition, ce qui a rajouté 355 millions de $ de chiffre d'affaires à 25% de marge brute.

Micron enregistre au passage un gain lié à l'acquisition de pas moins de 1,484 milliards $ en valorisant les actifs d'Elpida à 2,433 milliards de $ pour un coût d'acquisition de 949 millions. Une très bonne affaire qui permet au final à Micron d'afficher un résultat net de 1,7 milliards sur le trimestre.

Concernant la marge opérationnelle, l'amélioration découle notamment de la hausse du prix de la DRAM, qui avait permis à Micron de repasser dans le vert dès le trimestre précédent. La marge serait actuellement de 25% environ sur ce marché, contre 5 à 10% sur la NOR et 30 à 35% sur la NAND. Le prix de vente moyen de la DRAM a augmenté de 5% comparé au trimestre précédent, alors que celui de la NAND a baissé de 9%.

La soudaine hausse des prix suite à l'incendie de l'usine SK Hynix située à Wuxi devrait permettre à Micron de tirer son épingle du jeu, et Micron sans s'en féliciter officiellement indique ne pas avoir modifié son volume de DRAM en conséquence ce qui aidera malheureusement au maintien des prix élevés tant que l'usine de SK Hynix ne retrouvera pas son niveau de production. La transition d'une usine singapourienne de la DRAM vers la NAND n'est d'ailleurs pas retardée...

Toujours concernant la DRAM, Micron sous-entends clairement qu'il sera le ou tout du moins l'un des fournisseurs de GDDR5 pour la PlayStation 4.

Pour ce qui est de la NAND, qui représente 27% des ventes de Micron, la baisse de prix n'a pas impacté la marge brute qui reste stable. Plus de 50% du volume de NAND de Micron est utilisé dans ses propres SSD ou des SSD de partenaires clefs, et le fabricant précise que ses SSD "clients" sont à 40% en 20nm alors que les SSD entreprise sont à plus de 80% en 25nm.

1ers échantillons d'Hybrid Memory Cube !

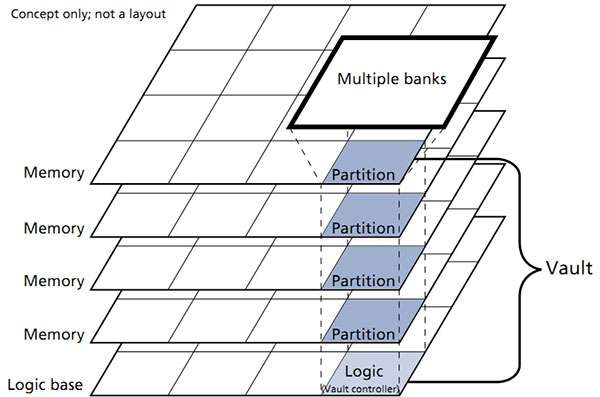

Micron vient d'annoncer par un communiqué de presse la disponibilité de ses tous premiers échantillons de test d'Hybrid Memory Cube. Pour rappel, l'Hybrid Memory Cube est un concept relativement simple qui superpose plusieurs dies de mémoire DRAM qui sont reliés les uns aux autres par des TSV (des fils qui passent au travers des différents dies), et reliés en dessous à une couche logique qui contient les contrôleurs.

Un consortium qui regroupe Micron et d'autres sociétés (notamment ARM, HP, Hynix, IBM et Samsung, mais bizarrement pas Intel qui pourtant avait effectué des démonstrations de la technologie) a publié une spécification pour ce nouveau type de mémoire en avril, annonçant des débits très élevés allant de 160 à 240 Go/s (et même 320 Go/s pour des modèles plus complexes). Vous pouvez retrouver plus de détails sur le fonctionnement de l'HMC dans cette actualité.

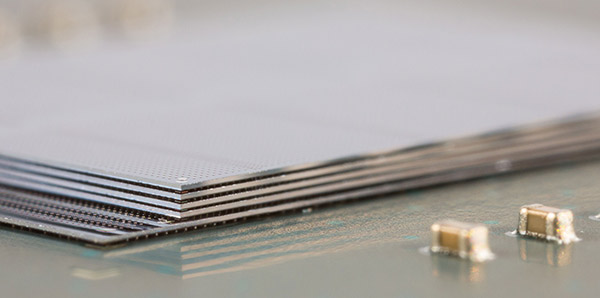

Micron fournit pour l'occasion cette magnifique photo ou l'on voit clairement le concept

Micron avait annoncé il y a peu son intention de lancer la production en 2014 et de livrer avant la fin de l'année ses premiers échantillons. C'est donc chose faite et l'on a droit en prime à quelques détails techniques. Ce premier échantillon est un modèle 2 Go composé de quatre dies de mémoire DRAM de 4 Gb. Avec quatre liens, cette puce offre 160 Go/s de bande passante mémoire comme attendu. Ces premiers échantillons permettront avant tout le développement pour les partenaires, l'HMC déportant une grande partie de la logique des contrôleurs mémoires directement dans sa couche logique. Micron annonce qu'il proposera début 2014 des échantillons 4 Go et que les deux modèles seront bel et bien en production en 2014, sans s'avancer plus précisément. Les curieux pourront retrouver ces modèles, annoncés en packaging BGA et FBGA sur cette page du site de la société.

L'Hybrid Memory Cube en production en 2014

Nous vous avions parlé en 2011 du concept de l'Hybrid Memory Cube. Sur le papier il s'agit d'un concept simple, superposer une couche logique de contrôleurs mémoires avec de multiples dies de mémoire DRAM reliés les uns aux autres par des TSV (Through Silicon Vias, littéralement des fils qui passent au travers des différents dies, à l'opposée de la solution "classique" ou l'on fait passer les fils par le côté).

Chaque colonne sur le schéma représente un "vault" qui dispose en bas dans la couche logique de son propre contrôleur mémoire indépendant. L'avantage du système est d'être capable d'atteindre des bandes passantes très élevées, on parlait déjà en 2011 de 128 Go/s sur une seule puce !

Sur cet autre schéma, on peut voir le principe un peu plus en détail avec une puce qui superpose neuf dies (8 mémoires, un logique). On retrouve ici 16 vaults, chaque contrôleur est relié à un switch puis à quatre liens point à point vers l'extérieur de la puce. Ces nombres étant bien entendu modulables. Notez également que les cubes sont chainables entre eux.

Micron et d'autres sociétés (notamment ARM, HP, Hynix, IBM et Samsung) se sont alliés pour mettre en place un consortium dans le but de développer un standard commun. On notera avec un étonnement certain l'absence d'Intel dans ce consortium, alors que la société avait pourtant effectué les démonstrations lors de l'IDF 2011. La spécification (PDF) a été publiée en avril avec des débits très prometteurs allant de 160 à 240 Go/s pour les modèles à quatre liens (en fonction de la vitesse individuelle des liens), et 320 Go/s pour le modèle huit liens.

Micron avait indiqué en 2011 que c'est IBM qui produirait dans son process 32nm HKMG. Aujourd'hui, dans un communiqué qui parle de l'intérêt de l'intégration avec des FPGA, Micron s'engage un peu plus sur les dates en annonçant la livraison d'échantillons avant la fin de l'année, et surtout une production en volume pour 2014. On ne sait pas s'il s'agira toujours d'un process 32 HKMG. En déportant les contrôleurs mémoires directement dans les puces mémoires, l'Hybrid Memory Cube propose en plus d'un bond net de bande passante la possibilité de repenser les sous systèmes mémoires des processeurs. Reste à voir dans quel cadre elle pourra être utilisée. Le consortium indique viser très clairement les CPU et les GPU. Auprès de ces puces, l'HMC jouerait alors un rôle hybride à mi chemin entre ce que propose l'eDRAM et la mémoire traditionnelle.