Les derniers contenus liés aux tags Micron et 3D XPoint

La 3D NAND arrive chez Micron, MX300 en vue ?

Du retard et de la PRAM pour 3D XPoint

IDF: Roadmap mémoire Micron

Intel et Micron annoncent la ReRAM 3D XPoint

Les premiers portables avec Optane au CES

Des détails sur le 7nm à l'ISSCC 2017

HMC, DDR5 et 3D XPoint pour Micron

V-NAND Gen4 et Z-NAND pour Samsung

PRAM 3D XPoint QuantX pour Micron

Les premiers portables avec Optane au CES

Lenovo a présenté un peu en avance sur son blog les prochains modèles de PC portables qu'ils introduiront au CES.

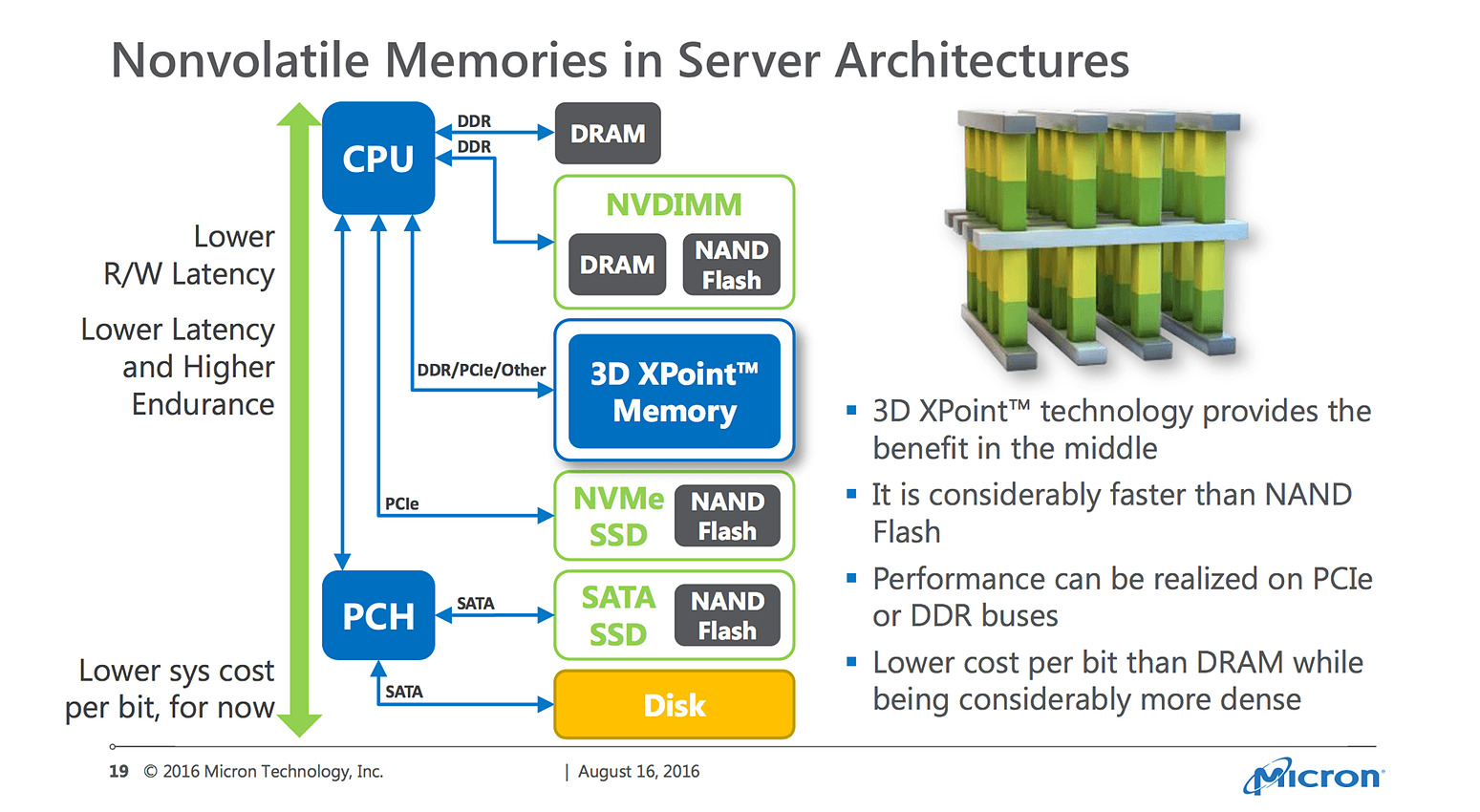

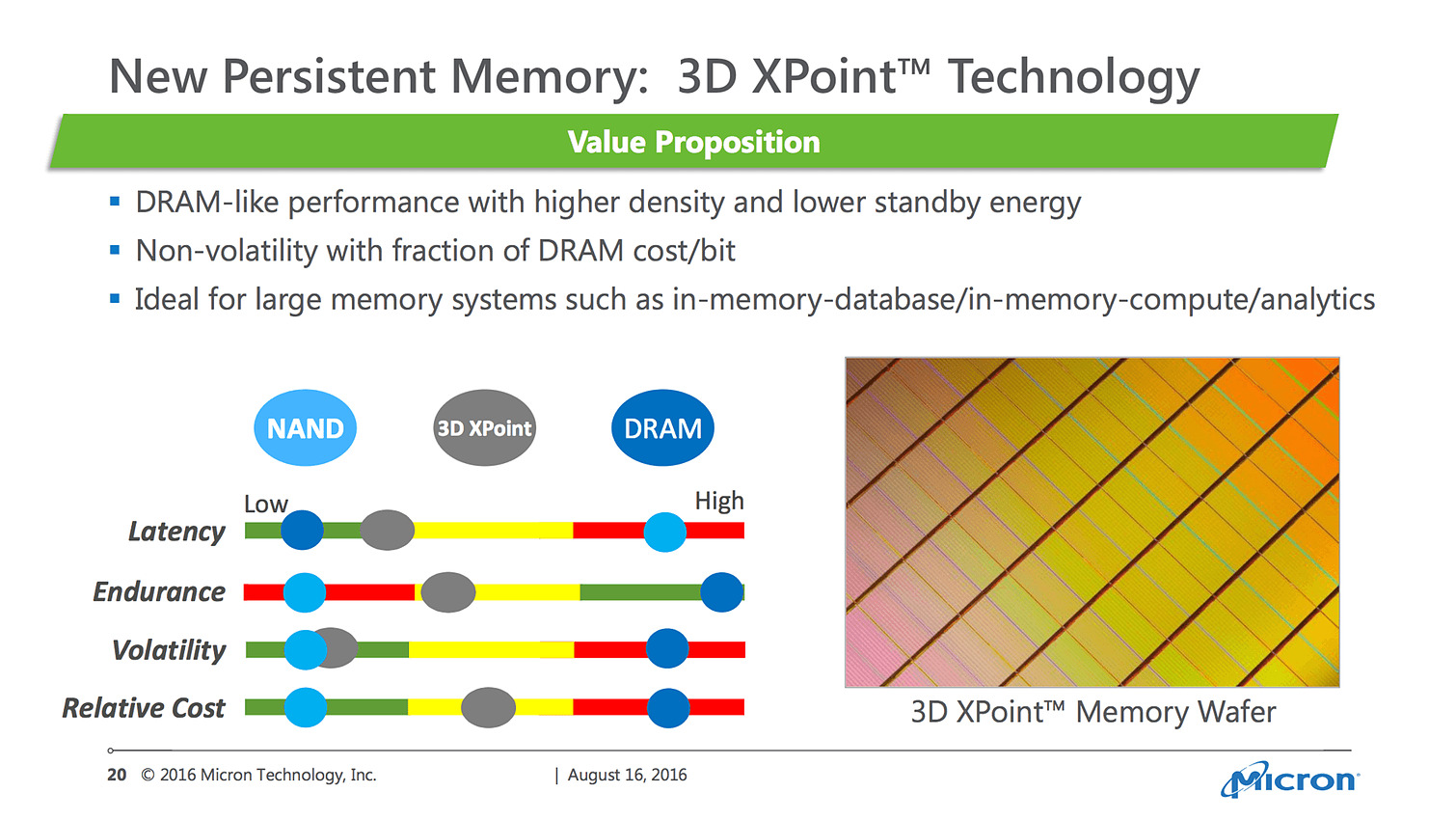

Ce qui retient notre attention est la présence du support de la technologie Optane d'Intel. Pour rappel, Intel avait présenté un nouveau type de mémoire sous le nom 3D Xpoint, s'intercalant entre la mémoire RAM (peu dense mais très rapide) et la NAND (très dense, moins rapide).

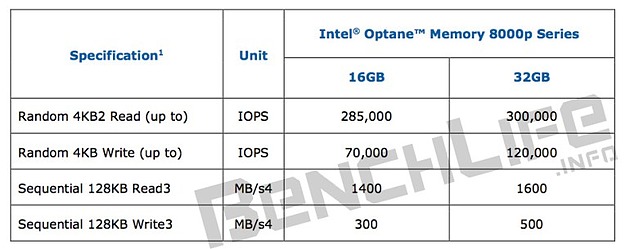

Le premier produit qui utilisera cette nouvelle mémoire est un accélérateur connu sous le nom de code Stony Beach et qui sera commercialisé comme Optane 8000p. Ces accélérateurs système se présentent sous la forme de cartes au format M.2 et Intel devrait lancer deux versions, en 16 et 32 Go. Lenovo indique qu'il proposera le modèle 16 Go sur certains de ses portables haut de gamme, en M.2 2241 (4.1 cm de long).

La manière exacte dont "l'accélération" sera effectuée reste assez floue aujourd'hui, une piste probable étant le mode SRT (Smart Response Technology) des pilotes disques RST d'Intel. Dans ce cas l'accélérateur servira de cache pour les disques systèmes. Si Intel avait mis au point ce système de cache pour les disques durs SATA traditionnels à plateaux, on notera que les dernières versions supportent également les SSD NVMe.

Si Optane a un avantage de latence net par rapport à la NAND, les chiffres d'IOPS annoncés pour les modèles 16 Go ne changent pas dramatiquement la donne par rapport aux derniers SSD haut de gamme

Intel devrait dévoiler un peu plus de détails sur le fonctionnement exact de la technologie dans quelques jours lors du CES, ainsi qu'effectuer des démonstrations.

Il sera intéressant de voir en pratique ce que cela apporte, car si proposer un cache en amont d'un disque dur à plateaux sera forcément bénéfique, l'impact pratique d'Optane accolé à un SSD rapide utilisant ses propres stratégies de cache (RAM + utilisation de MLC/TLC comme SLC en écriture) risque d'être plus difficilement perceptible sur une utilisation grand public, au delà de quelques benchs savamment choisis !

Des détails sur le 7nm à l'ISSCC 2017

La conférence ISSCC (International Solid-State Circuits Conference) se tiendra pour son édition 2017 du 5 au 9 février à San Francisco, et nos confrères d'EEtimes ont eu accès à l'avant programme.

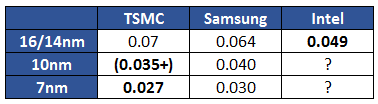

Comme tous les ans les acteurs du milieu des semi conducteurs y présenterons leurs nouveautés, et l'on notera que TSMC et Samsung présenterons leurs cellules SRAM (utilisées notamment pour la mémoire cache dans les puces). L'année dernière, Samsung avait proposé deux versions distinctes pour son process 10nm, optimisées pour la densité ou les performances, de 0.040 µm² et 0.049 µm².

D'après nos confrères, TSMC présentera une cellule SRAM 7nm de seulement 0.027µm², tandis que Samsung présentera une cellule SRAM 7nm de 0.030µm², mais fabriquée en EUV. D'après Samsung, l'EUV permettrait de diminuer la tension minimale nécessaire de 39.9mV (TSMC indique aussi des optimisations basse tension, on attendra la conférence pour comparer l'impact ou non de l'EUV).

La SRAM est un composant fondamental des puces et sa taille permet en général de se donner une bonne idée des process. Cependant il faut être assez méfiant, les constructeurs annonçant parfois des "records" de densité qu'ils n'utilisent pas forcément en production. Nous avons rapporté dans le tableau ci dessous les chiffres les plus bas (correspondant aux bibliothèques "hautes densité") pour TSMC, Samsung et Intel :

Par rapport au tableau, on notera qu'Intel n'utilise pas cette SRAM haute densité dans ses processeurs, mais de la SRAM 0.059 µm². Même en prenant cela en compte, Intel garde la meilleure densité à 16/14nm pour la SRAM. Le constructeur ne fournit pas encore d'infos sur ses futurs process.

TSMC n'a pas donné non plus de chiffre exact pour son 10nm, estimant simplement 50% de réduction par rapport à son 16nm sur la SRAM, ce qui nous vaut un chiffre entre parenthèses. Selon toutes vraisemblances, et conformément aux autres annonces sur la densité (2.1x d'après le constructeur), on estimera que TSMC devrait avoir une SRAM d'une taille légèrement inférieure à celle de Samsung.

Intel ne devrait pas effectuer d'annonce sur ce sujet lors de l'ISSCC, ce qui est assez dommage. Le constructeur devrait présenter les FPGA Altera Stratix 10 (14nm) tandis qu'AMD proposera une présentation plus en détails de Zen.

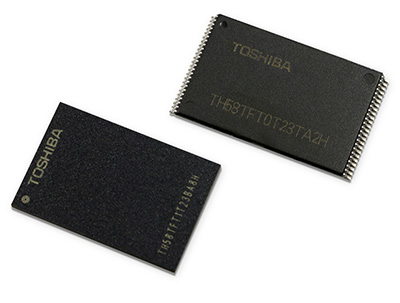

On notera aussi que Western Digital/Toshiba, ainsi que Samsung, présenterons des puces 3D NAND 512 Gbit TLC 64 couches. Dans le cas de Samsung, cette puce avait été annoncée cet été, plus de détails techniques devraient être disponibles. Pour Western Digital/Toshiba, cette puce avait été évoquée cet été comme objectif.

On notera que nos confrères pointent à raison un grand absent : une fois de plus, ni Intel, ni Micron, n'effectueront de présentation technique de leur mémoire 3D Xpoint !

HMC, DDR5 et 3D XPoint pour Micron

Micron a également pris la parole pendant la première matinée de Hot Chips, comme nous le rapportent une fois de plus nos confrères de ComputerBase . Ces derniers qualifient d'une honnêteté rafraîchissante la présentation de Micron, ne cherchant pas forcément à annoncer des chiffres extravagants. La société aurait même regretté, si l'on en croit nos confrères, que son partenaire Intel ait annoncé beaucoup trop tôt la mémoire 3D XPoint !

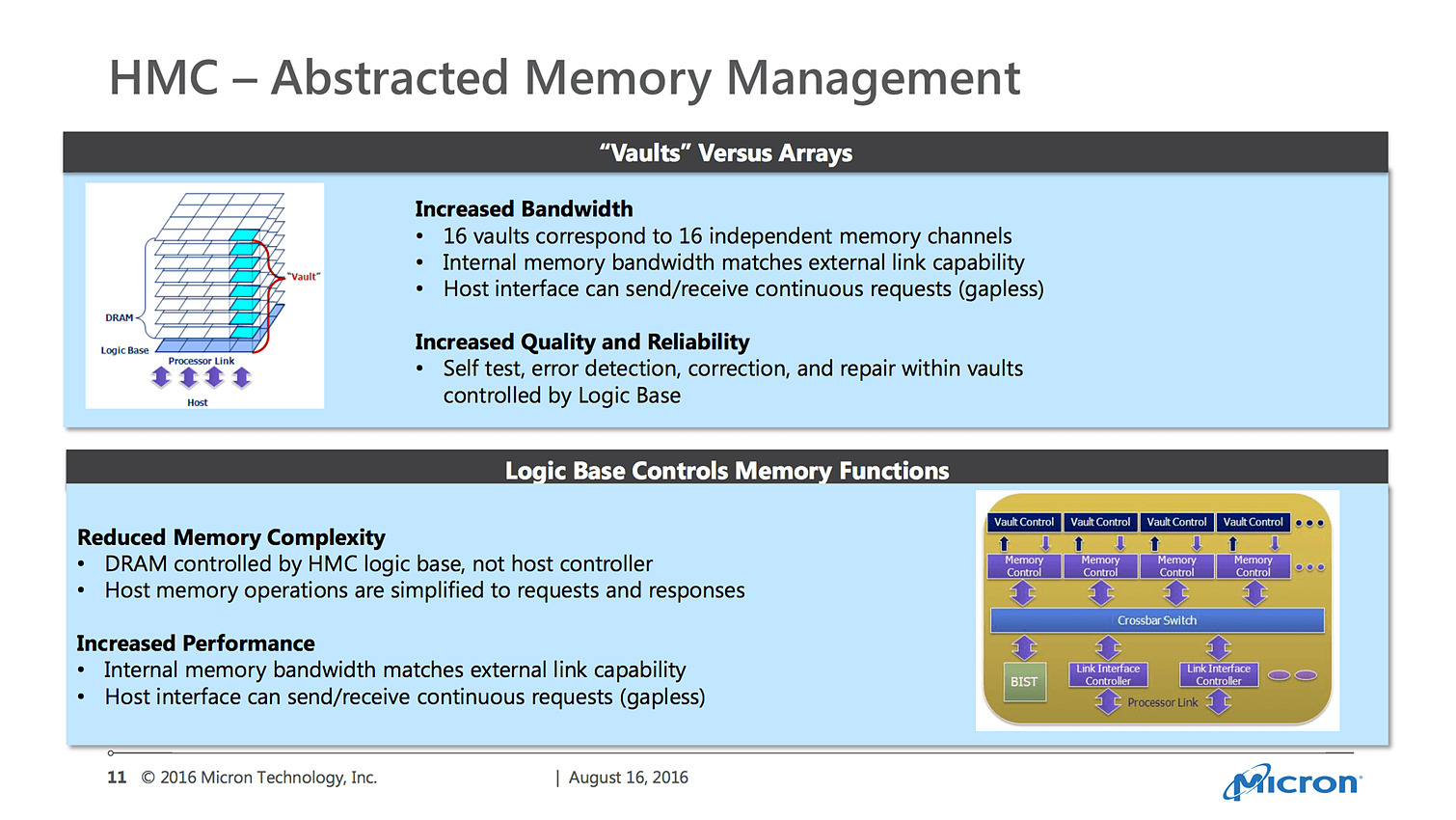

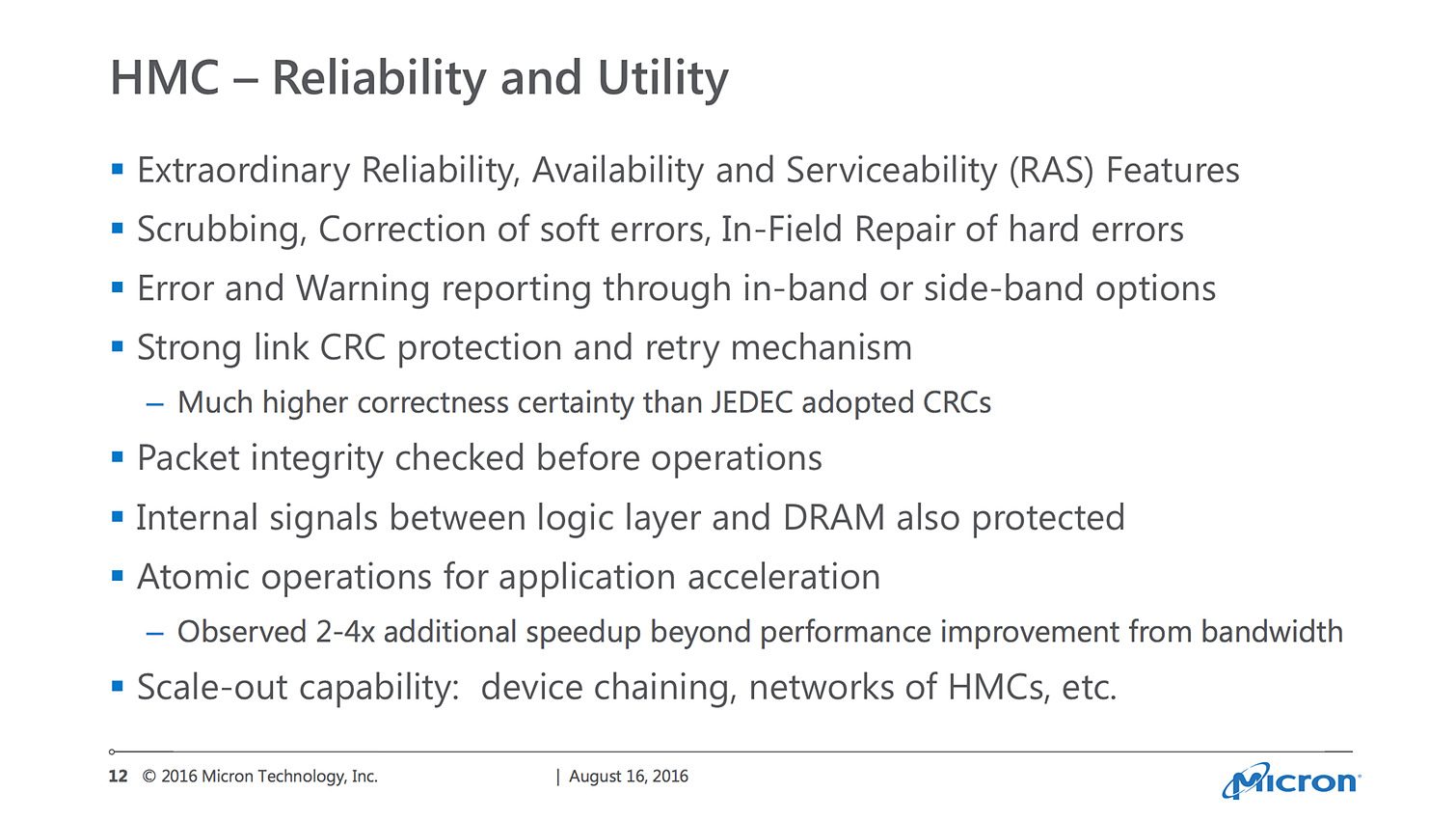

Dans le détail, Micron n'aura pas pu s'empêcher tout de même de qualifier la HBM de "mauvaise copie" de sa propre technologie Hybrid Memory Cube, plus complexe, coûteuse, et surtout assez peu disponible (elle devrait être présente sur le prochain Xeon Phi d'Intel, Knights Landing). Micron estime que la HMC dispose de nombreux avantages pour le marché du HPC, avec par exemple un meilleur algorithme de CRC que celui utilisé par le JEDEC pour la HBM.

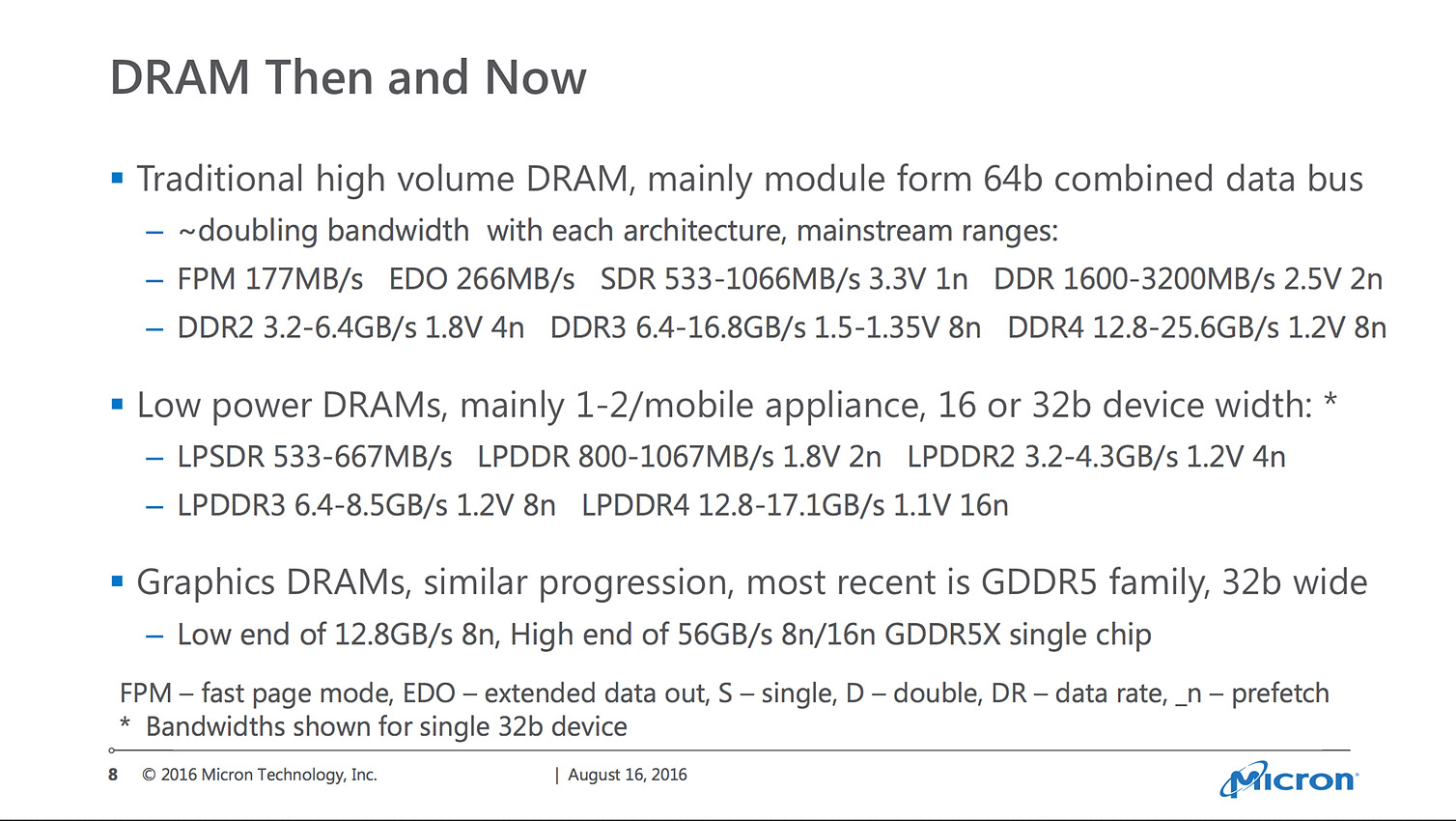

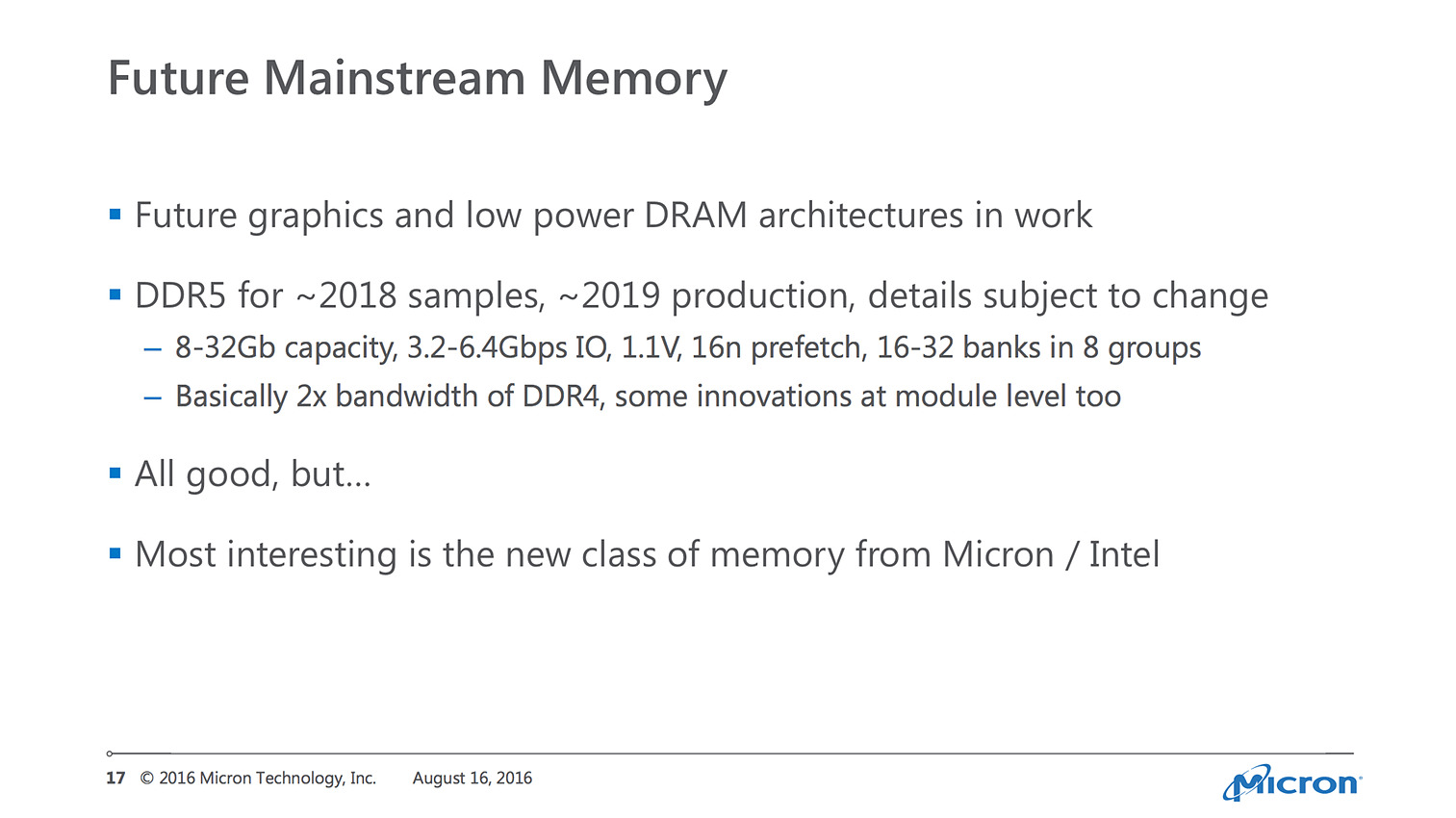

Micron aura également évoqué la DDR5 qui aura pour objectif de doubler la bande passante par rapport à la DDR4. Micron estime produire ses premiers échantillons courant 2018, avec une production en volume possiblement en 2019, mais plus probablement pour 2020.

Outre le tacle envers son partenaire Intel sur la mémoire 3D XPoint, on ne retiendra pas beaucoup d'informations, si ce n'est que Micron confirme que ce nouveau type de mémoire sera en production avant la fin de l'année.

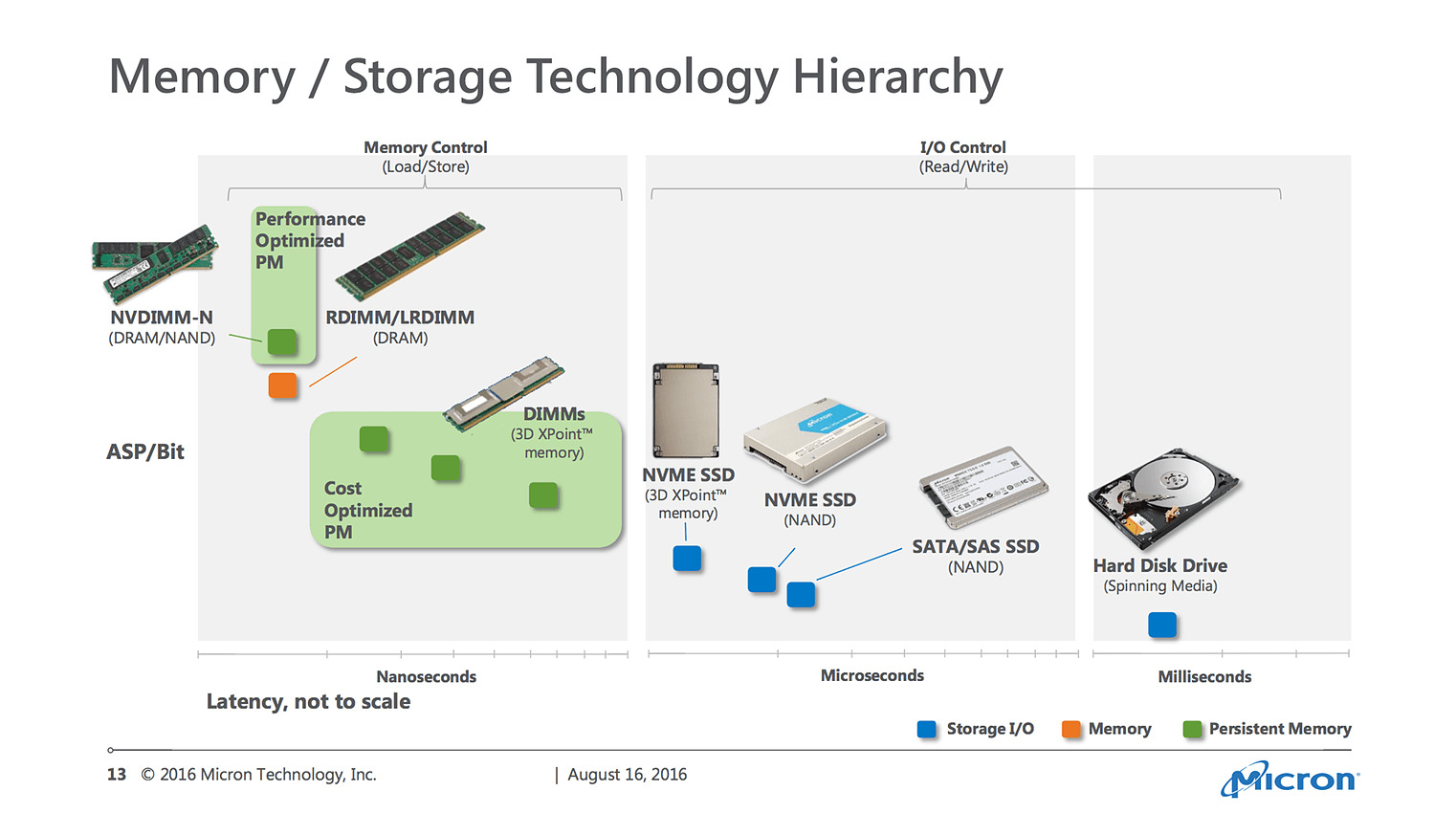

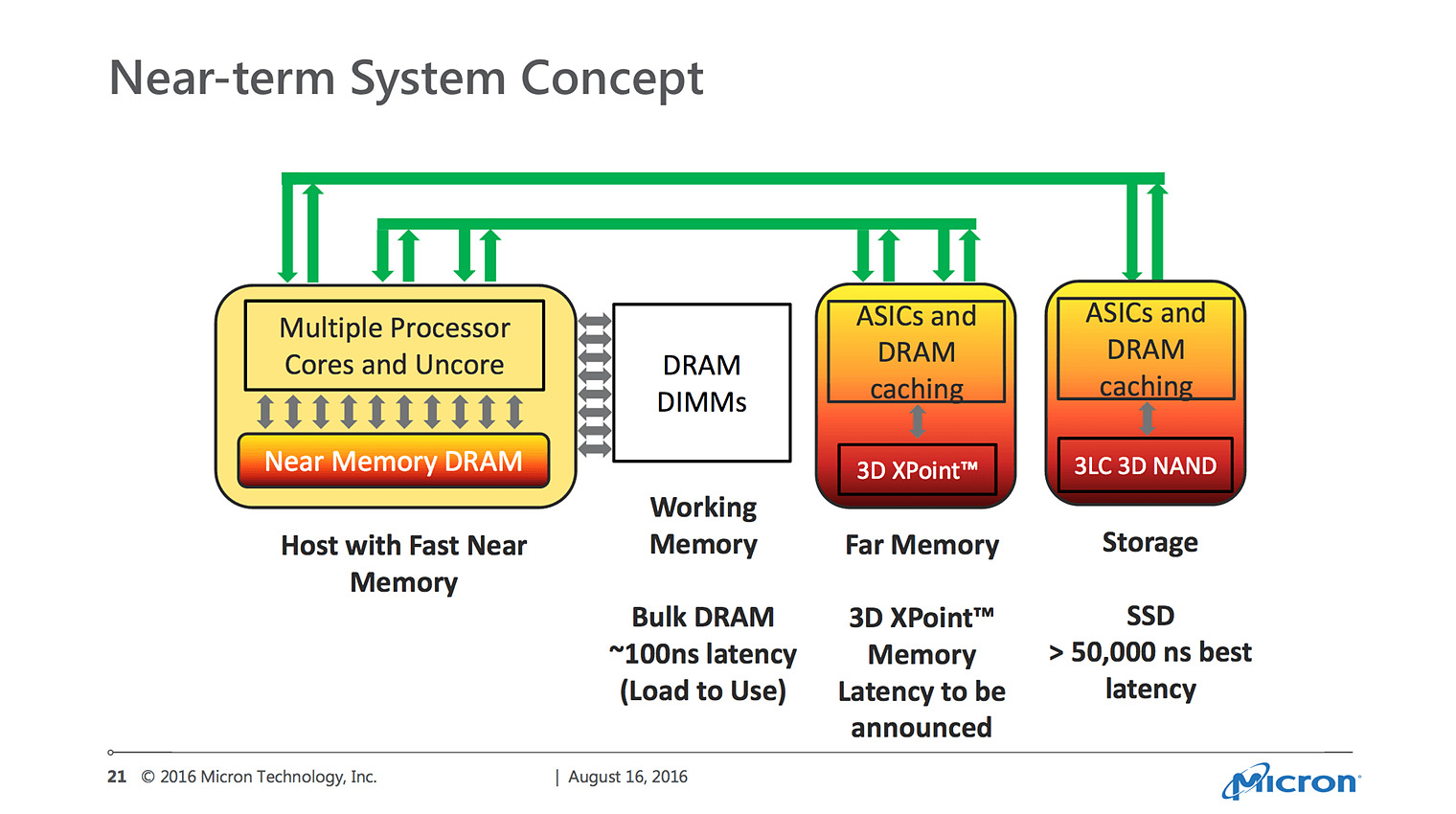

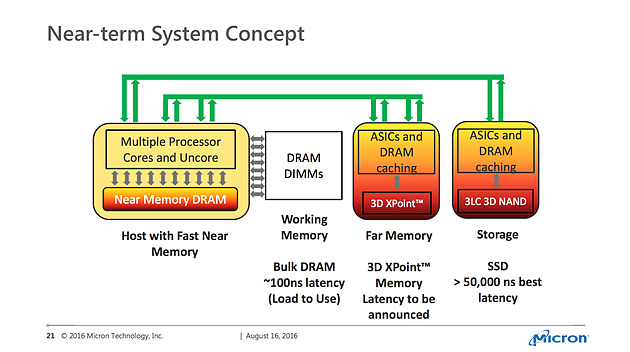

On retiendra ce dernier slide qui préfigure de ce que l'on devrait voir arriver sous peu sur les serveurs, avec deux tiers de mémoire DRAM. D'un côté une mémoire "proche", intégrée au processeur et rapide (HBM, ou plutôt HMC dans la vision de Micron) qui s'adjoint à la mémoire DRAM en barrettes plus classique. 3D XPoint et la 3D NAND proposant de leur côté deux tiers de stockages persistants.

Micron continue dans sa voie de l'originalité, dans un marché de la mémoire certes très concurrentiel. La société continue de mettre en avant sa GDDR5X, certes standardisée par le JEDEC mais qui n'a pas été adoptée par ses concurrents, mais aussi des solutions plus propriétaires comme l'Hybrid Memory Cube et 3D XPoint. Avec les ambitions de SK Hynix et de Samsung de pousser la HBM sur le terrain des PC clients, on peut cependant se demander si le pari d'ignorer la mémoire HBM ne se retournera pas contre Micron dans les mois à venir.

V-NAND Gen4 et Z-NAND pour Samsung

Samsung est lui aussi bien évidemment présent au Flash Memory Summit et en profite pour annoncer sa quatrième génération de mémoire NAND 3D (connue sous le nom marketing V-NAND). L'année dernière, Samsung annonçait sa troisième génération qui faisait passer à 48 couches pour obtenir jusque 32 Go par die.

Cette année, Samsung annonce 64 couches pour une densité maximale de 512 Gbit en TLC, soit 64 Go par die. De quoi permettre d'atteindre pas moins de 1 To par package (en superposant 16 dies). Samsung proposera donc un SSD BGA de 1 To avec 1500 Mo/s en lecture et 900 Mo/s en écriture.

Le PM1643 de 32 To, photo The SSD Review

Le SSD PM1633a de 16 To (qui avait été annoncé lors du Flash Memory Summit 2015 il y a un an, mais seulement commercialisé ces dernières semaines sera remplacé à terme par un modèle 32 To, le PM1643.

Une version 32 To en NVMe est également annoncée sous la référence PM1735 et un modèle M.2 de 4 To est également au programme en taille standard, et Samsung compte proposer en 2017 un "nouveau" format de M.2 dédié aux serveurs, le M.2 32114 (32mm de large pour 114 de long) avec une capacité pouvant atteindre 8 To, ce qui permettra d'atteindre 256 To de stockage dans un rack 1U.

Bien évidemment, et le lancement ces derniers jours du PM1633a le prouve, les annonces de Samsung se traduiront au fur et a mesure dans les mois à venir, le communiqué de presse du constructeur évoque le quatrième trimestre pour les premières disponibilités de produits basés sur la V-NAND de quatrième génération. Le PM1643 est quand à lui annoncé pour 2017 sans plus de précision.

On notera enfin une dernière annonce très floue de la part de Samsung avec la Z-NAND, un "nouveau type de mémoire" qui partage "la même structure fondamentale que la V-NAND" en utilisant un "design de circuit et un contrôleur unique". Si cela ne nous dit pas grand chose sur la manière dont fonctionne la technologie, il faut y voir la réponse de Samsung à la PRAM 3D XPoint d'Intel/Micron, le constructeur ne s'en cache en reprenant les mêmes arguments, une mémoire qui vient s'intercaler entre la DRAM (volatile, très rapide) et la NAND (non volatile, moins rapide).

La Z-NAND aurait une latence similaire à la PRAM, des performances séquentielles 20% supérieures, et une efficacité énergétique significativement meilleure. Bien entendu ces chiffres sont assez creux sachant que Samsung ne précise pas à quelle PRAM il se compare, mais on voit bien qu'Intel et Micron sont visés par cette annonce. Plus de détails devraient être disponibles d'ici quelques mois, Samsung annonçant une disponibilité en 2017.

PRAM 3D XPoint QuantX pour Micron

Le Flash Memory Summit a été l'occasion pour Micron de reparler de mémoire 3D XPoint. Pour rappel, Intel et Micron avaient annoncé cette mémoire l'année dernière, avec pour ambition de proposer un intermédiaire entre la mémoire RAM classique (très rapide, volatile) et la NAND (moins rapide, mais non volatile).

Côté technique les deux sociétés n'avaient pas dévoilé grand chose, on sait désormais qu'il s'agit de mémoire à changement de phase (PRAM) associée à un switch Ovonyx. A l'époque, les constructeurs avaient indiqué que leur mémoire était en production et un lancement "courant 2016" était attendu. En début d'année cependant, les perspectives ne semblaient pas très encourageantes.

Plus récemment, chez Intel, une roadmap avait filtré en juin, laissant penser que les premiers SSD utilisant la mémoire 3D XPoint pourraient arriver entre la toute fin de l'année et le début de l'année prochaine. Intel utilisera la marque commerciale Optane pour distinguer ses disques, et l'on aurait droit dans un premier temps à un "accélérateur" m.2 (un petit SSD de faible capacité en PCIe x2) suivi de modèles PCIe Gen3 NVMe s'interfaçant d'abord en x4 puis en x2.

Côté Micron, le constructeur avait simplement dit qu'il fallait s'attendre à "voir" sa 3D XPoint cette année. C'est en quelque sorte ce qui s'est passé puisque Micron a fait une démonstration lors d'une présentation pendant le premier jour du Flash Memory Summit, annonçant au passage qu'elle sera disponible sous le nom commercial QuantX. Comme chez Intel, on verra d'abord sous la marque QuantX des SSD, la déclinaison DIMM étant prévue pour plus tard.

Côté technique donc, on notera la confirmation de la latence très faible évoquée à l'époque, environ 10 microsecondes en lecture et 25 en écriture, environ dix fois moins que ce que permet la mémoire NAND.

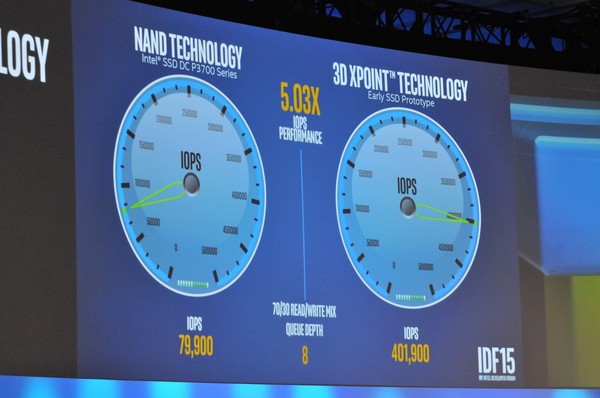

C'est du côté des IOPS que l'on aura obtenu un peu plus d'informations. Durant l'IDF 2015, Intel avait fait la démonstration d'un SSD atteignant 400 000 IOPS sur une charge de 70%/30% en lecture écriture QD8 sans préciser le nombre de lignes PCIe utilisées.

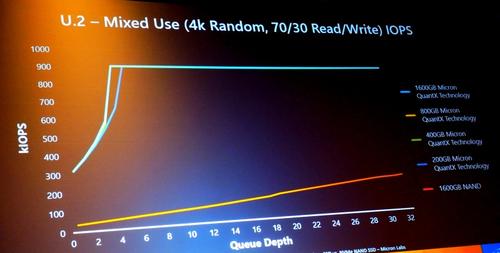

Lors de la démonstration du Flash Memory Summit, les prototypes de Micron ont atteint 900000 IOPS sur la même charge (70%/30%) sur un lien PCIe Gen3 x4, et près de 1.9 millions d'IOPS sur un lien x8. On notera que quatre capacités, 200, 400, 800 et 1600 Go étaient utilisées par Micron dans ses graphiques. Reste que pour ce qui est d'une éventuelle commercialisation, il faudra encore attendre. Un post de blog de Micron se contentant de parler d'une sortie "au cours des douze prochains mois".