AMD Ryzen 7 1800X en test, le retour d'AMD ?

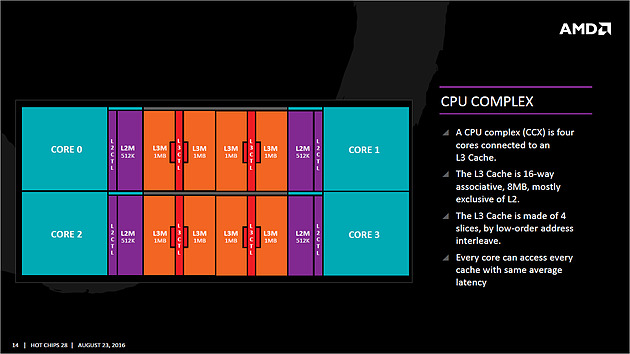

Les coeurs Zen dont nous avons détaillé l'architecture sur la page précédente sont regroupés dans une puce Ryzen dans des blocs modulaires appelés CPU Complex (AMD évite le mot de module, on les comprend !).

CCX : CPU Complex

Chaque CCX est composé de quatre coeurs qui sont regroupés autour d'un cache L3 de 8 Mo. En pratique c'est même un peu plus compliqué, puisque le cache L3 est partitionné en quatre morceaux de 2 Mo, un étant accolé à chaque coeur. Le L3 est de type "victime", les données qui sont éjectées du L2 se retrouvent stockées dans le L3.

C'est là que les choses deviennent un peu plus complexes puisque la latence devient variable en fonction de l'emplacement des données. Ainsi sur le schéma ci-dessus, si le Core 0 a besoin de données dans le L3 du troisième Core 3, la latence sera plus élevée que si les données sont dans le L3 du Core 0. AMD tempère cela en expliquant que tous les cores ont la même latence "moyenne" vers tous les caches, ce qui ne fait que tenter de noyer la différence.

Summit Ridge = Deux CCX reliés... mais comment ?

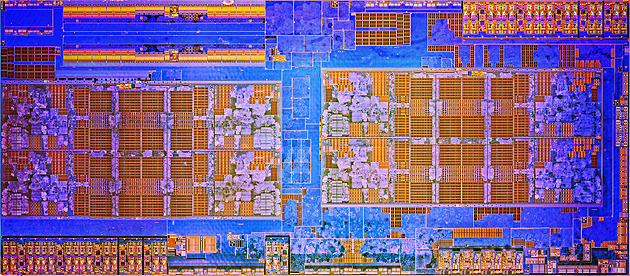

Là où les choses se compliquent encore plus, c'est dans le fait qu'un Ryzen 7 (les Summit Ridge lancés aujourd'hui) est composé de 8 coeurs, et donc de deux CCX indépendants.

Le die de Ryzen, on peut voir à gauche et à droite les deux CCX indépendants

AMD nous a donné beaucoup plus de détails la veille du lancement sur la question. Mike Clark avait expliqué durant la conférence Hot Chips que les deux CCX ne disposaient pas de lien direct entre eux.

AMD a clarifié cela, en pratique, chaque CCX est relié via une data fabric (rebaptisée Infinity Fabric, le marketing est parfois ironique) au contrôleur mémoire. En pratique, quand un coeur a besoin d'une information qui n'est pas dans la hiérarchie de cache de son CCX local, deux requêtes sont envoyées dans la data fabric, la première vers le contrôleur mémoire qui tente de rapatrier la donnée, la seconde vers l'autre CCX (en passant par un switch placé juste devant le contrôleur mémoire, entre les CCX et le contrôleur). Si le second CCX dispose de la donnée, elle est rapatriée directement, et la demande faite au contrôleur mémoire est annulée. Si ce n'est pas le cas, on attendra que le contrôleur mémoire rapatrie la donnée. AMD ajoute que le protocole MOESI est utilisé pour synchroniser les deux caches.

D'un point de vue conceptuel, Ryzen est donc assez différent des autres processeurs, qui disposent en général d'un lien direct entre les groupes de coeurs lorsque les caches sont séparés. On se retrouve à mi-chemin entre une architecture classique, et un système bi-CPU.

Si l'on reprend notre exemple plus haut, et que le Core 0 doit accéder à une donnée présente dans l'autre CCX, on paiera donc une pénalité de latence par rapport à si la donnée est présente dans le CCX où se situe le core. Mais en général, on va s'attendre à voir des latences mémoires plus hautes du fait de la nécessité d'effectuer deux requêtes à chaque fois dès que l'on sort du CCX.

Il nous semble probable qu'AMD révise assez rapidement cette approche avec d'autres itérations de l'architecture Zen, tant cela pourrait impacter les performances dans des cas spécifiques.

Et aussi un SoC !

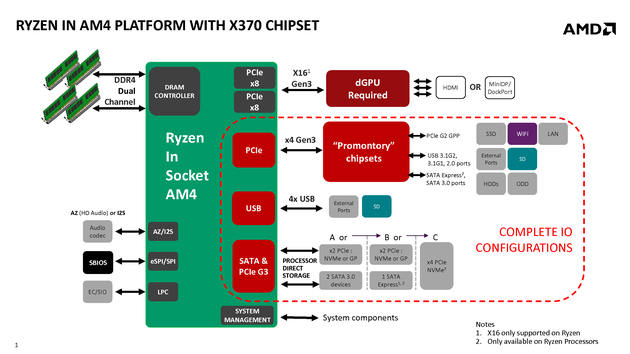

En plus des deux CCX et du contrôleur mémoire double canal, on retrouve dans les Ryzen plusieurs blocs supplémentaires. Le premier gère 24 lignes PCI Express 3.0. Ces dernières sont découpées en trois, avec seize lignes qui peuvent être partagées entre deux ports PCI Express (8x/8x), quatre lignes pour un port M.2 et enfin quatre lignes pour l'interconnexion avec le chipset.

Mais ce n'est pas tout, en effet Ryzen inclut nativement la gestion de quatre ports USB 3.0, ainsi qu'une gestion du SATA. Les autres IO (gestion système, connexion HD Audio, etc) sont également incluses ce qui permettra aux cartes mini-ITX de se contenter d'une petite puce compagnon interconnectée via un simple lien SPI.

Une tension par coeur

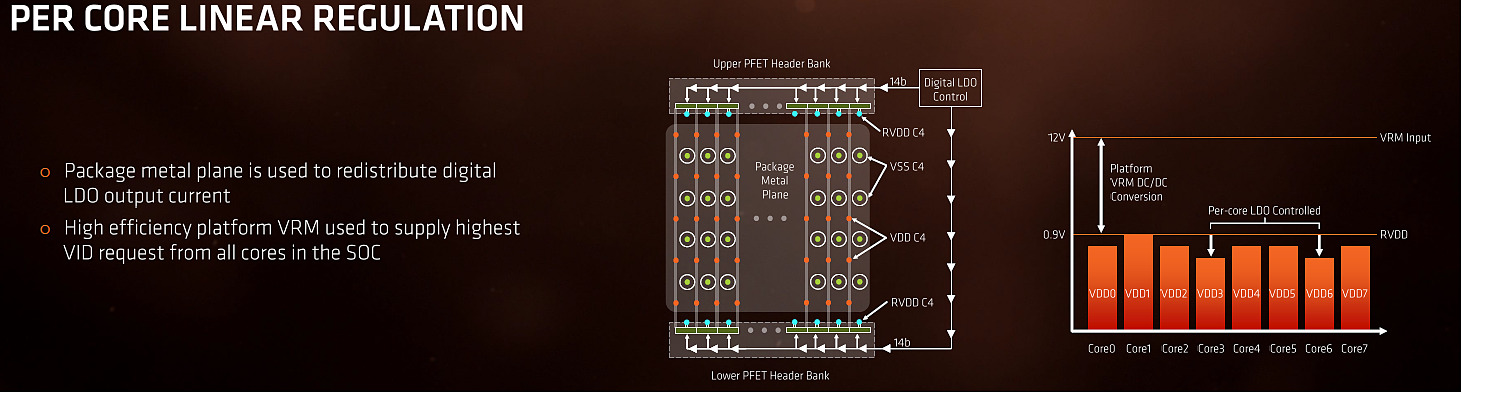

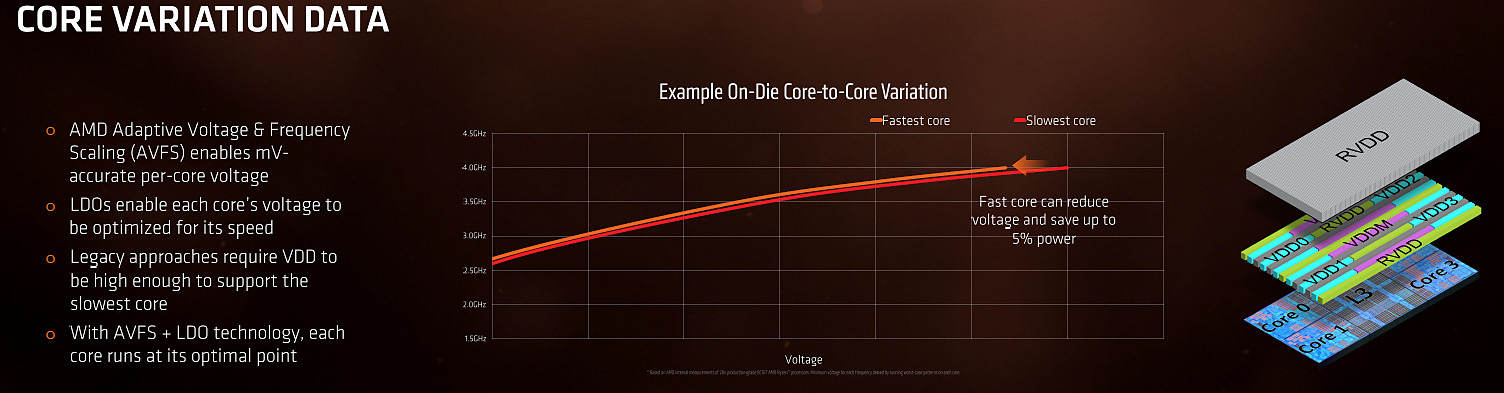

Côté alimentation, Ryzen innove là aussi puisque la carte mère AM4 fournie deux tensions principales au processeur, VDDCR CPU et VDDCR SOC (ainsi qu'une troisième pour le GPU pour les APU).

Les deux CCX sont alimentés par VDCCR CPU, le reste (data fabric, contrôleur mémoire, contrôleur pcie, soc) l'étant par VDDCR SOC qui est à 0,99v par défaut.

L'innovation se situe au niveau de VDDCR CPU, puisque la tension fournie par la carte mère sera légèrement modifiée afin de correspondre au mieux à celle nécessaire pour chacun des coeurs plutôt que d'appliquer une tension unique correspondant au moins bon. De quoi gagner en efficacité.

2 - Zen, une architecture équilibrée

3 - Ryzen, un SoC Zen 8 coeurs

4 - Ryzen 7 1800X, la gamme, DDR4

5 - Chipsets, plateforme AM4 et ASUS Crosshair VI Hero

6 - Piledriver, Zen et Broadwell-E à 3 GHz

7 - Impact du SMT/HT

8 - Retour sur le SMT et mode High Performance

9 - Overclocking en pratique

10 - Consommation, efficacité énergétique et "TDP"

11 - Protocole de test

12 - Compression : 7-Zip et WinRAR

13 - Compilation : Visual Studio et MinGW-w64/GCC

15 - IA d'échecs : Stockfish et Komodo

16 - Traitement photos : Lightroom et DxO Optics Pro

17 - Rendu 3D : Mental Ray et V-Ray

18 - Jeux 3D : Project Cars et F1 2016

19 - Jeux 3D : Civilization VI et Total War : Warhammer

20 - Jeux 3D : GTA V et Watch Dogs 2

21 - Jeux 3D : Battlefield 1 et The Witcher 3

22 - Indices de performance

23 - Retour sur le sous-système mémoire

24 - Retour sur le sous-système mémoire, suite

25 - Conclusion

Contenus relatifs

- [+] 09/05: AMD Ryzen 7 2700, Ryzen 5 2600 et I...

- [+] 23/04: MAJ de notre test des Ryzen 7 2700X...

- [+] 19/04: AMD Ryzen 2700X et 2600X : Les même...

- [+] 13/04: Les AMD Ryzen Pinnacle Ridge en pré...

- [+] 14/03: Des failles de sécurité spécifiques...

- [+] 08/03: Quatre Ryzen+ Pinnacle Ridge pour a...

- [+] 21/02: AMD Ryzen 5 2400G et Ryzen 3 2200G ...

- [+] 12/02: AMD lance les APU Ryzen 5 2400G et ...

- [+] 09/02: AMD Ryzen 3 2200G et 5 2400G : MAJ ...

- [+] 07/02: Windows 10, Meltdown et Spectre : q...