Les contenus liés au tag 3D NAND

Afficher sous forme de : Titre | FluxIntel P3100, SSD M.2 pour serveurs

Samsung 960 Pro et Evo au format M.2

Intel lance de nouveaux SSD NAND 3D

Des contrôleurs SSD chez... VIA !

Seagate montre un SSD de 60 To !

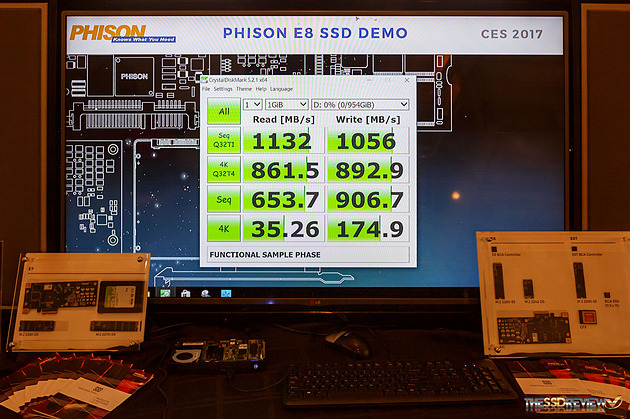

Le contrôleur Phison PS5008-E8 arrive

Annoncé au Flash Memory Summit de l'an dernier, le prochain contrôleur Phison commence à apparaître dans certains SSD.

Le PS5008-E8 opère deux lignes PCIe Gen3 via une interface NVme et se veut complémentaire par rapport au E7, que l'on trouve par exemple dans le SSD PNY évoqué la semaine dernière.

Comme prévu, il commence à équiper certains SSD qui visent le grand public. La plupart des SSD NVMe représentent une vitrine pour leurs constructeurs, qui les bardent généralement des meilleures technologies, les rendant souvent inaccessibles à de trop nombreux consommateurs.

Ainsi, même dans sa version 1 To, le prix au gigaoctet du Samsung 960 Evo reste de l'ordre de 50 centimes, là où celui d'un SSD plus classique fleurte actuellement avec les 30 centimes, voire moins.

Phison a donc décidé de développer un contrôleur d'entrée de gamme (qui prend tout de même en charge l'AES-256 et dispose d'un nouvel algorithme de corretions d'erreur baptisé StrongECC), afin de faire baisser les prix et d'attirer le plus grand nombre.

Évidemment, cela ne se fait pas sans sacrifice et le PS5008-E8 n'est pas le contrôleur le plus rapide du moment. Limité à 1,6 Go/s en lecture, il atteint tout de même 1,3 Go/s en écriture. Des débits qui peuvent se voir améliorer par des procédés de mise en cache comme le TurboWrite de Samsung.

En mode aléatoire, ses quatre canaux lui permettent de gérer jusqu'à 240 000 et 220 000 IOPS,respectivement en lecture et en écriture.

Prévu pour fonctionner avec de la NAND classique ou les plus récentes puces 3D, ce contrôleur prend également en charge la TLC.

On peut donc tout à fait imaginer des SSD équipés de NAND 3D TLC et de ce contrôleur Phison qui serait à la fois bien plus performants que les modèles SATA actuels, sans être beaucoup plus onéreux.

La marque KFA²/Galax a d'ailleurs récemment montré un SSD doté de ce contrôleur et de mémoire flash 3D (en MLC).

Ce contrôleur Phison devrait être disponible pour les constructeurs dans le courant du mois de mars. Une version sans DRAM (PS5008-E8T) est également attendue.

Nouvelle usine NAND/DRAM pour SK Hynix

![]() SK Hynix vient d'annoncer son intention de construire une nouvelle usine de fabrication de semi-conducteurs, dans la ville de Cheongju en Corée du Sud. La société investira environ 1.75 milliards d'euros dans la construction, qui démarrera au mois d'août prochain. La construction devrait être terminé en juin 2019 avec un début de production cette même année.

SK Hynix vient d'annoncer son intention de construire une nouvelle usine de fabrication de semi-conducteurs, dans la ville de Cheongju en Corée du Sud. La société investira environ 1.75 milliards d'euros dans la construction, qui démarrera au mois d'août prochain. La construction devrait être terminé en juin 2019 avec un début de production cette même année.

Le constructeur décrit dans le titre de son communiqué de presse cette usine comme dédiée à la mémoire NAND, et plus particulièrement à la 3D NAND. Cependant la société indique qu'elle pourrait, en fonction des besoins du marché, produire également d'autre types de mémoire (on pense plus particulièrement à de la DRAM).

En parallèle, SK Hynix annonce une extension de son usine de Wuxi en Chine, qui produit aujourd'hui la moitié de la DRAM du constructeur. Cet investissement d'un peu plus de 750 millions d'euros permettra d'augmenter l'espace de production pour mitiger les transitions vers de nouveaux nodes de fabrications, qui requièrent plus d'étapes et donc plus de machines. Ces travaux devraient être terminés en avril 2019.

Tout ce qui peut permettre d'augmenter la capacité de production de DRAM sera bienvenu, cette dernière voyant ses coûts augmenter massivement. Nous vous indiquions en début de mois que depuis l'été, la DRAM avait vu ses prix augmenter de 85%. On notera que 20 jours après ce relevé, le prix des puces de 1 Go de DDR4-2133 a encore augmenté de 5.5%, contre "seulement" 4.8% pour les puces 512 Mo !

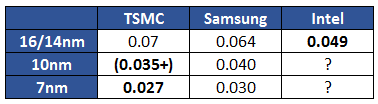

Des détails sur le 7nm à l'ISSCC 2017

La conférence ISSCC (International Solid-State Circuits Conference) se tiendra pour son édition 2017 du 5 au 9 février à San Francisco, et nos confrères d'EEtimes ont eu accès à l'avant programme.

Comme tous les ans les acteurs du milieu des semi conducteurs y présenterons leurs nouveautés, et l'on notera que TSMC et Samsung présenterons leurs cellules SRAM (utilisées notamment pour la mémoire cache dans les puces). L'année dernière, Samsung avait proposé deux versions distinctes pour son process 10nm, optimisées pour la densité ou les performances, de 0.040 µm² et 0.049 µm².

D'après nos confrères, TSMC présentera une cellule SRAM 7nm de seulement 0.027µm², tandis que Samsung présentera une cellule SRAM 7nm de 0.030µm², mais fabriquée en EUV. D'après Samsung, l'EUV permettrait de diminuer la tension minimale nécessaire de 39.9mV (TSMC indique aussi des optimisations basse tension, on attendra la conférence pour comparer l'impact ou non de l'EUV).

La SRAM est un composant fondamental des puces et sa taille permet en général de se donner une bonne idée des process. Cependant il faut être assez méfiant, les constructeurs annonçant parfois des "records" de densité qu'ils n'utilisent pas forcément en production. Nous avons rapporté dans le tableau ci dessous les chiffres les plus bas (correspondant aux bibliothèques "hautes densité") pour TSMC, Samsung et Intel :

Par rapport au tableau, on notera qu'Intel n'utilise pas cette SRAM haute densité dans ses processeurs, mais de la SRAM 0.059 µm². Même en prenant cela en compte, Intel garde la meilleure densité à 16/14nm pour la SRAM. Le constructeur ne fournit pas encore d'infos sur ses futurs process.

TSMC n'a pas donné non plus de chiffre exact pour son 10nm, estimant simplement 50% de réduction par rapport à son 16nm sur la SRAM, ce qui nous vaut un chiffre entre parenthèses. Selon toutes vraisemblances, et conformément aux autres annonces sur la densité (2.1x d'après le constructeur), on estimera que TSMC devrait avoir une SRAM d'une taille légèrement inférieure à celle de Samsung.

Intel ne devrait pas effectuer d'annonce sur ce sujet lors de l'ISSCC, ce qui est assez dommage. Le constructeur devrait présenter les FPGA Altera Stratix 10 (14nm) tandis qu'AMD proposera une présentation plus en détails de Zen.

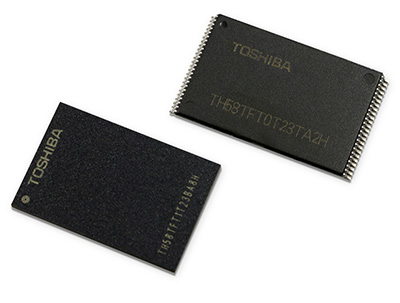

On notera aussi que Western Digital/Toshiba, ainsi que Samsung, présenterons des puces 3D NAND 512 Gbit TLC 64 couches. Dans le cas de Samsung, cette puce avait été annoncée cet été, plus de détails techniques devraient être disponibles. Pour Western Digital/Toshiba, cette puce avait été évoquée cet été comme objectif.

On notera que nos confrères pointent à raison un grand absent : une fois de plus, ni Intel, ni Micron, n'effectueront de présentation technique de leur mémoire 3D Xpoint !

Nouvelle usine NAND 3D pour Toshiba

Après avoir inauguré en juillet dernier sa nouvelle usine de mémoire flash au Japon, Toshiba vient d'annoncer qu'il s'engage à en construire une nouvelle.

Elle se situera toujours sur le même site japonais de Yokkaichi situé dans la ville de Mie, et sera dédiée à la production de la 3D NAND BiCS de Toshiba.

Le début de la construction est prévu pour 2017 et la société s'attend à ce que la première "phase" (l'usine sera construite en deux temps) soit opérationnelle à l'été 2018. Toshiba construira également un nouveau building dédié spécifiquement au R&D, où il centralisera des équipes qui étaient jusque là éparpillées.

L'annonce est faite par Toshiba qui n'est pas très clair sur le rôle que jouera Western Digital dans le financement. On rappellera que Toshiba et Sandisk collaboraient au sein d'une Joint Venture (Flash Forward). Le rachat de Sandisk par Western Digital avait lié les deux entreprises qui sont en compétition sur le marché des disques durs.

Le communiqué précise simplement que selon leurs "discussions" avec Western Digital, ils s'attendent à ce que ce dernier continue à participer aux investissements et aux opérations de cette usine. L'absence de communiqué commun chez WD laisse penser que les relations sont possiblement tendues entre les deux sociétés.

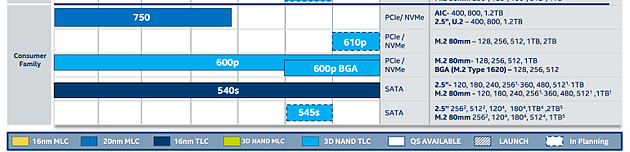

Deuxième génération de NAND 3D Intel mi 2017

Le site benchlife.info a publié un extrait de la roadmap SSD grand public d'Intel. Après les modèles 600p lancés cet été, équipés de NAND 3D, Intel lancera l'année prochaine des 610p.

On ne sait pas encore grand chose de ces modèles, si ce n'est qu'ils seront équipés de la seconde génération de NAND 3D d'Intel.

Il s'agira là aussi de modèles M.2 de 80mm de long (M.2 2280) en PCIe/NVMe, ils seront proposés dans des capacités de 128, 256, 512 Go, ainsi que 1 et 2 To. Leur lancement est prévu d'après nos confrères au quatrième trimestre 2017.

Au troisième trimestre, on verra arriver deux autres nouveautés, avec d'abord une version "BGA" du 600p, il s'agira en pratique de M.2 compacts (M.2 1620). Cette version sera disponible en 128, 256 et 512 Go.

Enfin on notera que sur l'entrée de gamme, les actuels 540s seront eux aussi succédés par une version NAND 3D. Les 540s ont la particularité d'utiliser de la TLC 16nm SK Hynix contrairement à ses autres modèles. Le 545s utilisera donc de la NAND 3D et sera disponible à la fois au format SATA et M.2. Les capacités démarreront dans les deux cas à 256 Go et atteindront 2 To en SATA, et 1 To en M.2. Intel devrait tout de même selon la roadmap conserver les 540s dans sa gamme. Ces 545s devraient être lancés au troisième trimestre 2017.