La V-NAND en production chez Samsung !

Publié le 07/08/2013 à 14:55 par Guillaume Louel

Le géant coréen vient d'annoncer la mise en production de sa technologie V-NAND, un nouveau type de mémoire flash conçu pour améliorer la densité. La V-NAND combine deux innovations par rapport à la mémoire flash NAND traditionnelle.

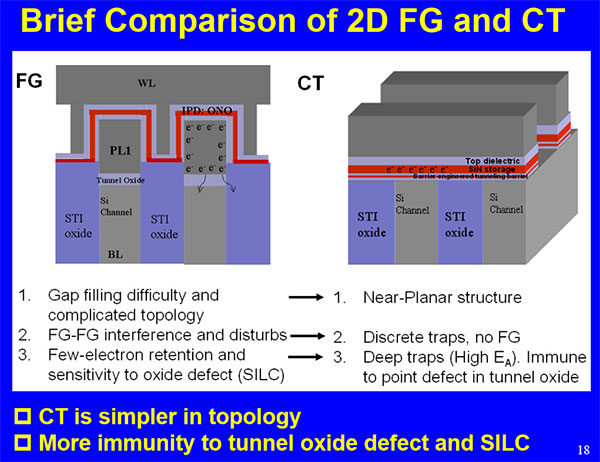

D'abord sur le fonctionnement même du stockage, la NAND traditionnelle utilise des transistors de type floating-gate pour stocker les informations. La V-NAND se distingue en utilisant un autre type de structure, dit charge-trap.

Schéma extrait de cette présentation de Macronix

La floating-gate est ici remplacée par une couche de nitrure de silicium, ce qui donne l'avantage d'une structure planaire plus facile à produire. Il ne s'agit pas en soit d'une technologie nouvelle puisque le concept date des années 70 et avait été popularisé par AMD et Fujitsu avec la mémoire flash NOR MirrorBit. Son application à la NAND avait été étudiée à plusieurs reprises, son inconvénient principal dans les structures traditionnelles SONOS (Silicon-Oxide-Nitride-Oxide-Silicon) étant qu'il est difficile de cumuler vitesse d'effacement rapide et rétention, bien qu'individuellement sur ces points la CT soit théoriquement plus intéressante que la NAND floating-gate. Depuis, des alternatives au SONOS utilisant par exemple des diélectriques high-k ont été mises au point.

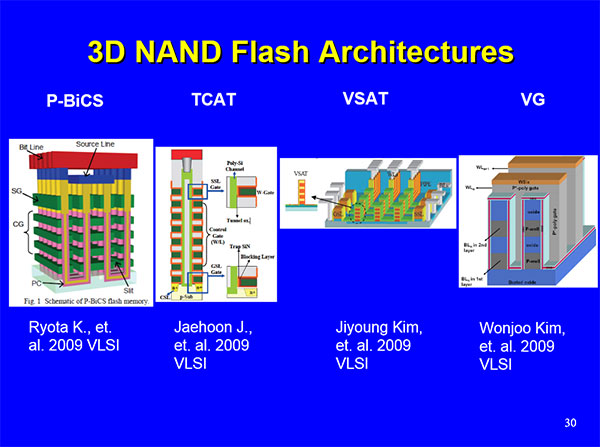

L'autre innovation consiste à produire ces structures de manière verticale, plutôt que de manière planaire. Samsung n'est pas le seul à travailler sur le sujet puisque Toshiba , dès 2007, avait proposé une structure de ce type que vous pouvez voir en image ci-dessous (la couche en rouge du schéma au-dessus est ici en (tube) jaune) :

En utilisant des structures verticales, il est possible d'améliorer significativement la densité de données, sans pour autant faire exploser les coûts. Plusieurs types de structures verticales étaient d'ailleurs à l'étude, Toshiba privilégiant sur le schéma ci-dessus une structure BiCS (Bit Cost Scalable) tandis que Samsung travaillait sur deux alternatives. Tout d'abord le TCAT (Terrabit Cell Array Transistor), une version améliorée du BiCS qui permet l'utilisation de diélectriques high-k et le VG-NAND (Vertical Gate NAND) dont la structure est un peu plus complexe :

Bien que le communiqué ne le précise pas exactement, nous supposons d'après certains termes utilisés dans le communiqué que c'est l'approche TCAT qui a été retenue, il s'agit en prime de celle qui semblait la plus prometteuse en termes de coûts. Le communiqué indique que Samsung pourrait en théorie placer jusqu'à 24 couches en hauteur, sans préciser le nombre de couches utilisées dans les premières puces.

Côté performances et caractéristiques, là encore le communiqué est flou et il faudra probablement attendre de voir les fiches techniques des puces pour avoir des informations précises. Samsung indique simplement que la V-NAND permet par rapport à de la NAND classique gravée en 1xnm (19nm probablement) d'augmenter la longévité des puces par un facteur compris entre 2 et 10x, tandis que les performances en écritures seraient doublées. Samsung se garde par contre d'indiquer quelle est la finesse de gravure utilisée pour cette V-NAND.

Il sera important de voir quelles seront les caractéristiques commerciales des puces, mais également leur prix ! La première proposera une densité de "seulement" 128 Gbit, une taille déjà atteinte avec des technologies classiques, avec pour objectif d'atteindre le Terabit sur une seule puce à terme via cette technologie.

Vos réactions

Contenus relatifs

- [+] 03/07: 3D NAND 96 couches chez Toshiba et ...

- [+] 28/06: Intel 545s, 1er SSD en NAND 3D 64 c...

- [+] 15/06: La V-NAND Gen4 de Samsung produite ...

- [+] 23/05: Toshiba et WD bientôt au point sur ...

- [+] 07/02: La NAND 3D 64 couches arrive aussi ...

- [+] 07/02: Micron : NAND 3D 64 couches pour ce...

- [+] 31/01: 1x nm et NAND 3D 72 couches chez SK...

- [+] 25/01: Samsung : la pénurie de NAND 3D se ...

- [+] 25/01: Hynix sur les rangs pour la NAND To...

- [+] 17/01: Nouveau contrôleur SSD SATA chez Ma...