Actualités informatiques du 20-07-2011

- OCZ annonce l'Indilinx Everest

- 1 To dans 2''1/2 et 9.5mm chez Western

- AMD A8-3870 : Un Llano débloqué

- Intel voudrait du PCI-Express x2

| Juillet 2011 | ||||||

|---|---|---|---|---|---|---|

| L | M | M | J | V | S | D |

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |

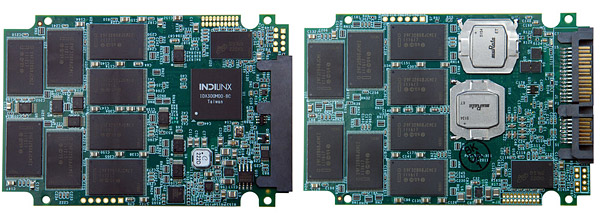

OCZ annonce l'Indilinx Everest

OCZ vient officiellement d'annoncer l'Indilinx Everest. Basé sur le contrôleur SATA 3.0 de nouvelle génération précédemment appelé Jet Stream puis Thunderbolt qui devait voir le jour dès 2010, Everest doit permettre à Indilinx de revenir dans la course.

Pour ce faire, Everest est constitué d'un CPU ARM dual core épaulé par un cache de DDR3 à 400 MHz pouvant atteindre jusqu'à 512 Mo. Il supporte une interface SATA 6 Gb/s et est prévu pour des débits séquentiels de l'ordre de 500 Mo /s pour une capacité totale de 1 To maximum. Cette vitesse est atteinte à l'aide de 8 canaux pouvant s'interfacer avec des Flash ONFI 2.0 / toggle DDR 1.0 à des vitesses pouvant atteindre 200 MT /s, alors que les autres contrôleurs seraient limités à 166 MT /s.

OCZ indique par ailleurs qu'Everest est optimisé pour les pages de 8 Ko que l'on trouve dans les mémoires Flash récentes, et qu'il dispose d'algorithmes spécifiquement destinés à réduire le temps de démarrage, avec un gain pouvant atteindre jusqu'à 50% par rapport aux SSD actuels, un chiffre à prendre avec de grosses pincettes.

Everest se distingue également de par un support plus complet des mémoires Flash, puisqu'il est déjà question de mémoire de classe 1xnm, a priori les 19nm annoncées récemment par Toshiba, mais également d'un support des mémoires SLC, MLC et TLC. Appelée également MLC 3BPC, la mémoire TLC permet de stocker 3 bits par cellule. Ceci permet d'abaisser nettement le coût de production, puisque la puce 8 Go 25nm annoncée en août 2010 par Micron est 21,5% plus petite qu'une MLC classique. Pas sûr cependant que le jeu en vaille vraiment la chandelle puisque Micron lui-même ne destine pas ses mémoires à des SSD, parlant d'ailleurs début 2009 de performances divisées par 2 et d'une endurance divisée par 10 par rapport à de la MLC.

Les choses ont peut être évolué de ce côté, et OCZ indique qu'Everest intègre une technologie propriétaire, Ndurance, qui est censée permettre d'utiliser des mémoires ayant une endurance réduite. Aucun détail n'est malheureusement communiqué sur Ndurance, et on sait juste qu'Everest intègre une correction d'erreurs basée sur l'algorithme BCH pouvant atteindre les 70 bits pour 512 octets, là où un SandForce SF-2000 se limite à 55 bits.

La plate-forme Indilinx Everest est actuellement disponible pour qualification auprès des OEM, OCZ ne donnant aucune information sur un éventuel futur SSD à base d'Indilinx Everest sous sa propre marque. Si ses performances brutes ne devraient pas bouleverser le monde du SSD, le support de la TLC, l'intégration d'algorithme spécifique au démarrage et la technologie Ndurance ont de quoi attiser la curiosité vivement la pratique !

1 To dans 2''1/2 et 9.5mm chez Western

Après Samsung en juin, c'est au tour de Western Digital de lancer un disque dur 2"1/2 offrant une capacité de 1 To malgré une hauteur standard de 9.5mm. Doté d'une interface SATA 3 Gb/s et de 8 Mo de cache, le WD Scorpio Blue WD10JPVT fonctionne à 5400 tpm et est au tarif officiel de 139$.

Western avait lancé en juillet 2009 le premier disque dur 2"1/2 de 1 To, mais il s'agissait d'un disque d'une hauteur de 12.5mm peu utilisée dans les portables et qui intégrait 3 plateaux. Le WD10JPVT utilise cette fois deux plateaux de 500 Go.

Pour rappel c'est Hitachi qui a le premier annoncé une telle densité avec le Z5K500 qui en embarquait un pour une hauteur de 7mm. Transposée sur un disque 3"1/2, une telle densité permettra datteindre des plateaux de 1 To qui devraient être utilisés sur les Spinpoint F6 EcoGreen attendus avant la fin de l'année.

AMD A8-3870 : Un Llano débloqué

AMD aurait dans ses cartons un AMD A8-3870. Prévu pour le dernier trimestre, ce nouvel APU partagerait les caractéristiques de l'actuel AMD A8-3850 (4 curs, 2 Mo de cache L2, Radeon HD 6550D, TDP de 100w) mais disposerait d'une fréquence plus élevée, peut être 3.1 GHz au lieu de 2.9 GHz, et surtout d'un coefficient multiplicateur débloqué ce qui facilitera l'overclocking, même si il faut bien dire que ce n'est pas la cible initiale de la plate-forme.

Actuellement il faut obligatoirement passer par le bus alors que toutes les autres fréquences sont basées dessus, ce qui peut poser problème au niveau des bus USB ou SATA dans certains cas. Reste à savoir si le coefficient du Radeon HD 6550D sera lui aussi accessible, dans la négative il faudra continuer à overclocker par le bus pour le faire monter en puissance.

Intel voudrait du PCI-Express x2

Selon VR-Zone , Intel souhaiterait que le PCI-Express x2 se généralise. Si le standard PCI Express permet des liens de 1, 2, 4, 8, 12, 16 ou 32 lignes (x1, x2, x4, x8, x12, x16 et x32), les ports et connecteurs n'ont été normés que pour les liens x1, x4, x8 et x16. De fait, en pratique les puces additionnelles PCI-Express suivent ces dernières spécifications et ne sont pas disponibles en version x2.

Selon VR-Zone , Intel souhaiterait que le PCI-Express x2 se généralise. Si le standard PCI Express permet des liens de 1, 2, 4, 8, 12, 16 ou 32 lignes (x1, x2, x4, x8, x12, x16 et x32), les ports et connecteurs n'ont été normés que pour les liens x1, x4, x8 et x16. De fait, en pratique les puces additionnelles PCI-Express suivent ces dernières spécifications et ne sont pas disponibles en version x2.

Cela pose bien entendu problème pour les chipsets offrants un nombre de ligne limités. C'est par exemple le cas des chipsets Intel Serie 6 (P67, H67, Z68

) mais aussi pour les futurs chipsets Intel Serie 7 (Z77, Z75, H77

) qui ne proposent que 8 lignes à la norme en PCI-Express 5 GT/s (500 Mo /s par ligne, dans chaque sens). Dès que l'on veut aller au-delà de cette bande passante, qui n'est qu'un maximum théorique, il faut passer à 4 lignes ce qui monopolise donc la moitié de celles disponibles, d'où le souhait d'Intel d'une généralisation d'une interface x2 malgré les coûts inhérents plus importants tant au niveau des puces que des cartes les implémentant.

A l'heure où le PCI Express 3.0 permettant des débits doublés est sur les rails, il est toutefois peu probable que le PCI-SIG, en charge de la norme PCI-Express, suive. Plutôt que de pousser un lien x2 en PCI Express 2.0, une généralisation rapide du PCI Express 3.0 qui permet la même bande passante avec un seul lien serait la bienvenue alors qu'il a fallu plus de 3 ans pour que les lignes à 5 GT /s passent du northbridge (X38 Express, septembre 2007) au southbridge (P67 Express, janvier 2011). De même, l'intégration d'un nombre de fonctionnalités croissant dans le southbridge permettrait de limiter l'utilisation du PCI-Express, et l'arrivée de 4 ports USB 3.0 sur les chipsets Intel Serie 7 va dans ce sens.