Les derniers contenus liés au tag 16/14nm

Afficher sous forme de : Titre | FluxAMD valide le 14nm LPP de GloFo

Résultats TSMC, 16 FinFET+ dans l'iPhone 6s

L'A9 d'Apple produit par Samsung et TSMC

16nm à l'heure, EUV en retard pour TSMC

Intel abandonne le Tick-Tock, confirme Kaby Lake

12nm et EUV à 7nm pour TSMC

Des détails sur le 7nm à l'ISSCC 2017

GTC: Nvidia Tesla P100: 10 Tflops, HBM2...

AMD annonce Polaris, sa future architecture GPU

Samsung en sus de GloFo pour le 14nm AMD ?

12nm et EUV à 7nm pour TSMC

TSMC a publié hier ses résultats financiers pour le dernier trimestre 2016. Le fondeur taiwannais a annoncé pour ce trimestre un revenu brut de près de 7.8 milliards d'euros, en hausse de 28.8% par rapport à la même période sur l'année précédente. Sur la totalité de l'année 2016, TSMC aura augmenté son revenu de 12.4% par rapport à 2015.

Pour 2017, TSMC s'attend à voir ses revenus progresser de "seulement" 5 à 10% (ce qui n'a pas manqué de décevoir les analystes financiers). Lors de la présentation des résultats, quelques informations supplémentaires ont été données.

Morris Chang, Chairman de TSMC s'est lancé dans quelques prédictions pour le marché 2017, s'attendant à voir le marché des smartphones grimper de 6% en unités, et celui du PC se contracter de 5% en unités également (il envisage également un déclin de 7% sur les tablettes tout en voyant le marché Internet of Things progresser de 34%).

Sur le 16/14nm, Morris Chang estime que la part de marché de TSMC est entre 65 et 70%, en dessous de ses attentes (TSMC dispose encore de 80% du marché sur le 28nm par exemple). Toujours poétique, le Chairman voit dans le 10 et le 7nm un "ciel bleu" par rapport à la compétition.

Quelques détails plus techniques ont été donnés, notamment par rapport à un "12nm" qui avait été évoqué ici ou là dans la presse. En pratique, TSMC travaille sur une nouvelle version de son process 16nm (une quatrième après les 16FF, 16FF+ et 16FFC) qui incorpore des améliorations importantes de densité. L'appellation commerciale exacte n'a pas été donnée, et on ne sait pas exactement quand elle sera disponible. On s'attendra dans quelques semaines à une annonce officielle, même si TSMC à confirmé aujourd'hui l'existence de ce "12nm".

Pour le 10nm, si le début de production est bien en cours, le gros du volume se situera sur la seconde partie de l'année (coïncidant avec le lancement des prochains iPhones dont le SoC utilisera le 10nm TSMC).

Sur le 7nm, plus de 20 sociétés travailleraient déjà sur des designs pour l'année prochaine, un chiffre qui devrait doubler dans l'année. Sur la question du 7nm en lui même, nous nous étions interrogés sur la manière dont le constructeur augmenterait la densité. Pour rappel, TSMC s'engage à lancer la production du 7nm dès la fin de l'année, il s'agira du node qu'utiliseront la majorité de ses clients, le 10nm devrait avoir une durée de vie courte et être réservé à quelques gros clients.

Le 10nm rappelle d'une certaine manière le 20nm de TSMC, lui aussi utilisé par des gros clients uniquement avant un passage rapide au 16nm. Cependant, avec une augmentation de la densité de 1.63x entre le 10 et le 7nm, la recette utilisée est plus complexe que pour le passage 20/16nm (qui ne proposait qu'une augmentation de densité de 1.15x). Nos confrères de SemiWiki, très au fait des détails, ont confirmé il y a quelques jours que des changements sur les tailles minimales des cellules sont en grande partie à l'origine des gains de densité et que pour réduire les coûts, TSMC évitera au maximum de généraliser le quadruple patterning (SAQP). Le 10 et le 7nm auront donc bel et bien des similarités techniques.

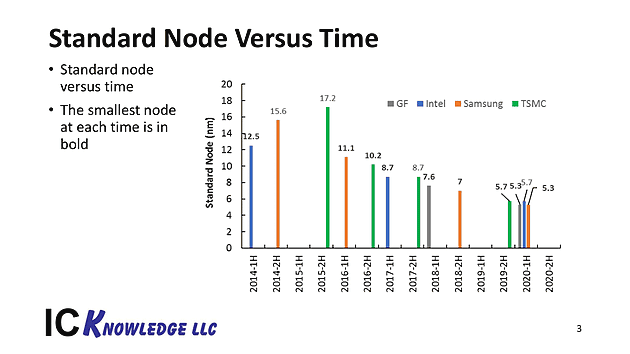

Pour essayer d'y voir un peu plus clair, et étant donné que plus aucun constructeur ne suit de règles équivalentes pour parler de densité, SemiWiki a publié ce graphique intéressant qui montre une "estimation" de la densité comparée de tous les fondeurs :

D'après SemiWiki, le 10nm d'Intel et le 7nm de TSMC auraient, après ajustement, une densité comparable. Il s'agit bien entendu d'estimations qui valent ce qu'elles valent, vous pouvez retrouver l'explication de la formule utilisée ici , mais elles donnent un bon ordre d'idée de ce à quoi il faut s'attendre (un seul bémol à cette analyse : les prévisions concernant GlobalFoundries nous semblent excessivement optimistes, en grande partie à cause des annonces de GlobalFoundries qui nous paraissent déconnectées de leur capacité d'exécution ces dernières années).

En pratique le 10nm de TSMC disposera tout de même d'une meilleure densité que l'actuel 14nm d'Intel, TSMC pourra donc se targuer d'avoir dépassé Intel côté process lorsque les premiers produits 10nm seront disponibles plus tard dans l'année. Et si Intel reprendra l'avantage avec "son" 10nm, TSMC sera effectivement - et pour la première fois - à parité dès la fin de l'année en lançant la production de son 7nm. Une situation qui durera un moment, et pour la première fois les constructeurs "fabless" pourront disposer d'un process équivalent en densité à celui d'Intel.

On notera enfin, concernant le 7nm, que TSMC a confirmé qu'ils inséreront l'EUV au bout d'un an de production à 7nm (soit fin 2018) pour créer une nouvelle version du 7nm (à l'image des multiples 16nm). Des propos plutôt optimistes concernant la lithographie EUV qui sera, Mark Liu le rappelle, indispensable à 5nm. Et un timing qui coïncide exactement avec le lancement de la production du 7nm de Samsung qui utilisera elle, dès le début, l'EUV !

Des détails sur le 7nm à l'ISSCC 2017

La conférence ISSCC (International Solid-State Circuits Conference) se tiendra pour son édition 2017 du 5 au 9 février à San Francisco, et nos confrères d'EEtimes ont eu accès à l'avant programme.

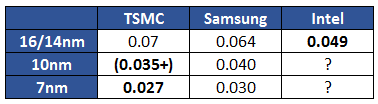

Comme tous les ans les acteurs du milieu des semi conducteurs y présenterons leurs nouveautés, et l'on notera que TSMC et Samsung présenterons leurs cellules SRAM (utilisées notamment pour la mémoire cache dans les puces). L'année dernière, Samsung avait proposé deux versions distinctes pour son process 10nm, optimisées pour la densité ou les performances, de 0.040 µm² et 0.049 µm².

D'après nos confrères, TSMC présentera une cellule SRAM 7nm de seulement 0.027µm², tandis que Samsung présentera une cellule SRAM 7nm de 0.030µm², mais fabriquée en EUV. D'après Samsung, l'EUV permettrait de diminuer la tension minimale nécessaire de 39.9mV (TSMC indique aussi des optimisations basse tension, on attendra la conférence pour comparer l'impact ou non de l'EUV).

La SRAM est un composant fondamental des puces et sa taille permet en général de se donner une bonne idée des process. Cependant il faut être assez méfiant, les constructeurs annonçant parfois des "records" de densité qu'ils n'utilisent pas forcément en production. Nous avons rapporté dans le tableau ci dessous les chiffres les plus bas (correspondant aux bibliothèques "hautes densité") pour TSMC, Samsung et Intel :

Par rapport au tableau, on notera qu'Intel n'utilise pas cette SRAM haute densité dans ses processeurs, mais de la SRAM 0.059 µm². Même en prenant cela en compte, Intel garde la meilleure densité à 16/14nm pour la SRAM. Le constructeur ne fournit pas encore d'infos sur ses futurs process.

TSMC n'a pas donné non plus de chiffre exact pour son 10nm, estimant simplement 50% de réduction par rapport à son 16nm sur la SRAM, ce qui nous vaut un chiffre entre parenthèses. Selon toutes vraisemblances, et conformément aux autres annonces sur la densité (2.1x d'après le constructeur), on estimera que TSMC devrait avoir une SRAM d'une taille légèrement inférieure à celle de Samsung.

Intel ne devrait pas effectuer d'annonce sur ce sujet lors de l'ISSCC, ce qui est assez dommage. Le constructeur devrait présenter les FPGA Altera Stratix 10 (14nm) tandis qu'AMD proposera une présentation plus en détails de Zen.

On notera aussi que Western Digital/Toshiba, ainsi que Samsung, présenterons des puces 3D NAND 512 Gbit TLC 64 couches. Dans le cas de Samsung, cette puce avait été annoncée cet été, plus de détails techniques devraient être disponibles. Pour Western Digital/Toshiba, cette puce avait été évoquée cet été comme objectif.

On notera que nos confrères pointent à raison un grand absent : une fois de plus, ni Intel, ni Micron, n'effectueront de présentation technique de leur mémoire 3D Xpoint !

GTC: Nvidia Tesla P100: 10 Tflops, HBM2...

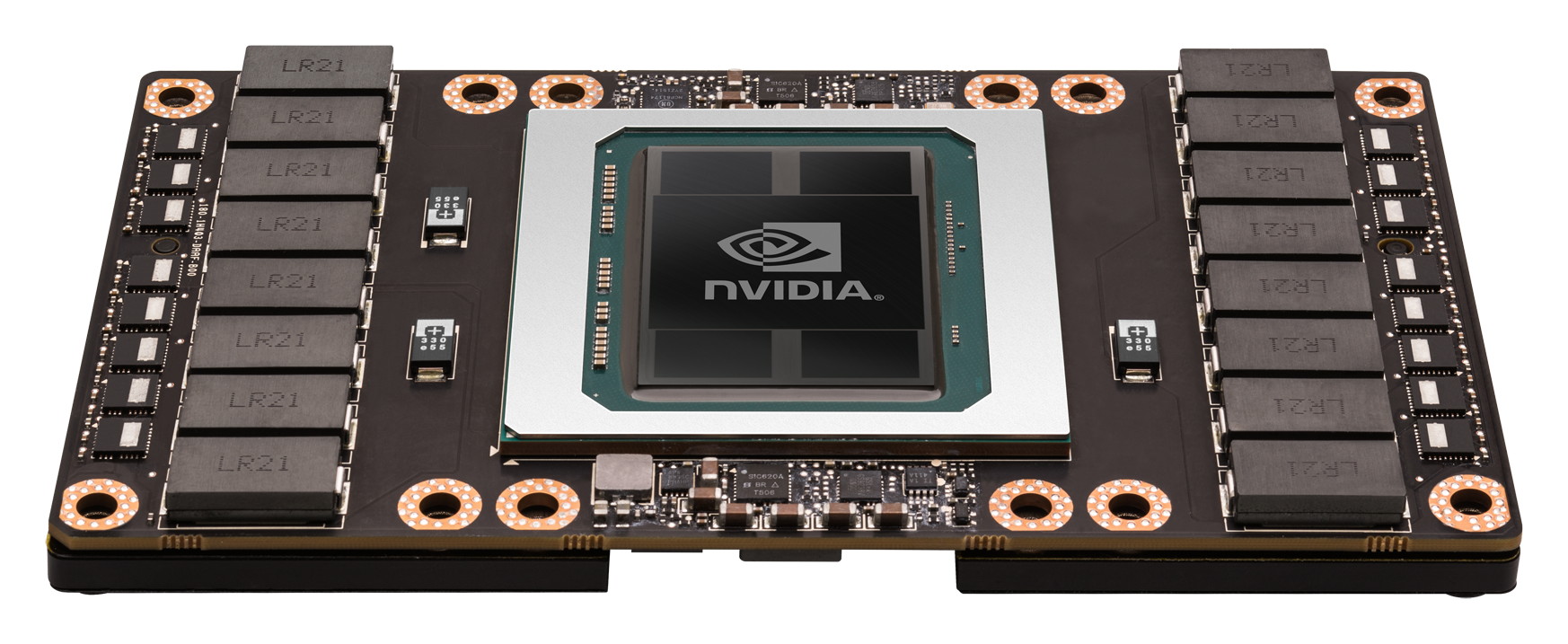

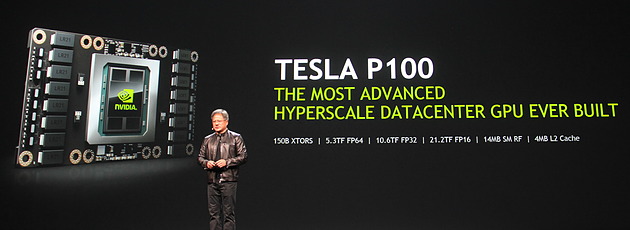

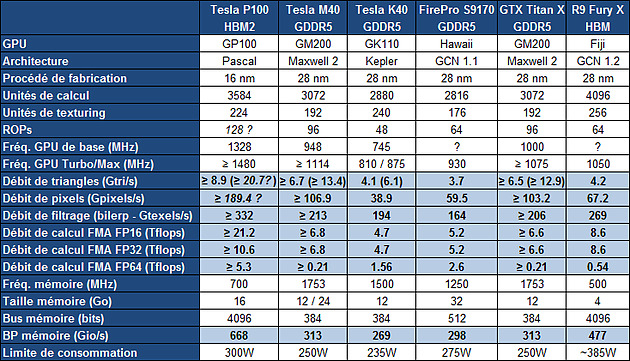

Comme prévu, Jen-Hsun Huang, le CEO de Nvidia, a levé un coin du voile concernant le premier produit Pascal, l'accélérateur Tesla P100. Au menu : 15 milliards de transistors, 10 Tflops, HBM2, 4 Mo de L2

Le Tesla P100 est un nouvel accélérateur dédié au calcul massivement parallèle qui embarque un GPU GP100, auquel nous faisions référence précédemment en tant que Pascal, nom de code de son architecture. Il s'agit bel et bien d'un nouveau monstre de puissance. Pour cette première utilisation de procédé de fabrication 16nm FinFET Plus, Nvidia n'a pas eu peur de concevoir un énorme GPU et le GP100 intègre pas moins de 15.3 milliards de transistors répartis sur 610 mm². A comparer aux 8 milliards de transistors de l'actuel GM200 qui mesure également 600 mm².

De quoi pouvoir pousser la puissance de calcul vers le haut mais surtout intégrer de nouvelles fonctionnalités avant tout dédiées au monde du HPC telles que la connectique NVLink qui offre une bande passante combinée de 160 Go/s.

Le Tesla P100 se présente sous la forme d'un module au format mezzanine qui revient à superposer 2 PCB, avec un ou plusieurs connecteurs entre ceux-ci. Sur le Tesla P100 il s'agit de 2 connecteurs de 400 broches qui vont permettre de proposer la connectique NVLink. Ce format facilite également l'intégration dans les serveurs et la mise en place d'un refroidissement performant ce qui permet à Nvidia de pousser le TDP à 300W.

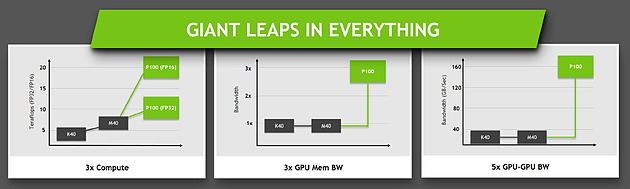

Concernant la puissance brute du Tesla P100, Nvidia annonce 10.6 Tflops avec GPU Boost en FP32, la précision classique, un gain de 60% par rapport aux 6.6 Tflops de la Titan X. L'architecture Pascal dans cette implémentation supporte également la double précision en demi-vitesse, soit 5.3 Tflops, un nouveau bond en avant par rapport au record actuel : 2.6 Tflops pour le GPU Hawaii d'AMD des FirePro W9100 et S9170. Dans l'autre sens, Pascal supporte également la demi-précision, le FP16, et peut alors monter à 21.2 Tflops.

A quelle configuration de GPU pourrait correspondre tout cela ? Au départ, nous supposions que le nombre d'unités de calcul passerait de 3072 sur le GM200 à 4608 sur le P100, réparties dans 36 blocs d'unités de calcul (SMP ?), ce qui aurait permis assez facilement d'augmenter à peu près toutes les capacités brutes du GPU de 50%. Il n'en est cependant rien et les changements sont plus profonds au niveau de l'architecture. Il s'agit ainsi pour le Tesla P100 de 3584 unités de calcul réparties dans 56 blocs de 64, mais le GP100 continent physiquement 60 de ces blocs.

Le gain de puissance de calcul brute provient ainsi principalement d'une hausse de la fréquence du GPU (+/- 1.5 GHz) alors que le GPU computing devrait profiter de cette organisation en plus petits blocs d'unités de calcul, mais également des autres évolutions de l'architecture Pascal, pour gagner en efficacité.

Sur ce point, Nvidia se contente de parler d'une augmentation de la taille du fichier registre. Au total le GM200 embarque +/- 6 Mo de registres, ce qui correspond à 256 Ko par SMM ou encore à 512 registres 32-bit par unités de calcul. Le GP100 passe à 15 Mo de registres, ce qui implique une augmentation de 100%, soit 256 Ko par SMP ou encore 1024 registres 32-bit par unité de calcul. De quoi permettre de maintenir un meilleur taux d'occupation des unités de calcul, particulièrement en double précision.

Le cache L2 passe de son côté de 3 à 4 Mo alors que l'interface mémoire est large de 4096-bit en HBM2. Nvidia annonce une bande passante de 720 Go/s pour les 16 Go de mémoire HBM2 CoWoS, le nom donné par TSMC à sa technologie 2.5D, similaire à celle employée par AMD pour son GPU Fiji.

Ce passage à la mémoire HBM2, associé à NVLink, à la puissance de calcul en hausse et au support de la précision FP16 permet au Tesla P100 d'afficher une progression conséquente sur différents plans par rapport à ses prédécesseurs.

Jen-Hsun Huang a terminé le chapitre consacré à Pascal en déclarant que la production en volume avait débuté et que son propre serveur basé sur le Tesla P100 serait commercialisé à partir du mois de juin. Il est probablement raisonnable de s'attendre à une nouvelle GeForce Titan d'ici là, mais sera-t-elle basée sur le GP100 ?

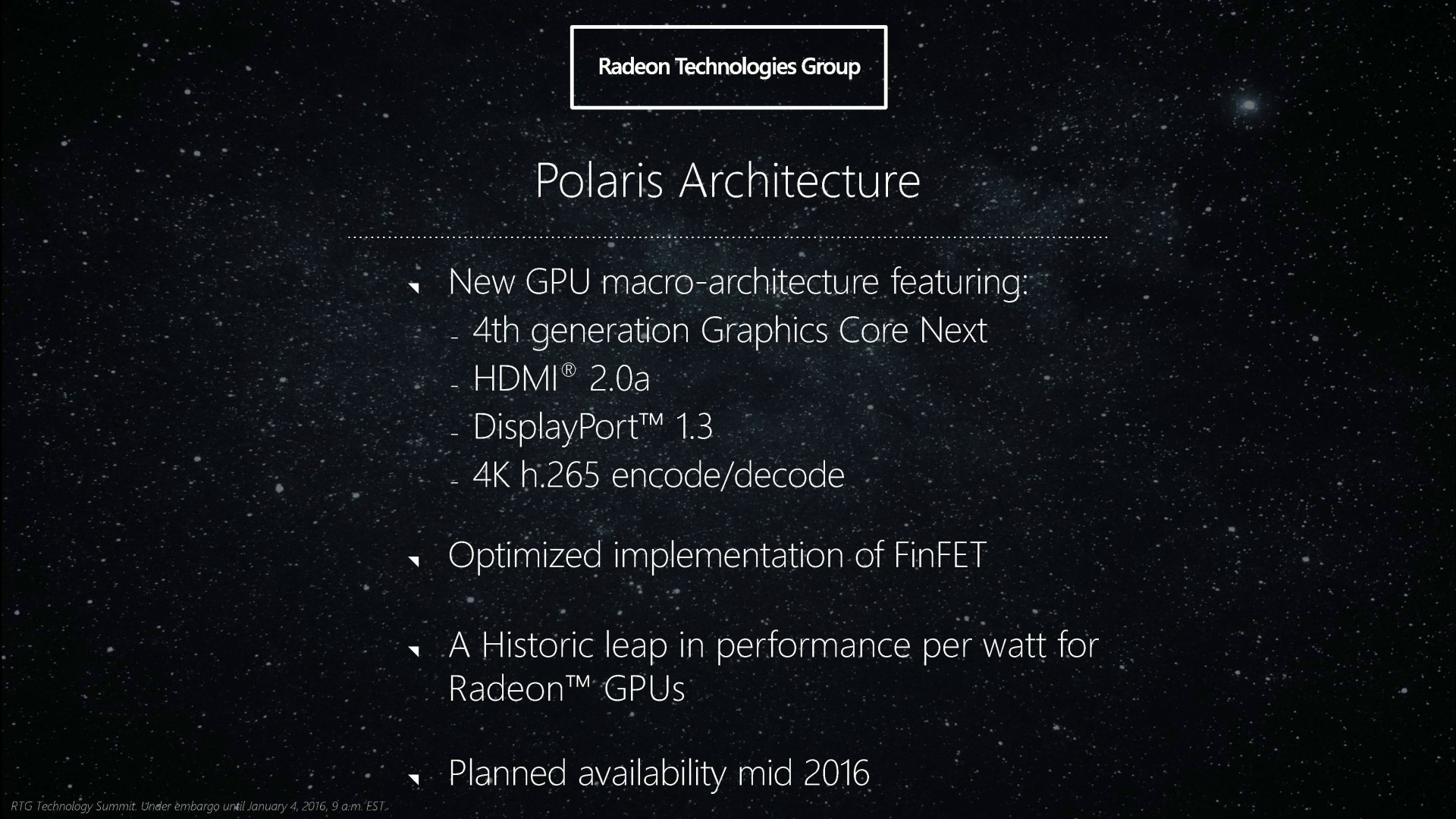

AMD annonce Polaris, sa future architecture GPU

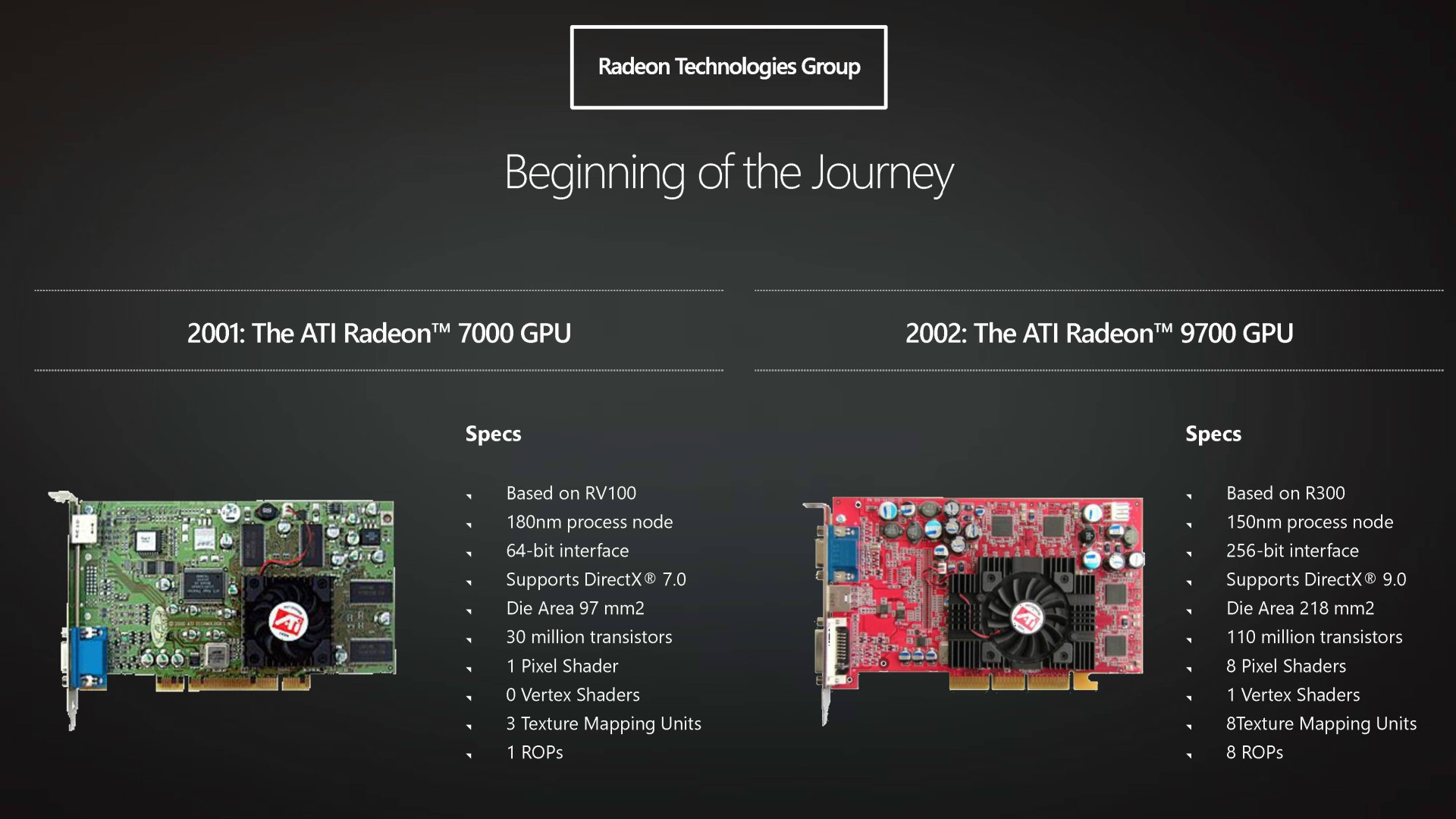

Enfin, après 4 années de GCN en 28nm, les Radeon vont accueillir une nouvelle architecture gravée en 14nm : Polaris. Et pour AMD le focus se portera sur l'efficacité énergétique avec un bond en avant annoncé sans précédent !

Le Radeon Technology Group d'AMD profite de ce début d'année pour lever un (très petit) coin du voile qui entoure sa prochaine génération de GPU, notamment en donnant un nom de code à son architecture : Polaris (l'étoile polaire). Et pour positionner sans équivoque ses objectifs avec cette architecture, AMD explique avoir opté pour ce nom de code en faisant le parallèle entre l'efficacité des étoiles à générer des photons et l'efficacité demandée aux GPU pour générer des pixels.

Comme vous le savez, l'architecture actuelle des Radeon est globalement en retrait par rapport à l'architecture Maxwell de Nvidia au niveau de l'efficacité énergétique. Fort de larges parts de marché et ayant bien anticipé le très long passage par le procédé de fabrication 28nm (exploité pour les GPU depuis 4 ans déjà !), Nvidia a développé deux architectures pour celui-ci : Kepler et Maxwell. En face, AMD est resté sur une architecture GCN moins efficace en se contentant d'évolutions mineures de son cur. Pourquoi ? Probablement parce que, contrairement à Nvidia, AMD avait parié sur l'exploitation d'un procédé en 20nm qui ne s'est jamais concrétisée pour les GPU.

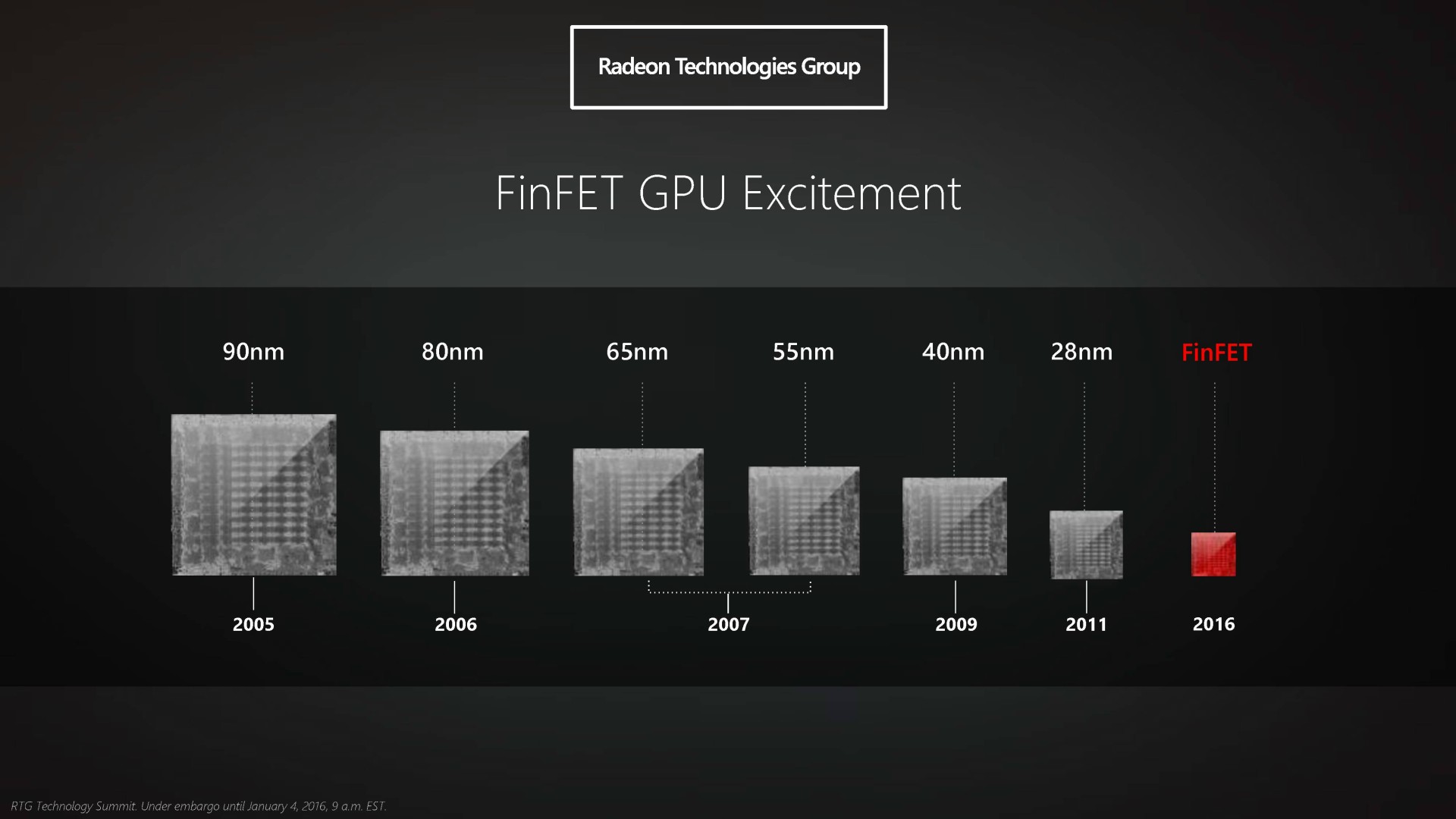

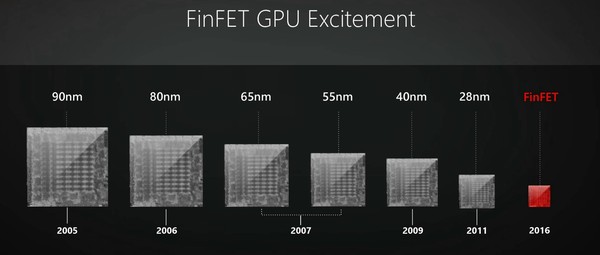

Tout cela va enfin changer en 2016 avec l'arrivée de GPU fabriqués en 16nm FinFET+ chez TSMC et en 14nm LPP chez GlobalFoundries et Samsung. Ces nouveaux procédés de fabrication ont pour point commun de donner enfin aux GPU l'accès à la technologie FinFET, de quoi donner un coup de pied dans une fourmilière bien trop tranquille à notre goût !

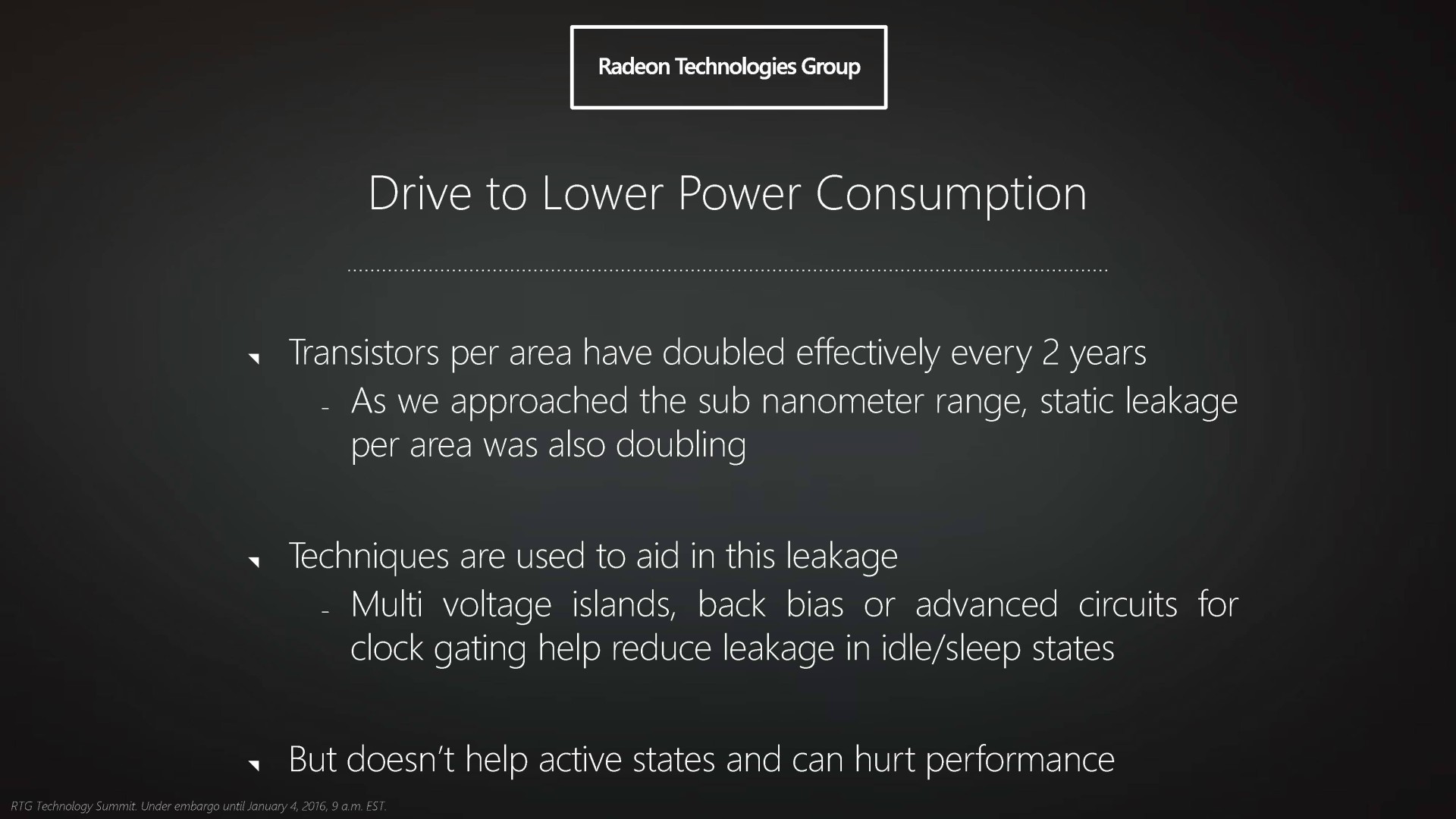

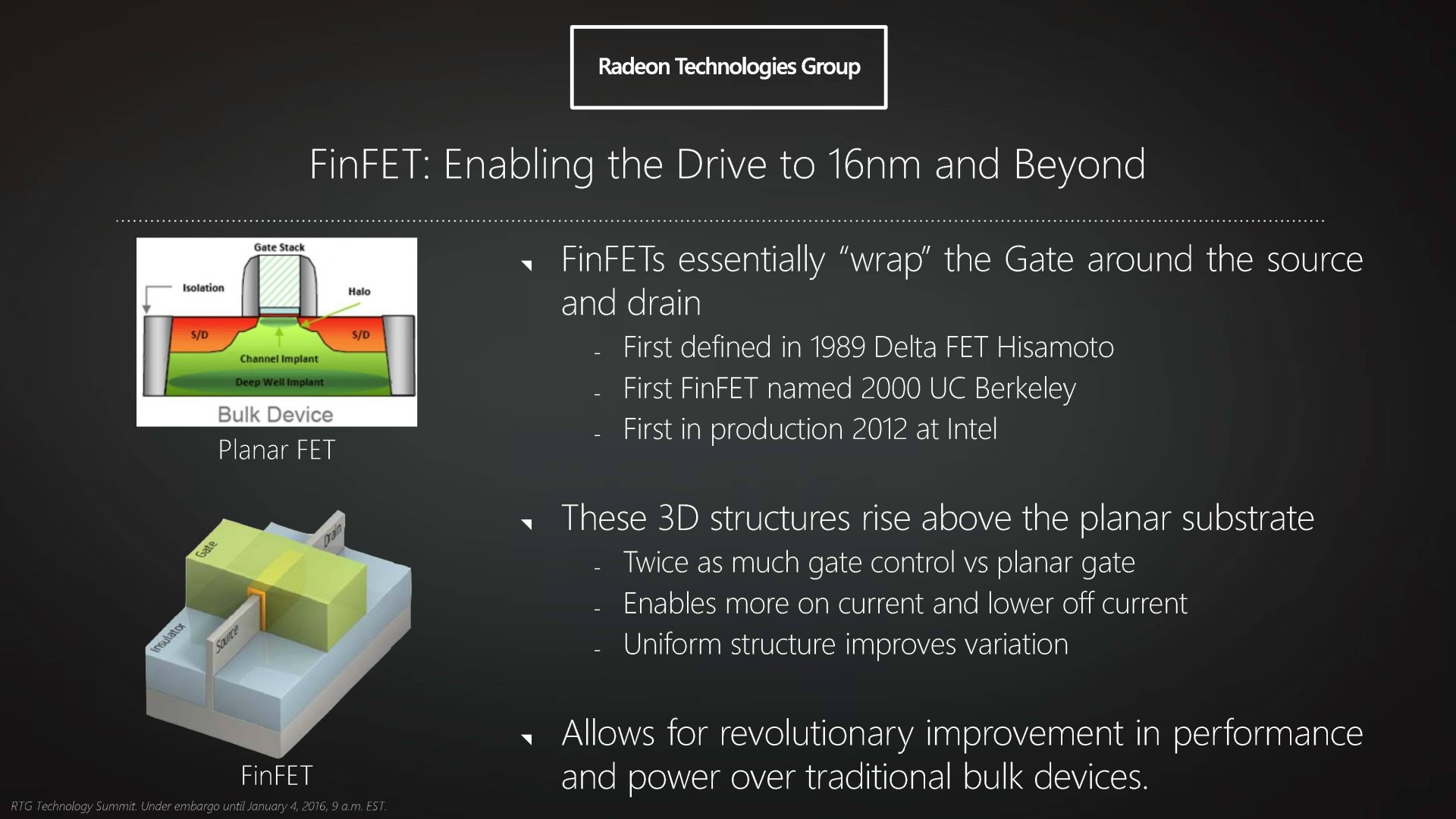

Introduit par Intel en 2012 sous les noms de "transistors tri-gates" ou de "transistors 3D", le FinFET se détache de la construction planaire classique des transistors en donnant une troisième dimension à la porte ce qui permet d'en augmenter la surface de contact et de mieux l'isoler. Les courants de fuite, qui peuvent représenter une grosse partie de la consommation d'un transistors classique, sont alors nettement réduits.

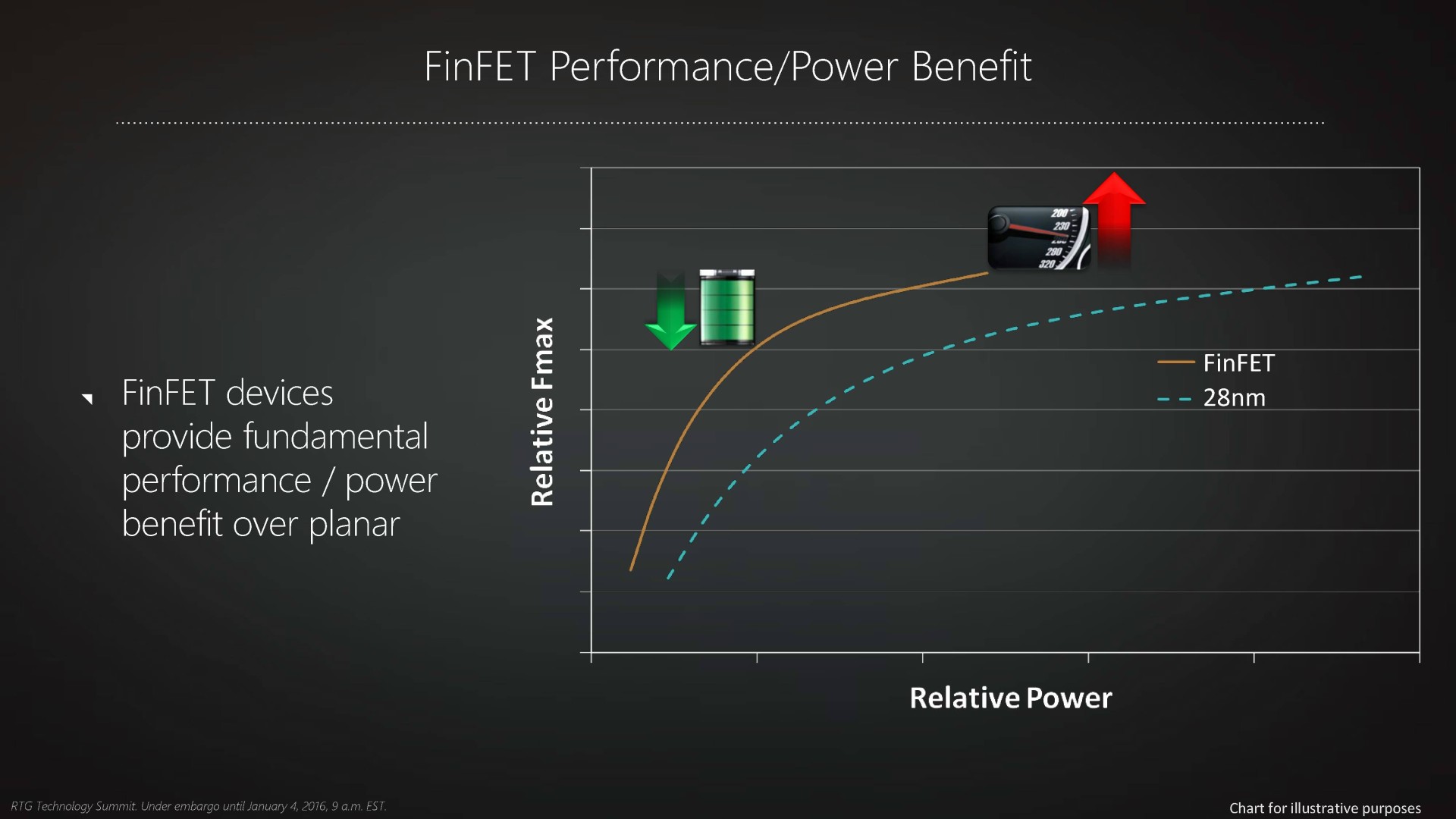

Autant, voire plus, que la finesse de gravure, c'est ainsi le passage au FinFET qui autorise une avancée significative dans les performances des transistors, ce qui peut se traduire par un gain de fréquence, une nette réduction de la consommation ou un mélange de ces deux points selon le positionnement de la puce. Autre avantage selon AMD, le FinFET permet d'obtenir un comportement plus homogène de l'ensemble des transistors, ce qui réduirait la variabilité dans les échantillons produits.

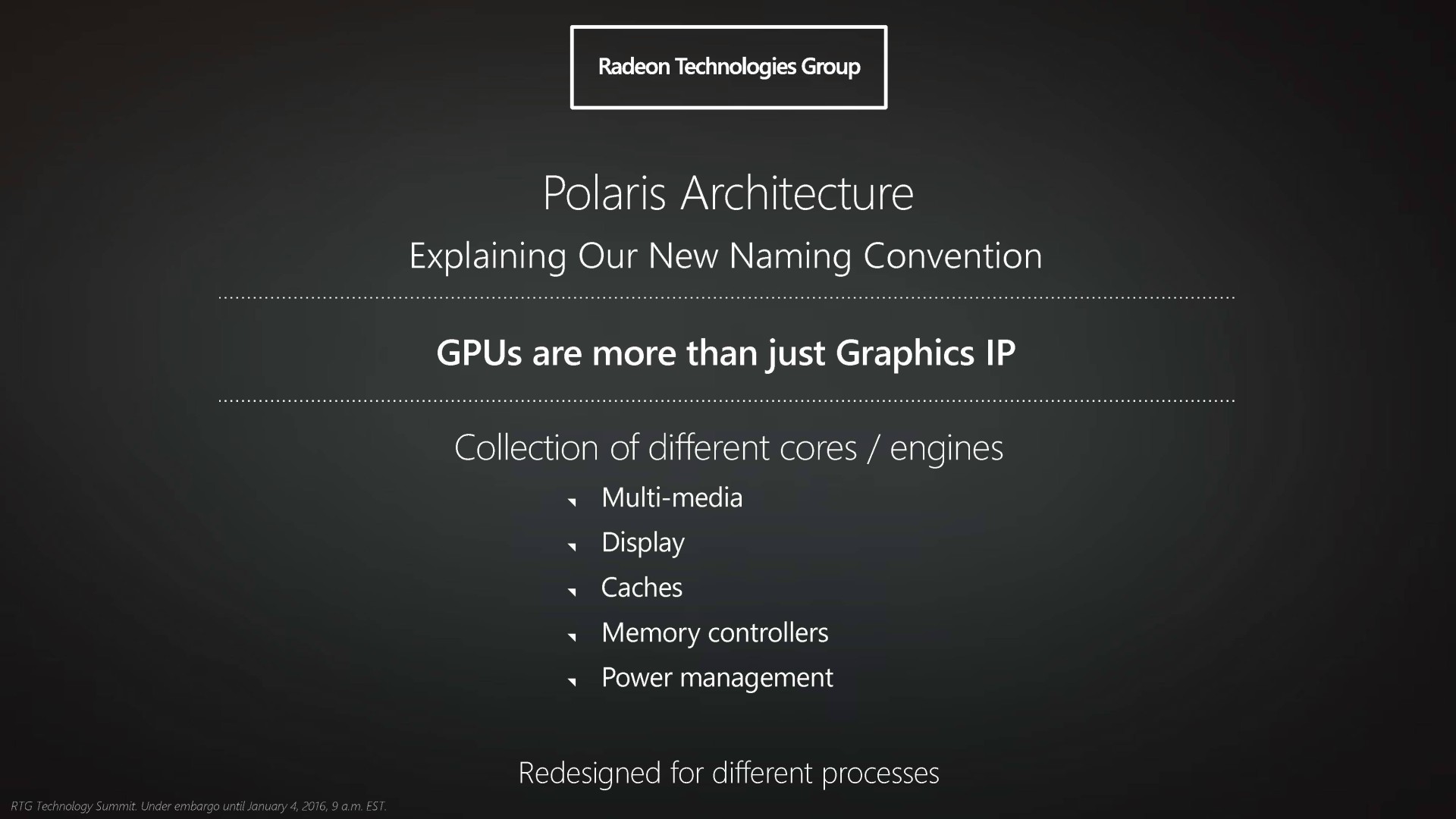

Comme c'est traditionnellement le cas pour les Radeon, c'est lors de ce changement de process qu'AMD va introduire une évolution significative de son architecture GPU, sur laquelle le Radeon Technology Group va bien entendu vouloir communiquer. Et pour cela il faut pouvoir lui mettre un nom.

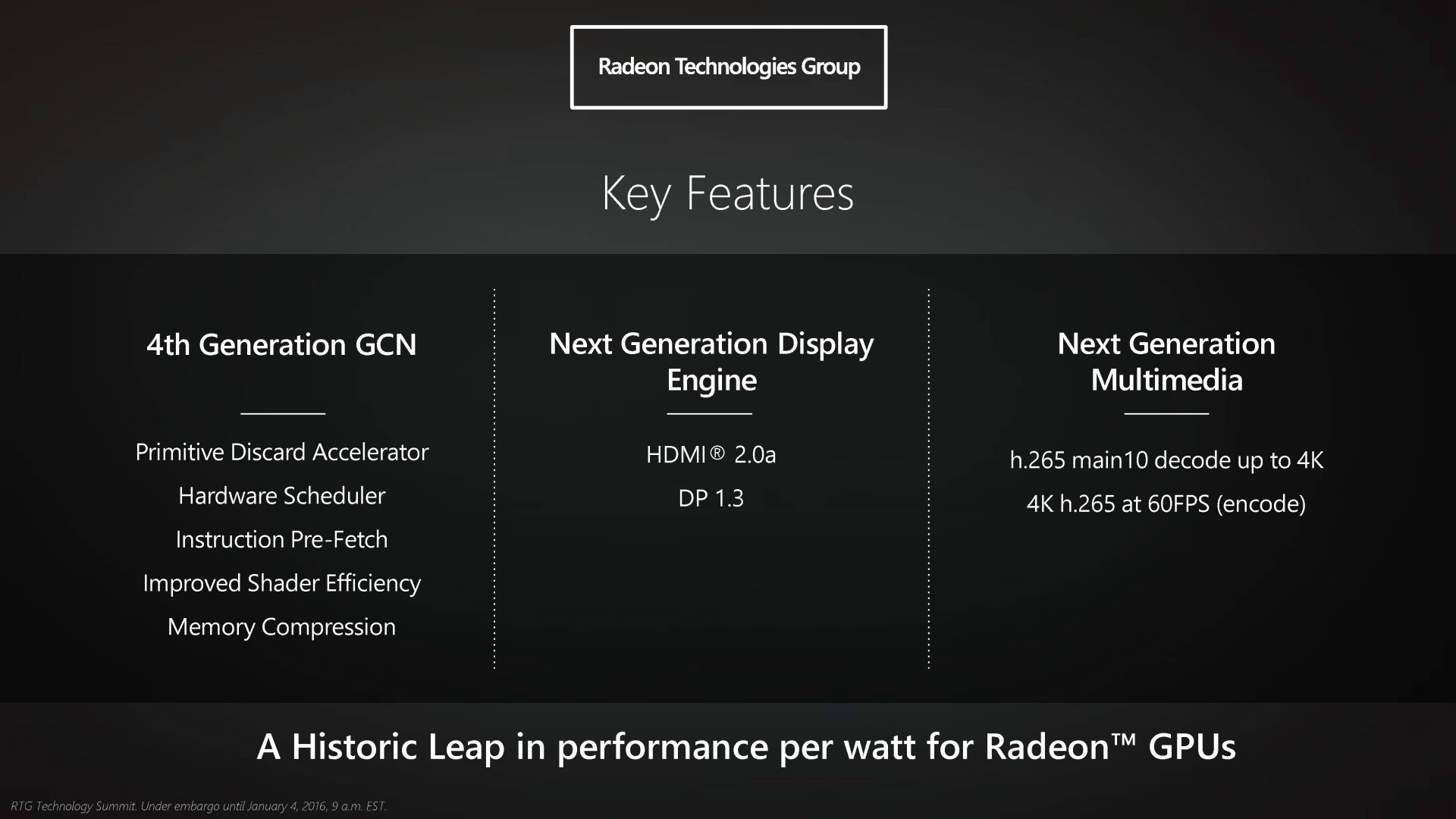

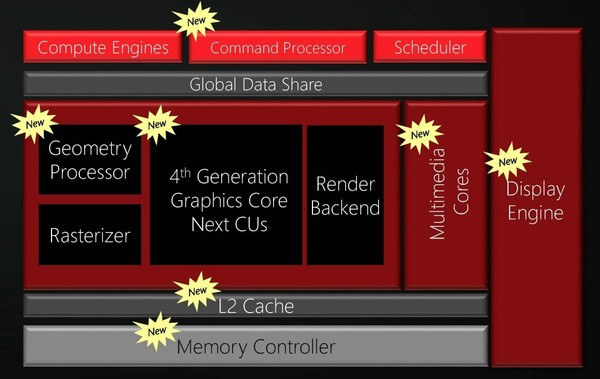

La nomenclature des architectures GPU d'AMD, ou plutôt son absence, a été source de confusion ces dernières années. En l'absence de communication d'AMD, nous avons ainsi fait référence à GCN 1.1 et GCN 1.2 pour parler des petites évolutions apportées depuis la Radeon HD 7970 de décembre 2011. AMD préfère cependant concentrer le terme GCN sur les unités de calcul du GPU (ses "curs"), d'autres éléments du GPU pouvant évoluer indépendamment. Polaris représente ainsi le nom global de la nouvelle architecture et GCN 4 la nouvelle version de ses unités d'exécution (après GCN 1 / 1.0, GCN 2 / 1.1 et GCN 3 / 1.2).

Raja Koduri, qui dirige Le Radeon Technology Group, nous a indiqué vouloir faire en sorte que les cartes graphiques qui embarqueront un GPU de type Polaris soient clairement identifiables. Pragmatique et réaliste, il est bien conscient qu'avec une éventuelle future gamme de cartes graphiques, il pourra être difficile pour ses équipes de résister à la tentation d'y intégrer d'anciens GPU. Il sera ainsi important de permettre aux GPU Polaris d'être mis en avant de manière explicite.

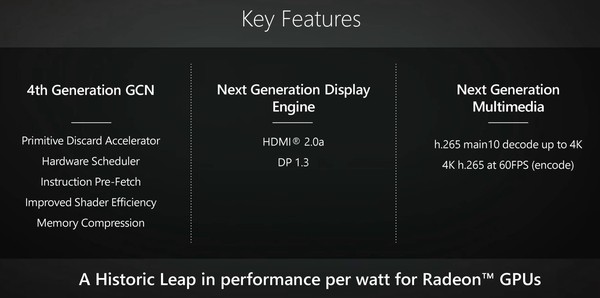

Avec Polaris, à peu près tous les blocs du GPU vont être mis à jour. Nous vous avons déjà parlé de l'aspect affichage et vidéo le mois passé. Pour rappel, les GPU Polaris supporteront le HDMI 2.0a, le DisplayPort 1.3 et le décodage des vidéo 4K en H.265.

Les processeurs de commandes (grahiques et compute), les processeurs géométriques, le cache L2 et le contrôleur mémoire seront également revus pour accompagner le passage aux Compute Units (CU) de type GCN de 4ème génération. Sur ce dernier point AMD précise que Polaris pourra supporter soit un bus GDDR5 soit un bus HBM, suivant les GPU.

Malheureusement, AMD en dit très peu sur les évolutions et ne donne que ces quelques maigres détails :

AMD indique tout d'abord que le cur de l'architecture a été amélioré pour une meilleure efficacité énergétique. Comme Nvidia a commencé à le faire à partir de la génération Kepler, nous pouvons supposer qu'AMD va essayer de ne plus avoir besoin d'une logique d'ordonnancement complexe et gourmande à l'intérieur des CU, là où le comportement d'une suite de certaines instruction est totalement déterministe et peut donc se contenter d'un ordonnancement statique préparé lors de la compilation.

AMD parle également d'amélioration des ordonnanceurs matériels, mais cette fois nous supposons qu'ils ne font pas référence aux CU mais au front-end et aux tâches globales initiées par les processeurs de commandes. Il s'agit ainsi probablement d'améliorations destinées au support du multi-engine de Direct3D 12. Il est également question de nouveaux modes de compression. Il pourrait s'agir de la compression ASTC, coûteuse à implémenter (mais le 14nm règle ce problème) et qu'AMD et Nvidia avaient évité jusqu'ici, contrairement aux concepteurs de GPU pour SoC pour lesquels quelques transistors de plus ne sont jamais trop chers payés pour économiser de la bande passante mémoire et de l'énergie.

Enfin, AMD mentionne un Primitive Discard Accelerator, soit un système d'éjection des triangles masqués du pipeline de rendu. Pour rappel, statistiquement, à peu près la moitié des triangles d'un objet tournent le dos à la caméra et peuvent être éjectés du rendu dès que cet état est confirmé. Pouvoir le faire rapidement permet de booster les performances géométriques en situation réelle.

Actuellement, les moteurs géométriques des Radeon ne sont pas capables d'effectuer cette tâche plus rapidement que le rendu d'un triangle, contrairement aux GeForce qui en profitent pour se démarquer dans certaines scènes, notamment quand la tesselation génère de nombreux triangles masqués. Avec Polaris, AMD devrait enfin combler ce déficit, probablement en doublant le nombre de moteurs d'éjection des primitives par moteur de rastérisation (Nvidia a opté pour une autre approche en décentralisant une partie du traitement géométrique mais nous ne nous attendons pas à ce qu'AMD suive cette voie).

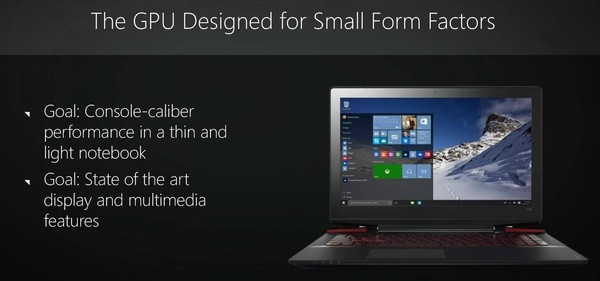

Pour introduire Polaris, contrairement à ce qui se passe habituellement (à l'exception de Maxwell 1 et des GTX 750), AMD met en avant non pas son futur haut de gamme mais un petit GPU prévu pour les PC compacts et pour les portables. Il est équipé de mémoire GDDR5. Nous n'avons pas encore de nom pour ce GPU et n'avons pu l'apercevoir que brièvement sans pouvoir en prendre une photo. Tout juste de quoi apercevoir qu'il s'agit effectivement d'une petite puce et d'un packaging compact.

Sans confirmer que ce serait le premier GPU Polaris disponible, AMD a indiqué que ce petit GPU était important pour sa division graphique, qu'il serait lancé mi-2016 et qu'il serait fabriqué en 14nm chez GlobalFoundries. En précisant ne pas exclure que d'autres GPU soient fabriqués ailleurs, chez Samsung (probablement) ou chez TSMC (de moins en moins probable).

Au niveau de ses spécifications, nous ne saurons rien. Il faudra encore patienter quelque peu, le but d'AMD aujourd'hui étant de nous mettre l'eau à la bouche pour nous faire patienter quelques mois de plus.

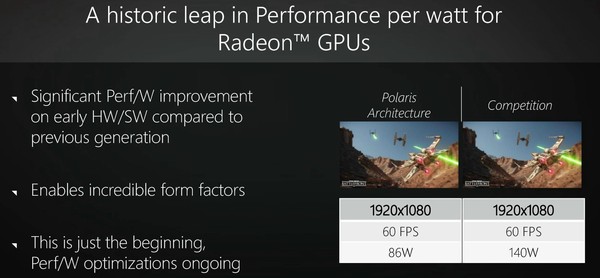

Nous avons par contre pu voir ce GPU en action dans une version alpha lors d'un événement presse organisé il y a quelques semaines. AMD a voulu illustrer les gains d'efficacité énergétique apportés par Polaris par rapport à un GPU Maxwell, déjà très efficace. Des chiffres à prendre avec des pincettes, puisqu'ils restent dans le fond assez vagues et avec des conditions de mesure discutables, mais qui font état d'une progression fulgurante du rendement de l'architecture GCN.

Un système équipé d'un petit GPU Polaris est ainsi capable de maintenir 60 fps dans Star Wars Battlefront avec une consommation totale mesurée à la prise de 86W là où un même système équipé d'une GTX 950 demande 140W. Difficile d'en déduire exactement la consommation GPU et ce gain peut en partie être lié à la combinaison d'une puissance GPU supérieure avec un V-Sync à 60 Hz qui permet de rester à une plus faible fréquence, d'ailleurs le GPU utilisé est configuré à 850 MHz pour 0,8375v seulement. Mais de toute évidence Polaris en 14nm va enfin permettre à AMD de faire mieux que Maxwell en 28nm.

AMD tient d'ailleurs à préciser que cette démonstration a été effectuée avec un support partiel de Polaris par les pilotes. Les gains d'efficacité proviennent ainsi uniquement du 14nm et des CU GCN 4, le support des nouveaux mécanismes dédiés à économiser de l'énergie n'ayant pas encore été implémenté.

Bien entendu, les GPU Polaris n'auront pas simplement affaire aux GPU Maxwell actuels mais bien aux GPU Pascal et peut-être à de petits GPU Maxwell 2 fabriqués en 16/14nm. Et il est beaucoup trop tôt pour savoir comment s'opposeront ces futurs concurrents. Pour la première fois depuis très longtemps, il est d'ailleurs intéressant de noter qu'un élément tiers pourra venir semer le trouble dans le combat AMD vs Nvidia : les fondeurs. En effet, il semble de plus en plus probable qu'AMD exploite principalement les process 14nm de GlobalFoundries et Samsung alors que Nvidia exploiterait plutôt le 16nm de TSMC. Si l'un de ces process s'avère meilleur que l'autre, le fabricant de GPU qui aura misé sur le bon cheval s'en trouvera mécaniquement avantagé même si le process ne fait pas tout.

Vous retrouverez la présentation complète ci-dessous :

Samsung en sus de GloFo pour le 14nm AMD ?

C'est officiel depuis quelques mois, une partie au moins des nouveaux produits AMD de 2016 côté GPU comme CPU seront produits par GlobalFoundries en utilisant le process 14nm LPP développé par Samsung.

Selon ETNews , AMD ne se contenterait pas d'utiliser les services de GloFo mais ferait également appel à Samsung pour fabriquer ses puces sur ce process qui est commun au deux fondeurs. La production devrait débuter au second trimestre, avec une disponibilité autour de la mi-2016 donc, et concerner initialement les GPU avant l'arrivée de Zen sur les chaines de fabrication un peu plus tard.

Cette nouvelle est assez étonnante puisqu'en vertu des accords qui ont fait suite à la revente de la branche fonderie d'AMD, ce dernier dispose d'accord contractuels avec GlobalFoundries assez contraignants sur les volumes. Soit AMD a réussi à renégocier ces contrats, à la faveur par exemple d'un retard de GloFo pour la mise en place du process, soit il compte atteindre des volumes de commande bien supérieurs à ceux prévus.