Les derniers contenus liés aux tags Intel et 16/14nm

Afficher sous forme de : Titre | FluxDes Core M en fin de vie avant leur lancement

Intel précise son process 14nm

Intel Broadwell : +5% d'IPC et TDP de 5 watts

Broadwell en fin d'année seulement (et encore)

Le 20nm en production chez TSMC

12nm et EUV à 7nm pour TSMC

Des détails sur le 7nm à l'ISSCC 2017

Intel abandonne le Tick-Tock, confirme Kaby Lake

Intel densifie sa SRAM 14nm et parle du 10 et 7nm

Intel lance les Core M, 1ers Broadwell 14nm

12nm et EUV à 7nm pour TSMC

TSMC a publié hier ses résultats financiers pour le dernier trimestre 2016. Le fondeur taiwannais a annoncé pour ce trimestre un revenu brut de près de 7.8 milliards d'euros, en hausse de 28.8% par rapport à la même période sur l'année précédente. Sur la totalité de l'année 2016, TSMC aura augmenté son revenu de 12.4% par rapport à 2015.

Pour 2017, TSMC s'attend à voir ses revenus progresser de "seulement" 5 à 10% (ce qui n'a pas manqué de décevoir les analystes financiers). Lors de la présentation des résultats, quelques informations supplémentaires ont été données.

Morris Chang, Chairman de TSMC s'est lancé dans quelques prédictions pour le marché 2017, s'attendant à voir le marché des smartphones grimper de 6% en unités, et celui du PC se contracter de 5% en unités également (il envisage également un déclin de 7% sur les tablettes tout en voyant le marché Internet of Things progresser de 34%).

Sur le 16/14nm, Morris Chang estime que la part de marché de TSMC est entre 65 et 70%, en dessous de ses attentes (TSMC dispose encore de 80% du marché sur le 28nm par exemple). Toujours poétique, le Chairman voit dans le 10 et le 7nm un "ciel bleu" par rapport à la compétition.

Quelques détails plus techniques ont été donnés, notamment par rapport à un "12nm" qui avait été évoqué ici ou là dans la presse. En pratique, TSMC travaille sur une nouvelle version de son process 16nm (une quatrième après les 16FF, 16FF+ et 16FFC) qui incorpore des améliorations importantes de densité. L'appellation commerciale exacte n'a pas été donnée, et on ne sait pas exactement quand elle sera disponible. On s'attendra dans quelques semaines à une annonce officielle, même si TSMC à confirmé aujourd'hui l'existence de ce "12nm".

Pour le 10nm, si le début de production est bien en cours, le gros du volume se situera sur la seconde partie de l'année (coïncidant avec le lancement des prochains iPhones dont le SoC utilisera le 10nm TSMC).

Sur le 7nm, plus de 20 sociétés travailleraient déjà sur des designs pour l'année prochaine, un chiffre qui devrait doubler dans l'année. Sur la question du 7nm en lui même, nous nous étions interrogés sur la manière dont le constructeur augmenterait la densité. Pour rappel, TSMC s'engage à lancer la production du 7nm dès la fin de l'année, il s'agira du node qu'utiliseront la majorité de ses clients, le 10nm devrait avoir une durée de vie courte et être réservé à quelques gros clients.

Le 10nm rappelle d'une certaine manière le 20nm de TSMC, lui aussi utilisé par des gros clients uniquement avant un passage rapide au 16nm. Cependant, avec une augmentation de la densité de 1.63x entre le 10 et le 7nm, la recette utilisée est plus complexe que pour le passage 20/16nm (qui ne proposait qu'une augmentation de densité de 1.15x). Nos confrères de SemiWiki, très au fait des détails, ont confirmé il y a quelques jours que des changements sur les tailles minimales des cellules sont en grande partie à l'origine des gains de densité et que pour réduire les coûts, TSMC évitera au maximum de généraliser le quadruple patterning (SAQP). Le 10 et le 7nm auront donc bel et bien des similarités techniques.

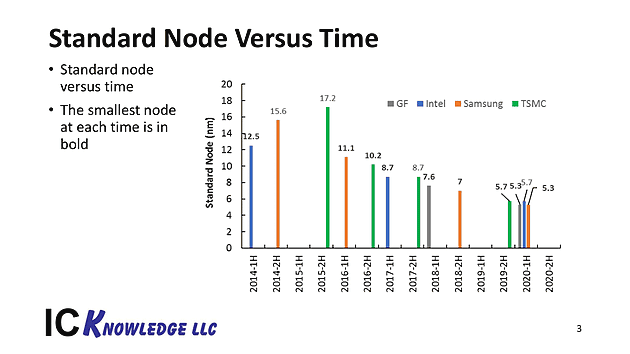

Pour essayer d'y voir un peu plus clair, et étant donné que plus aucun constructeur ne suit de règles équivalentes pour parler de densité, SemiWiki a publié ce graphique intéressant qui montre une "estimation" de la densité comparée de tous les fondeurs :

D'après SemiWiki, le 10nm d'Intel et le 7nm de TSMC auraient, après ajustement, une densité comparable. Il s'agit bien entendu d'estimations qui valent ce qu'elles valent, vous pouvez retrouver l'explication de la formule utilisée ici , mais elles donnent un bon ordre d'idée de ce à quoi il faut s'attendre (un seul bémol à cette analyse : les prévisions concernant GlobalFoundries nous semblent excessivement optimistes, en grande partie à cause des annonces de GlobalFoundries qui nous paraissent déconnectées de leur capacité d'exécution ces dernières années).

En pratique le 10nm de TSMC disposera tout de même d'une meilleure densité que l'actuel 14nm d'Intel, TSMC pourra donc se targuer d'avoir dépassé Intel côté process lorsque les premiers produits 10nm seront disponibles plus tard dans l'année. Et si Intel reprendra l'avantage avec "son" 10nm, TSMC sera effectivement - et pour la première fois - à parité dès la fin de l'année en lançant la production de son 7nm. Une situation qui durera un moment, et pour la première fois les constructeurs "fabless" pourront disposer d'un process équivalent en densité à celui d'Intel.

On notera enfin, concernant le 7nm, que TSMC a confirmé qu'ils inséreront l'EUV au bout d'un an de production à 7nm (soit fin 2018) pour créer une nouvelle version du 7nm (à l'image des multiples 16nm). Des propos plutôt optimistes concernant la lithographie EUV qui sera, Mark Liu le rappelle, indispensable à 5nm. Et un timing qui coïncide exactement avec le lancement de la production du 7nm de Samsung qui utilisera elle, dès le début, l'EUV !

Des détails sur le 7nm à l'ISSCC 2017

La conférence ISSCC (International Solid-State Circuits Conference) se tiendra pour son édition 2017 du 5 au 9 février à San Francisco, et nos confrères d'EEtimes ont eu accès à l'avant programme.

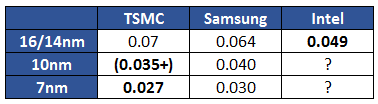

Comme tous les ans les acteurs du milieu des semi conducteurs y présenterons leurs nouveautés, et l'on notera que TSMC et Samsung présenterons leurs cellules SRAM (utilisées notamment pour la mémoire cache dans les puces). L'année dernière, Samsung avait proposé deux versions distinctes pour son process 10nm, optimisées pour la densité ou les performances, de 0.040 µm² et 0.049 µm².

D'après nos confrères, TSMC présentera une cellule SRAM 7nm de seulement 0.027µm², tandis que Samsung présentera une cellule SRAM 7nm de 0.030µm², mais fabriquée en EUV. D'après Samsung, l'EUV permettrait de diminuer la tension minimale nécessaire de 39.9mV (TSMC indique aussi des optimisations basse tension, on attendra la conférence pour comparer l'impact ou non de l'EUV).

La SRAM est un composant fondamental des puces et sa taille permet en général de se donner une bonne idée des process. Cependant il faut être assez méfiant, les constructeurs annonçant parfois des "records" de densité qu'ils n'utilisent pas forcément en production. Nous avons rapporté dans le tableau ci dessous les chiffres les plus bas (correspondant aux bibliothèques "hautes densité") pour TSMC, Samsung et Intel :

Par rapport au tableau, on notera qu'Intel n'utilise pas cette SRAM haute densité dans ses processeurs, mais de la SRAM 0.059 µm². Même en prenant cela en compte, Intel garde la meilleure densité à 16/14nm pour la SRAM. Le constructeur ne fournit pas encore d'infos sur ses futurs process.

TSMC n'a pas donné non plus de chiffre exact pour son 10nm, estimant simplement 50% de réduction par rapport à son 16nm sur la SRAM, ce qui nous vaut un chiffre entre parenthèses. Selon toutes vraisemblances, et conformément aux autres annonces sur la densité (2.1x d'après le constructeur), on estimera que TSMC devrait avoir une SRAM d'une taille légèrement inférieure à celle de Samsung.

Intel ne devrait pas effectuer d'annonce sur ce sujet lors de l'ISSCC, ce qui est assez dommage. Le constructeur devrait présenter les FPGA Altera Stratix 10 (14nm) tandis qu'AMD proposera une présentation plus en détails de Zen.

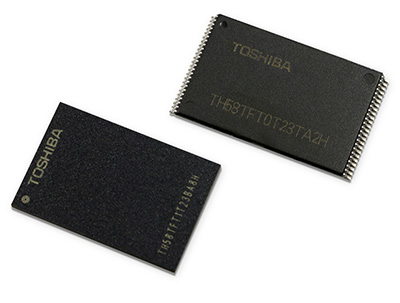

On notera aussi que Western Digital/Toshiba, ainsi que Samsung, présenterons des puces 3D NAND 512 Gbit TLC 64 couches. Dans le cas de Samsung, cette puce avait été annoncée cet été, plus de détails techniques devraient être disponibles. Pour Western Digital/Toshiba, cette puce avait été évoquée cet été comme objectif.

On notera que nos confrères pointent à raison un grand absent : une fois de plus, ni Intel, ni Micron, n'effectueront de présentation technique de leur mémoire 3D Xpoint !

Intel abandonne le Tick-Tock, confirme Kaby Lake

En marge de l'annonce de ses résultats financiers, la conférence dédiée aux analystes a été l'occasion pour Intel de confirmer ce dont l'on se doutait depuis un long moment : le 10nm du constructeur ne sera pas à l'heure.

En marge de l'annonce de ses résultats financiers, la conférence dédiée aux analystes a été l'occasion pour Intel de confirmer ce dont l'on se doutait depuis un long moment : le 10nm du constructeur ne sera pas à l'heure.

Au milieu de l'annonce de nouveaux retards sur sa roadmap mobile (notamment SoFIA LTE qui est désormais attendu pour la première moitié de 2016), Brian Krzanich a indiqué que la transition d'un node à l'autre ne tenait plus réellement le rythme des 24 mois que le constructeur souhaitait s'imposer, mais que sur les deux générations précédentes, il était plus proche des deux années et demi. En conséquence, la stratégie du Tick-Tock doit s'adapter et il aura confirmé l'arrivée d'un troisième produit 14 nm, Kaby Lake qui sera lancé durant la seconde moitié de 2016 (comme on le pressentait le mois dernier) !

Le CEO d'Intel décrit Kaby Lake comme « bâti sur les fondations de la micro architecture Skylake », mais « avec des améliorations clefs de performances ». Un phrasé relativement vague qui laisse entendre qu'il s'agirait d'un peu plus que d'un « Skylake refresh », sans vraiment s'engager (possiblement un nouveau GPU seulement ?). Le lancement de Cannonlake est lui bel et bien repoussé à la seconde moitié de 2017, en 10nm.

Interrogé (légèrement) sur le sujet par les analystes, Brian Krzanich a qualifié le retard par la complexité croissante de mise au point des process et que les difficultés du 10nm, si elles étaient similaires en pratique à celles rencontrées pour le 14nm, n'étaient pas directement liées au retard du 14nm. Intel est sur le sujet dans une position délicate puisque le constructeur a toujours clamé que le retard du 14nm n'aurait aucun impact sur le 10nm. Selon le CEO, la lithographie continue à être de plus en plus complexe, notamment à cause de l'augmentation des étapes de multi-patterning. En marge de cela, il aura rappelé que le 10nm d'Intel sera une solution sans EUV (le reste de l'industrie ne s'attends pas non plus à disposer de l'EUV pour le 10nm).

Pour le CEO, rajouter Kaby Lake à la roadmap permet d'améliorer la « prévisibilité » pour ses partenaires. Un argument qui ne manque pas d'ironie quand l'on connait l'historique du Tick-Tock chez Intel. La stratégie du Tick-Tock avait été mise en place en interne chez Intel au début des années 2000 par Pat Gelsinger dans le but de mettre de l'ordre dans le développement parfois anarchique des architectures qui a conduit à de nombreux projets et architectures repoussés et abandonnés. En interne, il s'agissait de délimiter clairement le périmètre de deux équipes de développement d'architectures, une située en Oregon et l'autre en Israël. Le tout articulé autour des changements de process tous les deux ans.

Ainsi chaque nouveau passage à un process (65 vers 45 nm, etc) serait un Tick. Une version légèrement modifiée de l'architecture précédente, portée vers le nouveau node (ce que l'on appelle un die shrink), tandis que la « nouvelle architecture », le Tock serait lancé l'année suivante, lorsque le process de fabrication serait arrivé à maturité.

Historiquement, ce n'est qu'avec beaucoup de créativité que le constructeur aura pu compter 24 mois entre chaque node, des retards de plusieurs mois ayant été observés au fil des années mais globalement jusqu'ici Intel s'était imposé de tenir le modèle de deux produits principaux (on met de côté les produits/architecture dédiées spécifiquement à la mobilité) par node sur environ deux ans.

Avec le 14nm le modèle n'était plus tenable, obligeant en 2014 Intel à proposer un Haswell refresh, simple « speed bump » d'Haswell, lancé en juin 2013 en lieu et place de Broadwell. En pratique si Intel s'est targué d'avoir « lancé » le 14nm en 2014, il s'agissait d'un seul processeur, le Core M, qui plus est dans un stepping remplacé avant même sa sortie ! Et pour le desktop, la gamme Broadwell aura été réduite au minimum avec seulement deux modèles, lancés le mois dernier pour tenir les annonces. Avec au final un retard d'un an sur la cadence que s'imposait jusqu'ici Intel.

En pratique Skylake (le tock original 14nm) est toujours attendu pour cette année même si Intel n'a pas encore confirmé de quelle manière s'effectuerait son lancement. Il a été indiqué par Intel qu'une des conséquences du ralentissement de l'activité en Q2 était un inventaire encore important, laissant penser que le constructeur pourrait repousser certains SKU de Skylake. Le lancement des modèles K était prévu pour rappel pour le 5 aout, tandis que le reste de la gamme 4 curs était attendue entre le 30 aout et le 5 septembre. On ne s'étonnerait pas de voir ces références repoussées de plusieurs semaines afin d'écouler les inventaires existants, même si Intel ne l'a pas dit clairement.

On notera également qu'au détour d'une question, Brian Krzanich a confirmé que le 10nm d'Intel utiliserait toujours des FinFET, et non un autre type de structures comme certaines rumeurs avaient pu le laisser entendre. Il a indiqué que le 10nm serait la troisième génération de FinFET d'Intel. A une autre question il a indiqué que des changements de matériaux étaient par contre attendus sans les préciser.

Interrogé enfin sur l'impact de ces retards sur « l'avance » d'Intel en matière de process par rapport au reste de l'industrie, Brian Krzanich s'est voulu rassurant, indiquant que l'avance d'Intel ne diminuerait pas sur le reste de l'industrie. De notre point de vue, il est probable que TSMC, et possiblement Samsung lancent une production en volume autour, voir même un peu avant Intel. Ce qui serait, au moins pour l'image, un véritable drame pour la firme de Santa Clara.

Intel densifie sa SRAM 14nm et parle du 10 et 7nm

Intel profite de la conférence ISSCC (International Solid-State Circuits Conference) qui se tient cette semaine à San Francisco pour effectuer plusieurs annonces autour de ses process de fabrication. Le constructeur a donné à la presse un avant-goût de ses annonces, deux d'entre elles ont particulièrement retenu notre attention.

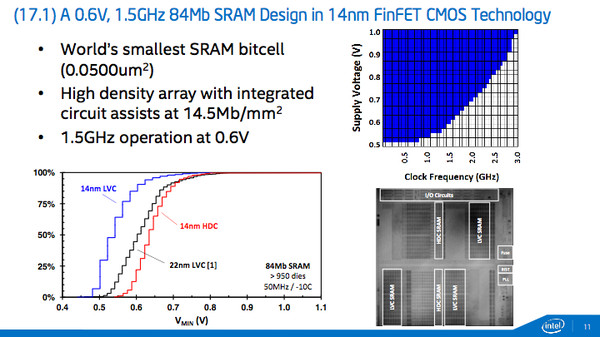

En premier lieu on retiendra la présentation d'un bloc de SRAM particulièrement optimisé pour la densité avec une taille de cellule de seulement 0.0500 µm², un record. Il s'agit d'une amélioration importante par rapport à la dernière présentation du constructeur qui évoquait des tailles de cellules de 0.0588 µm² lors du dernier IEDM fin 2014.

Il s'agit en pratique d'une puce de 84 Mbit (10,5 Mo) de SRAM optimisée pour un fonctionnement à 1.5 GHz à 0.6 Volts, même si en montant la tension d'activation à 1 Volt on peut atteindre 3 GHz. Si elle montre le bond en avant en densité lié au process, cette annonce tient surtout de la performance technique, le constructeur annonçant souvent des cellules de SRAM spécialisées et différentes de ce que l'on retrouve dans les produits commerciaux. Le constructeur avait ainsi annoncé pour le node 22 nm des cellules de 0.092 µm² optimisées pour la densités, mais ce sont des cellules de 0.108 µm² optimisées cette fois ci pour leur rapport performance/puissance qui sont utilisées dans les processeurs.

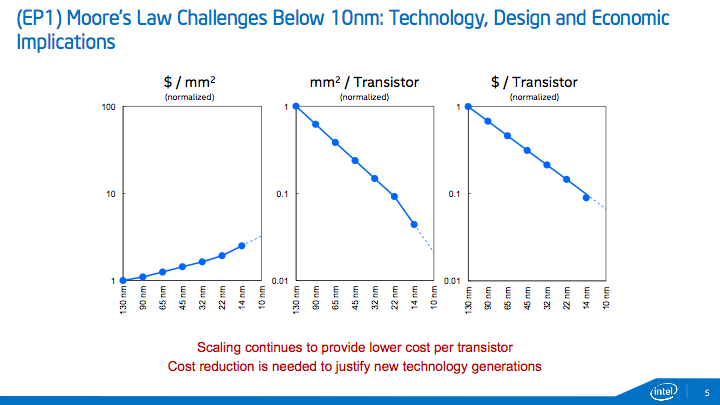

On retiendra enfin la description des challenges rencontrés au delà du 10 nm. Intel se félicite tout d'abord d'avoir atteint un coût par transistor plus faible qu'attendu sur le 14 nm, un chiffre toujours difficile à mettre en perspective qui plus est cette fois-ci avec les retards engendrés et les lancements décalés !

En ce qui concerne le 10nm, il semblerait que le constructeur ait - sans surprise - opté pour sa solution à lithographie à immersion « classique » en 193nm, et non pour une solution EUV comme Mark Bohr nous l'avait déjà indiqué en 2012 à l'occasion d'une interview. En fin d'année dernière TSMC avait également indiqué que l'EUV ne serait pas a l'heure pour leur propre process 10 nm.

Intel ne s'est pas encore étendu sur les changements techniques de son process 10 nm mais il avait été évoqué précédemment un recours plus fort au multiple patterning (exposition multiples). Déjà utilisé sporadiquement sur certaines couches critiques, son utilisation devrait être généralisée.

En ce qui concerne le 7 nm, un changement de la forme des structures (remplacer par exemple les FinFET par des microfils) et des matériaux utilisés (par exemple Arséniure de Gallium-Indium [InGaAs] ou Phosphure d'Indium [InP]) est envisagée mais Intel n'est pas encore prêt a livrer les détails de sa recherche.

On notera enfin que le constructeur indique avoir appris de ses problèmes concernant le 14 nm en ajoutant de nouvelles procédures internes pour détecter les problèmes rencontrés, particulièrement autour des masques qui semblent avoir posé beaucoup de problèmes au constructeur et être en partie coupable des retards. Le fondeur annonce qu'il a pour objectif d'avoir une transition vers le 10nm deux fois plus rapide que celle du 14nm, mais vu l'introduction de produits 14nm au compte-goutte 18 à 24 mois après le passage au 22nm on ne sait pas vraiment quels sont l'intervalle et la date de départ pris en compte pour le 14nm. Toujours est-il que le 10nm devrait pour sa part débarquer en 2016 !

Intel lance les Core M, 1ers Broadwell 14nm

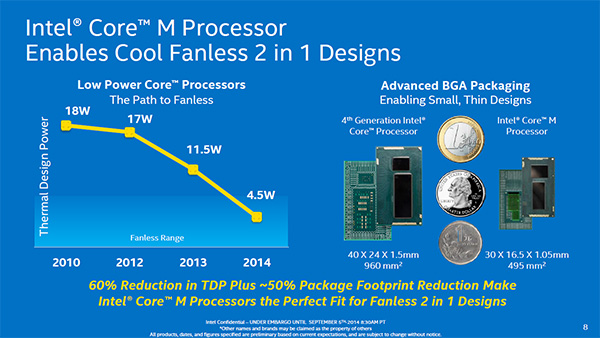

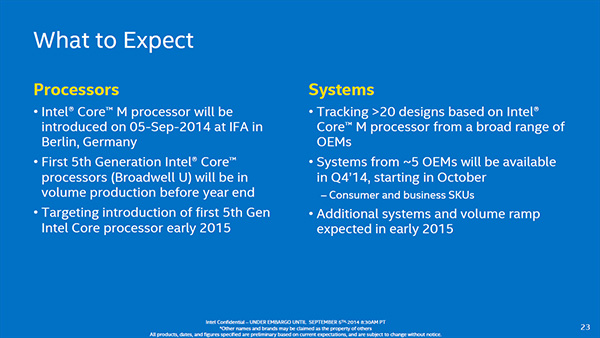

Intel profite de l'IFA pour annoncer officiellement ses processeurs Intel Core M. Pour rappel, il s'agit des premiers modèles utilisant l'architecture Broadwell, et plus précisément de Broadwell-Y.

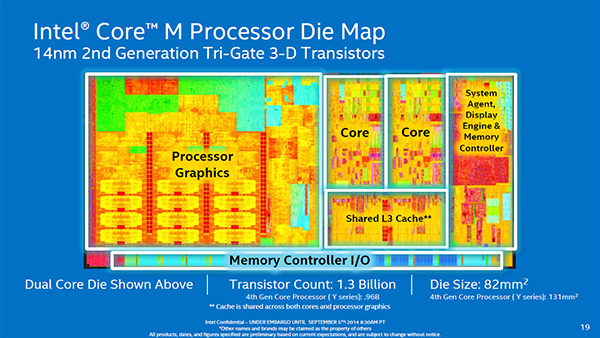

Destiné à l'intégration dans des ordinateurs et tablettes fanless, ces processeurs ont la particularité d'avoir un TDP de 4.5 watts seulement, une avancée importante face aux Haswell-Y qui étaient à 11.5 watts. Un Broadwell-Y intègre pour rappel deux puces, la première gravée en 14nm fait 82mm² et intègre 1,3 milliards de transistors, contre 82mm² et 960 millions pour son prédécesseur. On reste à 2 curs CPU mais le cache L3 passe de 3 à 4 Mo et le HD Graphics de 20 à 24 unités.

L'autre puce est gravée en 32nm, c'est le chipset Broadwell PCH-LP 32nm. Il permet de gérer jusqu'à 4 USB 3.0, 4 SATA 6 Gb/s et gère 12 lignes PCIe Gen2 pouvant être configurées sur 6 ports au maximum, des fonctionnalités réduites mais bien suffisantes vu la cible des Intel Core M.

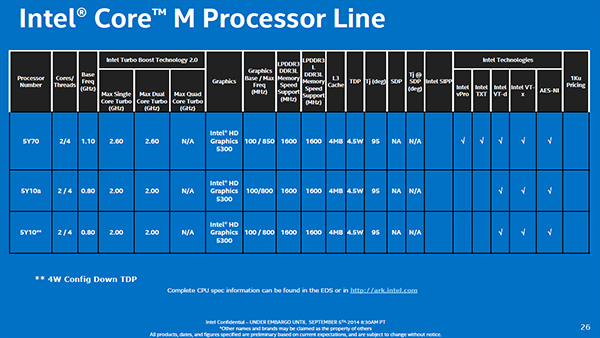

La gamme Core M est déclinée de la sorte :

-Core M-5Y70 : 2 curs à 1.1-2.6 GHz, HD Graphics à 100-850 MHz

-Core M-5Y10a : 2 curs à 0.8-2.0 GHz, HD Graphics à 100-800 MHz

-Core M-5Y10 : 2 curs à 0.8-2.0 GHz, HD Graphics à 100-800 MHz

Le 5Y70 est le seul à supporter Intel vPro et Intel TXT, la différence entre 5Y10a et 5Y10 se limite au TDP qui est configurable sur le 5Y10, on peut ainsi le passer de 4.5 à 4 watts si nécessaires. Les deux curs disposent de l'Hyperthreading. Côté tarif il est question de 281$ quelque soit le modèle.

Par rapport aux Core i3 Haswell avec un TDP de 11.5W, on note que la baisse du TDP ne se fait pas seulement par le passage au 14nm puisque les fréquences dites de base sont revues à la baisse. En effet sur un Core i5-4300Y les fréquences CPU varient entre 1.6 et 2.3 GHz, contre 200 à 850 MHz pour le HD Graphics.

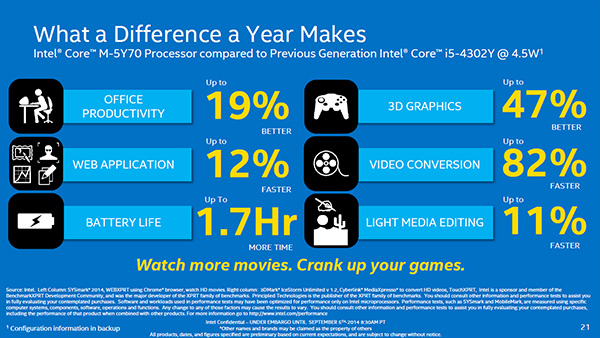

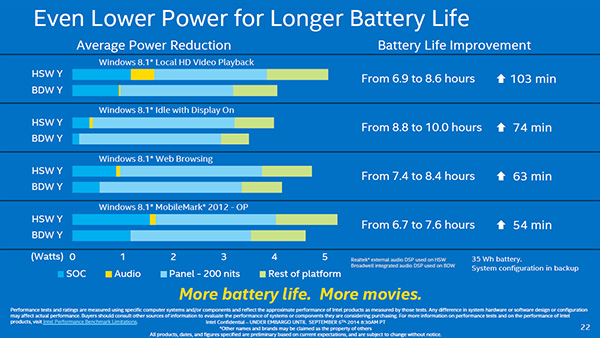

Pour mettre en avant les gains de performances Intel compare à un Core i5-4302Y et annonce que le Core M-5Y70 serait alors 11 à 18% côté CPU (SYSmark 2014, WEBXRPT, TouchXPRT), 58% plus rapide sous 3DMark IceStorm et 82% en conversion vidéo (sous Cyberlink MediaXpresso avec QuickSync). Côté autonomie les gains seraient également là avec 54 à 103 minutes de mieux. Dans le détail ont voit qu'en lecture HD une grosse partie du gain provient de la partie audio désormais prise en charge en interne par le chipset au lieu d'être confiée à un codec HD Audio externe. Seul problème, l'i5-4302Y dispose d'un TDP de 11.5W et d'un SDP de 4.5W, mais dans les configurations de test Intel indique qu'il a un TDP de 4.5W... est-ce que le processeur est bridé artificiellement à ce niveau pour les tests ?

Difficile d'en tirer des conclusions définitives mais sur le papier Intel semble avoir réussi à amener son architecture x86 "hautes performances" sur le marché de la basse consommation ou il ne proposait jusqu'alors que Bay Trail, même si cela n'est pas sans concession côté fréquence. Il est d'ailleurs probable qu'en charge CPU multithread un N3540 (4 curs à 2.16-2.66 GHz, TDP de 7.5w) ne soit pas si éloigné que ça, mais les Core M auront un avantage net en charge single thread et côté iGPU.

Intel met en avant les Core M pour une intégration au sein des "2 en 1", ces portables qui peuvent également faire office de Tablette, avec par exemple un format 11.6" et 8mm d'épaisseur. Les premières machines devraient être disponibles chez 5 fabricants au dernier trimestre, les premières dès octobre. A noter que nous n'avons pas encore eu de retour d'Intel par rapport au PCN publié il y a peu qui annonçait la fin de vie de ces Core M, a priori en préparation d'une nouvelle révision qu'Intel n'a pas décidé d'attendre pour le lancement.

Pour le reste de la gamme Broadwell il va par contre falloir patienter, puisque les premiers processeurs Intel Core de 5è génération ne sont pas attendus avant début 2015. Il s'agira de Broadwell-U, un dual core plus classique avec notamment un TDP et des fréquences en hausse, un HD Graphics plus musclé et un chipset externe. Les Broadwell-H, c'est-à-dire les 4 curs, ne sont même pas mentionnés ce qui tend à confirmer les rumeurs parlant d'un lancement aux alentours de la mi-2015 seulement !