Intel densifie sa SRAM 14nm et parle du 10 et 7nm

Publié le 23/02/2015 à 14:25 par Guillaume Louel

Intel profite de la conférence ISSCC (International Solid-State Circuits Conference) qui se tient cette semaine à San Francisco pour effectuer plusieurs annonces autour de ses process de fabrication. Le constructeur a donné à la presse un avant-goût de ses annonces, deux d'entre elles ont particulièrement retenu notre attention.

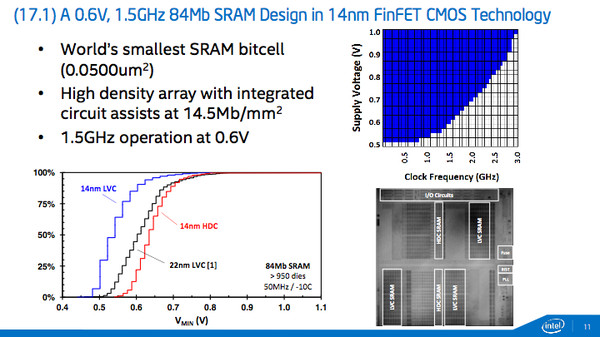

En premier lieu on retiendra la présentation d'un bloc de SRAM particulièrement optimisé pour la densité avec une taille de cellule de seulement 0.0500 µm², un record. Il s'agit d'une amélioration importante par rapport à la dernière présentation du constructeur qui évoquait des tailles de cellules de 0.0588 µm² lors du dernier IEDM fin 2014.

Il s'agit en pratique d'une puce de 84 Mbit (10,5 Mo) de SRAM optimisée pour un fonctionnement à 1.5 GHz à 0.6 Volts, même si en montant la tension d'activation à 1 Volt on peut atteindre 3 GHz. Si elle montre le bond en avant en densité lié au process, cette annonce tient surtout de la performance technique, le constructeur annonçant souvent des cellules de SRAM spécialisées et différentes de ce que l'on retrouve dans les produits commerciaux. Le constructeur avait ainsi annoncé pour le node 22 nm des cellules de 0.092 µm² optimisées pour la densités, mais ce sont des cellules de 0.108 µm² optimisées cette fois ci pour leur rapport performance/puissance qui sont utilisées dans les processeurs.

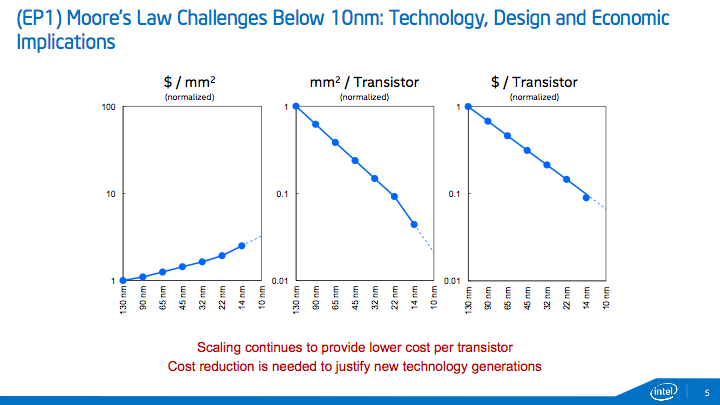

On retiendra enfin la description des challenges rencontrés au delà du 10 nm. Intel se félicite tout d'abord d'avoir atteint un coût par transistor plus faible qu'attendu sur le 14 nm, un chiffre toujours difficile à mettre en perspective qui plus est cette fois-ci avec les retards engendrés et les lancements décalés !

En ce qui concerne le 10nm, il semblerait que le constructeur ait - sans surprise - opté pour sa solution à lithographie à immersion « classique » en 193nm, et non pour une solution EUV comme Mark Bohr nous l'avait déjà indiqué en 2012 à l'occasion d'une interview. En fin d'année dernière TSMC avait également indiqué que l'EUV ne serait pas a l'heure pour leur propre process 10 nm.

Intel ne s'est pas encore étendu sur les changements techniques de son process 10 nm mais il avait été évoqué précédemment un recours plus fort au multiple patterning (exposition multiples). Déjà utilisé sporadiquement sur certaines couches critiques, son utilisation devrait être généralisée.

En ce qui concerne le 7 nm, un changement de la forme des structures (remplacer par exemple les FinFET par des microfils) et des matériaux utilisés (par exemple Arséniure de Gallium-Indium [InGaAs] ou Phosphure d'Indium [InP]) est envisagée mais Intel n'est pas encore prêt a livrer les détails de sa recherche.

On notera enfin que le constructeur indique avoir appris de ses problèmes concernant le 14 nm en ajoutant de nouvelles procédures internes pour détecter les problèmes rencontrés, particulièrement autour des masques qui semblent avoir posé beaucoup de problèmes au constructeur et être en partie coupable des retards. Le fondeur annonce qu'il a pour objectif d'avoir une transition vers le 10nm deux fois plus rapide que celle du 14nm, mais vu l'introduction de produits 14nm au compte-goutte 18 à 24 mois après le passage au 22nm on ne sait pas vraiment quels sont l'intervalle et la date de départ pris en compte pour le 14nm. Toujours est-il que le 10nm devrait pour sa part débarquer en 2016 !

Vos réactions

Contenus relatifs

- [+] 27/04: Le 10nm d'Intel (encore) retardé, l...

- [+] 27/04: AMD Vega 7nm en labo, Zen 2 échanti...

- [+] 08/03: GlobalFoundries : 12nm, 7nm et EUV

- [+] 30/01: TSMC confiant sur l'EUV en volume p...

- [+] 30/01: L'activité d'Intel poussée par le s...

- [+] 09/01: CES: Silence sur l'après Pascal che...

- [+] 29/11: Samsung lance la production en volu...

- [+] 19/10: Samsung annonce la qualification de...

- [+] 21/09: AMD utilisera le 12nm de GloFo en 2...

- [+] 11/09: Un nouveau 14nm chez Samsung