Les contenus liés au tag 16/14nm

Afficher sous forme de : Titre | FluxIntel densifie sa SRAM 14nm et parle du 10 et 7nm

TSMC, résultats et point sur les 20nm, 16nm et 10nm

Le 16nm de TSMC en avance sur son retard

Intel lance les Core M, 1ers Broadwell 14nm

Des Core M en fin de vie avant leur lancement

AMD valide le 14nm LPP de GloFo

GlobalFoundries vient d'annoncer dans un communiqué qu'il avait livré à AMD des puces fonctionnelles gravées avec le process 14nm LPP (Low Power Plus), la version la plus avancée du procédé de fabrication Samsung 14nm FinFet (l'Apple A9 utilisant le 14nm LPE Low Power Early) qui est pour rappel également déployé chez GF.

Le fondeur précise qu'AMD a "taped out" plusieurs produit chez GF en 14nm LPP et qu'il est actuellement en train de valider les échantillons produit. Il semble donc qu'un premier produit ai été validé, GF parlant de "silicon success". AMD indique au passage qu'il compte utiliser le process 14nm LPP sur des produits CPU, APU mais aussi GPU. Jusqu'alors les GPU AMD étaient comme ceux de Nvidia fabriqués par TSMC, mais sachant qu'AMD a toujours des engagements contractuels sur des volumes avec GF qu'il peine à remplir il est logique qu'il favorise ce dernier si le process est à la hauteur. On devrait donc avoir droit en 2016 à une bataille d'architecture entre AMD et Nvidia combinée à une bataille de fondeurs avec d'un côté le 16nm FinFET+ de TSMC et de l'autre le 14nm LPP de Samsung/GlobalFoundries !

GlobalFoundries indique que le 14nm LPP a été qualifié au cours du troisième trimestre pour la production, cette dernière va débuter au cours de ce quatrième trimestre et arrivera à plein débit en 2016, sans plus de précision. Difficile pour le moment de savoir quand les premières puces AMD produites en 14nm LPP seront lancées en 2016, mais il serait étonnant que ce soit avant le second trimestre côté GPU et le dernier trimestre côté CPU. Vivement !

Résultats TSMC, 16 FinFET+ dans l'iPhone 6s

TSMC présentait cette nuit également ses résultats qui, sans trop de surprises, sont bons et au-dessus des estimations. Une des raisons se trouve derrière le fait que TSMC est, contrairement aux spéculations, le fournisseur majoritaire de SoC d'Apple pour l'iPhone 6s. TSMC a également glissé au passage que ces SoC livrés par TSMC étaient bel et bien 16 FinFET+ (la version avancée du process 16nm de TSMC), ce qui explique peut-être l'avantage de consommation en charge lourde que l'on voit dans les versions TSMC des iPhones face aux versions Samsung, comme noté par nos confrères d'Ars Technica .

On aura noté quelques sourires lorsque la question de la différence a été posée clairement à TSMC, le fondeur se contentant de rapporter les propos d'Apple (qui indique 2 à 3% de variations selon les puces en usage normal) et qu'ils étaient « très confiants » sur leur technologie. Dans tous les cas, cela confirme qu'effectivement le 16 FinFET+ de TSMC est déjà prêt, ce qui est une bonne nouvelle pour tous les clients du fondeur !

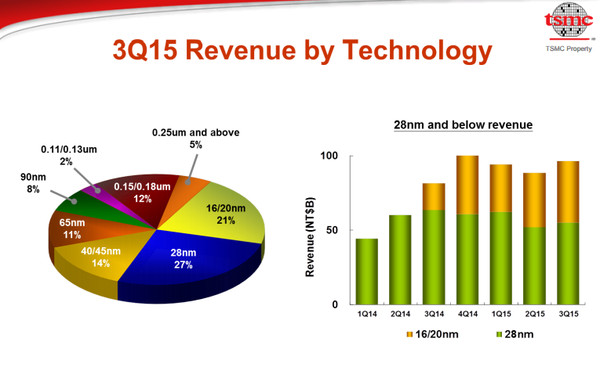

Par rapport au troisième trimestre 2013 les revenus du fondeur sont en hausse de 1.7%. La marge brute est en baisse cependant, principalement suite à la vente de l'activité solaire du groupe. La société mélange les revenus 16 et 20nm dans ses résultats, les deux nodes représentent 21% des revenus de TSMC. La proportion du 16nm devrait augmenter significativement au quatrième trimestre même si la société n'a pas donné de détails. Au second trimestre, le 20nm, utilisé quasi exclusivement par Apple et Qualcomm représentait 20% des revenus de TSMC.

TSMC s'attend à voir ses revenus progresser sur l'année 2015 de 11%, porté par le marché des smartphones qui globalement profiterait d'une hausse de 10% sur l'année quand tous les autres secteurs sont en baisse. La société se félicite de sa place sur le marché haut de gamme qui, s'il n'évolue pas massivement en volume, contient de plus en plus desilicium TSMC.

L'un des co-CEO de TSMC Mark Liu insiste sur le rôle à venir de TSMC sur le marché du « computing » en général, quelque chose qui fait écho aux propos de Morris Chang, le chairman qui au trimestre dernier voyait TSMC jouer un rôle plus important sur les PC portables et les serveurs, mais aussi l'arrivée de SoC dans de nouveaux marchés qui n'existent pas encore. TSMC a indiqué travailler avec certains de ses partenaires sur les automobiles autonomes, nécessitant beaucoup de silicium pour des puces spécialisées dans les traitements d'images pour simuler la vision.

Sur le 10nm, TSMC dit être en bon chemin sur le développement indiquant que le process apportera un gain de densité de 2.1x par rapport au 16 FinFET+, 20% de performances supplémentaires ou 40% d'économie d'énergie à performances égales. Des chiffres qui ont légèrement évolué, plutôt dans le bon sens par rapport à ce qui était indiqué le trimestre dernier (2.2x, +15% et -35% respectivement). TSMC compte freezer la phase de développement ce trimestre et commencer les phases de qualifications avec des premiers tapeout clients attendus au printemps prochain. Des délais agressifs qui correspondent à ce que la société avait promis jusqu'ici.

Pour le 7nm, TSMC sous-entend que le process profitera de l'apprentissage des yields du 10nm. Nous continuons de penser, même si TSMC ne le dit pas clairement, que le BEOL (la partie interconnexion de la puce) du 10 et du 7nm seront communs à l'image de ce qui s'est passé entre le 20 et le 16nm, même si des gains de densités ont été évoqués (mais non quantifiés !). Le développement est lui aussi « en bonne voie » et devrait apporter des gains substantiels de performances face au 10 même s'ils n'ont pas été précisés non plus. Le 7nm sera en tout cas le prochain node « long » (après le 16 FinFET+) ce qui laisse penser qu'effectivement la situation 20/16 se réitèrera en 10/7. Mark Liu a en prime indiqué avoir déjà produit de la SRAM fonctionnelle en 7nm.

L'autre co-CEO de TSMC, C.C. Wei, a indiqué que la demande sur le 20nm était plus faible qu'attendue, en partie du fait de la disponibilité un peu plus tôt que prévue du 16nm. Le fondeur s'attend tout de même à produire deux fois plus de puces 20nm en 2015 qu'en 2014. Cependant la conversion des usines 20nm en 16nm va continuer, le 20nm étant voué à disparaitre. 100 produits de 40 clients sont attendus en 2016. Sur le packaging type InFO (Intergrated Fan-Out Wafer Level Packaging) le fondeur s'attend à ce qu'il soit disponible en 2016 pour ses clients sur son process 16nm.

Les yields 16 FinFET+ continuent en tout cas de battre tous les records internes d'après le constructeur, confirmant que le choix d'avoir utilisé un BEOL commun, même si cela n'apporte pas un gain de densité massif, permet d'être plus rapidement présent sur le marché avec un process performant.

MAJ : A la toute fin du (long !) webcast, TSMC est revenu sur l'EUV, indiquant que durant ces trois derniers mois, les progrès de l'EUV ont été très bon et qu'à compter de janvier, de nouvelles machines devraient être livrées pour préparer le travail sur le 5nm !

L'A9 d'Apple produit par Samsung et TSMC

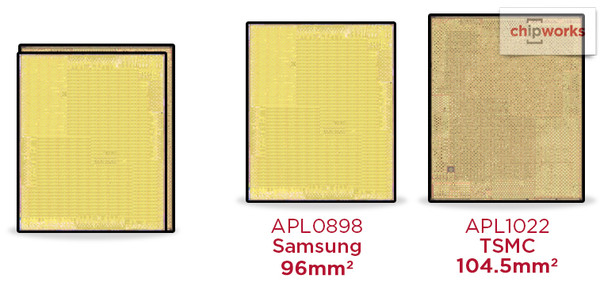

La société Chipworks a confirmé via son blog une semi surprise : l'A9, le SoC ARM custom présent dans l'iPhone 6s d'Apple existe en deux variantes, une produite par Samsung et l'autre par TSMC. Selon Chipworks, ils ont trouvé ces deux puces dans « deux modèles identiques », tandis que iFixit a trouvé la version Samsung dans un iPhone 6s et la version TSMC dans le modèle 6s Plus .

Les deux puces portent une référence différente (APL0898 et APL1022) et mesurent respectivement 96 mm2 et 104.5 mm2 (l'A8 en 20nm mesurait 89mm2 à titre de comparaison). Le nombre de transistor est inconnu, il était de 2 milliards sur l'A8. Le process de Samsung (partagé sous licence avec GlobalFoundries) est un 14nm FinFET tandis que celui de TSMC est un 16nm FinFET même si en pratique les nomenclatures ne veulent plus dire grand-chose. Samsung semble avoir tout de même un avantage de densité, quelque chose que l'on attendait, TSMC avait déjà annoncé dès l'année dernière qu'ils proposeraient une seconde version de leur process 16nm en 2016 (le 16 FinFET Plus) afin d'améliorer la densité et être plus compétitif avec la concurrence.

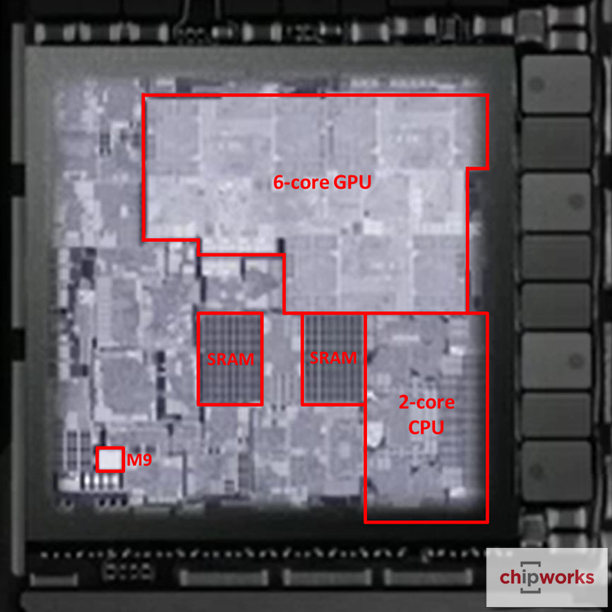

Au-delà de leurs tailles différentes, les puces semblent se comporter de manière similaire dans les premiers benchmarks que l'on a pu croiser, même s'il est encore tôt pour se faire une idée complète. Techniquement l'A9 est un SoC composé pour sa partie CPU d'un dual core basé sur une architecture ARM 64 bit custom et cadencé à 1.8 GHz accompagné de 3 Mo de cache L2. Un GPU issu de chez PowerVR avec « six cores » s'occupe de la partie graphique, le CPU et le GPU partageraient possiblement 8 Mo de cache L3. Apple annonçait +70% de performance CPU et +90% de performances graphiques par rapport à sa génération précédente gravée en 20nm par TSMC, des chiffres qui se vérifient à peu près dans les premiers benchmarks. Le SoC est de type PoP avec 2 Go de mémoire LPDDR4 au-dessus (et l'on notera pour l'anecdote la présence d'un contrôleur NAND PCIe/NVMe dans l'iPhone 6s !)

Si l'on s'attendait à voir Samsung et TSMC produire la nouvelle génération de puces d'Apple, beaucoup pensaient que Samsung aurait récupéré la production de l'A9 et TSMC celle de l'A9X (la version iPad du SoC). En juillet dernier, TSMC avait cependant semé le doute indiquant avoir déjà réalisé ses premières livraisons de puces à ses clients.

Le choix d'utiliser deux process distincts pour produire une même puce est original de la part d'Apple qui n'a toutefois pas les mêmes problèmes que tout le monde. Le volume de l'iPhone (13 millions vendus en un weekend, 200 millions attendus sur l'année) permet à la marque de justifier aisément le cout double de développements séparés pour deux process différents (les process sont incompatibles dans leurs règles et les designs doivent être adaptés pour chaque fondeur).

Cela permet également d'améliorer le volume de disponibilité dès le lancement - un problème particulièrement important sur des process de toute dernière génération, il suffit de regarder la disponibilité anémique des Skylake d'Intel pour s'en convaincre - et de minimiser les problèmes de yields que pourraient avoir l'un ou l'autre de ses fournisseurs.

16nm à l'heure, EUV en retard pour TSMC

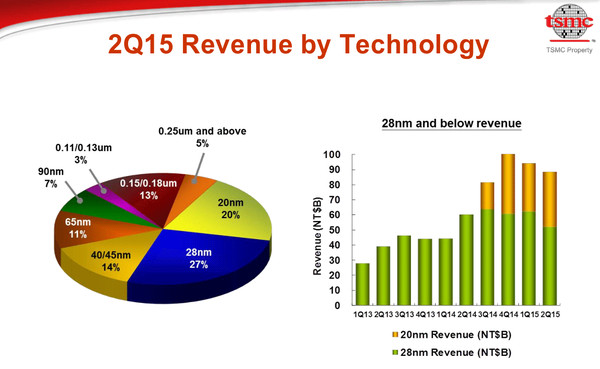

TSMC a également annoncé ses résultats financiers. La société a enregistré pour le second trimestre un chiffre d'affaire de 6.62 milliards avec une marge brute atteignant 48.5%. Par rapport au même trimestre l'année dernière, cela représente une hausse de 12.2% du CA (et 33% pour les bénéfices).

Au-delà des chiffres, TSMC a donné quelques détails intéréssants, confirmant d'abord la cession de sa participation dans ASML qui avait été annoncée en janvier, en assurant que cela ne changeait strictement rien à ses liens avec la société basée aux Pays-Bas. TSMC a également cédé 5% de sa participation dans Vanguard (VIS), un spinoff de TSMC proposant des services spécialisés. TSMC garde malgré tout le contrôle de 28% de VIS, étant toujours l'actionnaire majoritaire.

Le 28nm continue de représenter 27% des revenus tandis que le 20nm aura représenté 20% des revenus sur le second trimestre. TSMC note cependant que côté smartphones, les inventaires chez les constructeurs sont importants, particulièrement sur les produits d'entrée et milieu de gamme faute d'augmentation de la demande en Chine et dans les marchés émergeants. Le dollar elevé est l'une des causes mises en avant, tout comme les situations économiques locales. Tous ces facteurs font que TSMC s'attend à voir une hausse de son activité possiblement plus mesurée qu'ils ne le pensaient.

La nouvelle la plus importante est la confirmation que le 16nm est bel et bien en cours de production et que les premières puces ont été livrées ce mois-ci. Sur le 16nm, TSMC indique que la montée en puissance de son process sera extrêmement rapide, plus rapide que le 20nm profitant du BEOL (la seconde partie du process qui gère les interconnexions, plus de détails ici ) commun. Les taux de défauts sont annoncés comme extrêmement bas, et la courbe de réduction des défauts est la meilleure jamais obtenue par TSMC.

La société pense rafler en 2016 la majorité du marché 16nm. Les premiers clients en volume de TSMC sur le 16nm sont très probablement Apple (qui utiliserait aussi Samsung selon les rumeurs pour son A9) et Qualcomm qui ont en général la priorité sur les nouveaux nodes, même si AMD a annoncé avoir effectué deux tapeout sur ce process (sans préciser s'il s'agissait bien de TSMC, ou de GlobalFoundries).

TSMC a également profité de l'occasion pour parler du 10 et du 7nm. Selon TSMC les progrès réalisés sur le 10 nm sont « très encourageants » et continue de prévoir un début de la production en volume fin 2016. Une date qui, si elle est effectivement tenue, placerait potentiellement la sortie de produits 10nm en volume chez les très bons clients de TSMC avant même la sortie de Cannonlake chez Intel. Encore faut-il que TSMC tienne ses délais, bien évidemment, mais sur les deux derniers nodes cela a plutôt été le cas. Techniquement par rapport au 16 FinFET+ (la version la plus avancée de son process FinFET), le 10nm apporte 15% de vitesse à puissance égale, ou 35% d'économie d'énergie à vitesse égale. La densité est 2.2x celle du 16 FinFET+.

On notera avec intérêt que pour le 10nm, TSMC annonce des tape out sur un tas de secteurs, y compris ce qu'ils appellent high-performance computing, sous-entendu des CPU/SoC. Morris Chang, le chairman de TSMC est même allé un peu plus loin indiquant qu'il pense que TSMC va jouer un rôle important sous peu dans les marchés notebook et serveur, à condition de lier trois acteurs. Non seulement une fonderie (TSMC), ARM, mais aussi des sociétés capables de faire des designs custom « haute performance ».

TSMC a également évoqué le 7nm, s'attendant à lancer la qualification de son process au premier trimestre 2017, soit seulement cinq trimestres après la qualification attendue du 10nm. Le fondeur n'est pas très précis sur la technique, indiquant profiter de la maturité du 10nm pour mettre en place le 7nm, ce qui sous entends peut être que de la même manière qu'ils l'ont fait pour le 16nm avec le 20nm, TSMC pourrait garder le BEOL du 10nm sur le 7nm. Cela expliquerait très certainement le délai très réduit entre les qualifications.

Concernant l'EUV, Mark Liu, l'un des Co-CEO a indiqué que la porte était toujours ouverte et qu'ils travaillaient activement avec ASML, mais qu'il restait encore des challenges à résoudre, particulièrement autour des masques. Il a également indiqué que le 7 nm n'utiliserait « probablement pas » l'EUV dans un premier temps mais qu'il pourrait être introduit dans un second temps, et qu'il serait introduit dès le début à 5nm. Un changement de position et une mauvaise nouvelle pour ASML - par rapport au discours habituel qui indiquait que l'EUV serait possiblement introduit dans un second temps à 10nm et dès le début à 7nm.

Intel abandonne le Tick-Tock, confirme Kaby Lake

En marge de l'annonce de ses résultats financiers, la conférence dédiée aux analystes a été l'occasion pour Intel de confirmer ce dont l'on se doutait depuis un long moment : le 10nm du constructeur ne sera pas à l'heure.

En marge de l'annonce de ses résultats financiers, la conférence dédiée aux analystes a été l'occasion pour Intel de confirmer ce dont l'on se doutait depuis un long moment : le 10nm du constructeur ne sera pas à l'heure.

Au milieu de l'annonce de nouveaux retards sur sa roadmap mobile (notamment SoFIA LTE qui est désormais attendu pour la première moitié de 2016), Brian Krzanich a indiqué que la transition d'un node à l'autre ne tenait plus réellement le rythme des 24 mois que le constructeur souhaitait s'imposer, mais que sur les deux générations précédentes, il était plus proche des deux années et demi. En conséquence, la stratégie du Tick-Tock doit s'adapter et il aura confirmé l'arrivée d'un troisième produit 14 nm, Kaby Lake qui sera lancé durant la seconde moitié de 2016 (comme on le pressentait le mois dernier) !

Le CEO d'Intel décrit Kaby Lake comme « bâti sur les fondations de la micro architecture Skylake », mais « avec des améliorations clefs de performances ». Un phrasé relativement vague qui laisse entendre qu'il s'agirait d'un peu plus que d'un « Skylake refresh », sans vraiment s'engager (possiblement un nouveau GPU seulement ?). Le lancement de Cannonlake est lui bel et bien repoussé à la seconde moitié de 2017, en 10nm.

Interrogé (légèrement) sur le sujet par les analystes, Brian Krzanich a qualifié le retard par la complexité croissante de mise au point des process et que les difficultés du 10nm, si elles étaient similaires en pratique à celles rencontrées pour le 14nm, n'étaient pas directement liées au retard du 14nm. Intel est sur le sujet dans une position délicate puisque le constructeur a toujours clamé que le retard du 14nm n'aurait aucun impact sur le 10nm. Selon le CEO, la lithographie continue à être de plus en plus complexe, notamment à cause de l'augmentation des étapes de multi-patterning. En marge de cela, il aura rappelé que le 10nm d'Intel sera une solution sans EUV (le reste de l'industrie ne s'attends pas non plus à disposer de l'EUV pour le 10nm).

Pour le CEO, rajouter Kaby Lake à la roadmap permet d'améliorer la « prévisibilité » pour ses partenaires. Un argument qui ne manque pas d'ironie quand l'on connait l'historique du Tick-Tock chez Intel. La stratégie du Tick-Tock avait été mise en place en interne chez Intel au début des années 2000 par Pat Gelsinger dans le but de mettre de l'ordre dans le développement parfois anarchique des architectures qui a conduit à de nombreux projets et architectures repoussés et abandonnés. En interne, il s'agissait de délimiter clairement le périmètre de deux équipes de développement d'architectures, une située en Oregon et l'autre en Israël. Le tout articulé autour des changements de process tous les deux ans.

Ainsi chaque nouveau passage à un process (65 vers 45 nm, etc) serait un Tick. Une version légèrement modifiée de l'architecture précédente, portée vers le nouveau node (ce que l'on appelle un die shrink), tandis que la « nouvelle architecture », le Tock serait lancé l'année suivante, lorsque le process de fabrication serait arrivé à maturité.

Historiquement, ce n'est qu'avec beaucoup de créativité que le constructeur aura pu compter 24 mois entre chaque node, des retards de plusieurs mois ayant été observés au fil des années mais globalement jusqu'ici Intel s'était imposé de tenir le modèle de deux produits principaux (on met de côté les produits/architecture dédiées spécifiquement à la mobilité) par node sur environ deux ans.

Avec le 14nm le modèle n'était plus tenable, obligeant en 2014 Intel à proposer un Haswell refresh, simple « speed bump » d'Haswell, lancé en juin 2013 en lieu et place de Broadwell. En pratique si Intel s'est targué d'avoir « lancé » le 14nm en 2014, il s'agissait d'un seul processeur, le Core M, qui plus est dans un stepping remplacé avant même sa sortie ! Et pour le desktop, la gamme Broadwell aura été réduite au minimum avec seulement deux modèles, lancés le mois dernier pour tenir les annonces. Avec au final un retard d'un an sur la cadence que s'imposait jusqu'ici Intel.

En pratique Skylake (le tock original 14nm) est toujours attendu pour cette année même si Intel n'a pas encore confirmé de quelle manière s'effectuerait son lancement. Il a été indiqué par Intel qu'une des conséquences du ralentissement de l'activité en Q2 était un inventaire encore important, laissant penser que le constructeur pourrait repousser certains SKU de Skylake. Le lancement des modèles K était prévu pour rappel pour le 5 aout, tandis que le reste de la gamme 4 curs était attendue entre le 30 aout et le 5 septembre. On ne s'étonnerait pas de voir ces références repoussées de plusieurs semaines afin d'écouler les inventaires existants, même si Intel ne l'a pas dit clairement.

On notera également qu'au détour d'une question, Brian Krzanich a confirmé que le 10nm d'Intel utiliserait toujours des FinFET, et non un autre type de structures comme certaines rumeurs avaient pu le laisser entendre. Il a indiqué que le 10nm serait la troisième génération de FinFET d'Intel. A une autre question il a indiqué que des changements de matériaux étaient par contre attendus sans les préciser.

Interrogé enfin sur l'impact de ces retards sur « l'avance » d'Intel en matière de process par rapport au reste de l'industrie, Brian Krzanich s'est voulu rassurant, indiquant que l'avance d'Intel ne diminuerait pas sur le reste de l'industrie. De notre point de vue, il est probable que TSMC, et possiblement Samsung lancent une production en volume autour, voir même un peu avant Intel. Ce qui serait, au moins pour l'image, un véritable drame pour la firme de Santa Clara.