Les derniers contenus liés aux tags Samsung et 16/14nm

12nm et EUV à 7nm pour TSMC

Des détails sur le 7nm à l'ISSCC 2017

AMD valide le 14nm LPP de GloFo

L'A9 d'Apple produit par Samsung et TSMC

Intel précise son process 14nm

12nm et EUV à 7nm pour TSMC

TSMC a publié hier ses résultats financiers pour le dernier trimestre 2016. Le fondeur taiwannais a annoncé pour ce trimestre un revenu brut de près de 7.8 milliards d'euros, en hausse de 28.8% par rapport à la même période sur l'année précédente. Sur la totalité de l'année 2016, TSMC aura augmenté son revenu de 12.4% par rapport à 2015.

Pour 2017, TSMC s'attend à voir ses revenus progresser de "seulement" 5 à 10% (ce qui n'a pas manqué de décevoir les analystes financiers). Lors de la présentation des résultats, quelques informations supplémentaires ont été données.

Morris Chang, Chairman de TSMC s'est lancé dans quelques prédictions pour le marché 2017, s'attendant à voir le marché des smartphones grimper de 6% en unités, et celui du PC se contracter de 5% en unités également (il envisage également un déclin de 7% sur les tablettes tout en voyant le marché Internet of Things progresser de 34%).

Sur le 16/14nm, Morris Chang estime que la part de marché de TSMC est entre 65 et 70%, en dessous de ses attentes (TSMC dispose encore de 80% du marché sur le 28nm par exemple). Toujours poétique, le Chairman voit dans le 10 et le 7nm un "ciel bleu" par rapport à la compétition.

Quelques détails plus techniques ont été donnés, notamment par rapport à un "12nm" qui avait été évoqué ici ou là dans la presse. En pratique, TSMC travaille sur une nouvelle version de son process 16nm (une quatrième après les 16FF, 16FF+ et 16FFC) qui incorpore des améliorations importantes de densité. L'appellation commerciale exacte n'a pas été donnée, et on ne sait pas exactement quand elle sera disponible. On s'attendra dans quelques semaines à une annonce officielle, même si TSMC à confirmé aujourd'hui l'existence de ce "12nm".

Pour le 10nm, si le début de production est bien en cours, le gros du volume se situera sur la seconde partie de l'année (coïncidant avec le lancement des prochains iPhones dont le SoC utilisera le 10nm TSMC).

Sur le 7nm, plus de 20 sociétés travailleraient déjà sur des designs pour l'année prochaine, un chiffre qui devrait doubler dans l'année. Sur la question du 7nm en lui même, nous nous étions interrogés sur la manière dont le constructeur augmenterait la densité. Pour rappel, TSMC s'engage à lancer la production du 7nm dès la fin de l'année, il s'agira du node qu'utiliseront la majorité de ses clients, le 10nm devrait avoir une durée de vie courte et être réservé à quelques gros clients.

Le 10nm rappelle d'une certaine manière le 20nm de TSMC, lui aussi utilisé par des gros clients uniquement avant un passage rapide au 16nm. Cependant, avec une augmentation de la densité de 1.63x entre le 10 et le 7nm, la recette utilisée est plus complexe que pour le passage 20/16nm (qui ne proposait qu'une augmentation de densité de 1.15x). Nos confrères de SemiWiki, très au fait des détails, ont confirmé il y a quelques jours que des changements sur les tailles minimales des cellules sont en grande partie à l'origine des gains de densité et que pour réduire les coûts, TSMC évitera au maximum de généraliser le quadruple patterning (SAQP). Le 10 et le 7nm auront donc bel et bien des similarités techniques.

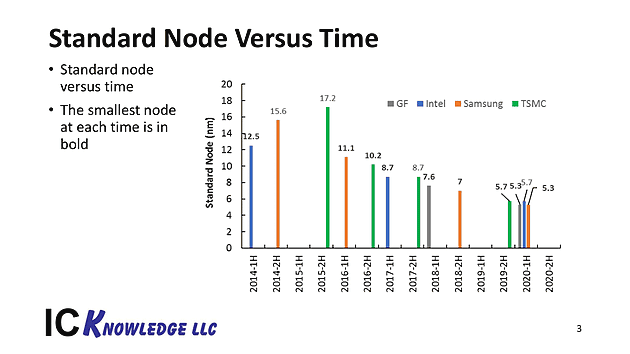

Pour essayer d'y voir un peu plus clair, et étant donné que plus aucun constructeur ne suit de règles équivalentes pour parler de densité, SemiWiki a publié ce graphique intéressant qui montre une "estimation" de la densité comparée de tous les fondeurs :

D'après SemiWiki, le 10nm d'Intel et le 7nm de TSMC auraient, après ajustement, une densité comparable. Il s'agit bien entendu d'estimations qui valent ce qu'elles valent, vous pouvez retrouver l'explication de la formule utilisée ici , mais elles donnent un bon ordre d'idée de ce à quoi il faut s'attendre (un seul bémol à cette analyse : les prévisions concernant GlobalFoundries nous semblent excessivement optimistes, en grande partie à cause des annonces de GlobalFoundries qui nous paraissent déconnectées de leur capacité d'exécution ces dernières années).

En pratique le 10nm de TSMC disposera tout de même d'une meilleure densité que l'actuel 14nm d'Intel, TSMC pourra donc se targuer d'avoir dépassé Intel côté process lorsque les premiers produits 10nm seront disponibles plus tard dans l'année. Et si Intel reprendra l'avantage avec "son" 10nm, TSMC sera effectivement - et pour la première fois - à parité dès la fin de l'année en lançant la production de son 7nm. Une situation qui durera un moment, et pour la première fois les constructeurs "fabless" pourront disposer d'un process équivalent en densité à celui d'Intel.

On notera enfin, concernant le 7nm, que TSMC a confirmé qu'ils inséreront l'EUV au bout d'un an de production à 7nm (soit fin 2018) pour créer une nouvelle version du 7nm (à l'image des multiples 16nm). Des propos plutôt optimistes concernant la lithographie EUV qui sera, Mark Liu le rappelle, indispensable à 5nm. Et un timing qui coïncide exactement avec le lancement de la production du 7nm de Samsung qui utilisera elle, dès le début, l'EUV !

Des détails sur le 7nm à l'ISSCC 2017

La conférence ISSCC (International Solid-State Circuits Conference) se tiendra pour son édition 2017 du 5 au 9 février à San Francisco, et nos confrères d'EEtimes ont eu accès à l'avant programme.

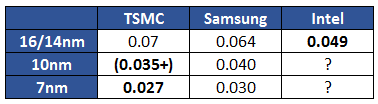

Comme tous les ans les acteurs du milieu des semi conducteurs y présenterons leurs nouveautés, et l'on notera que TSMC et Samsung présenterons leurs cellules SRAM (utilisées notamment pour la mémoire cache dans les puces). L'année dernière, Samsung avait proposé deux versions distinctes pour son process 10nm, optimisées pour la densité ou les performances, de 0.040 µm² et 0.049 µm².

D'après nos confrères, TSMC présentera une cellule SRAM 7nm de seulement 0.027µm², tandis que Samsung présentera une cellule SRAM 7nm de 0.030µm², mais fabriquée en EUV. D'après Samsung, l'EUV permettrait de diminuer la tension minimale nécessaire de 39.9mV (TSMC indique aussi des optimisations basse tension, on attendra la conférence pour comparer l'impact ou non de l'EUV).

La SRAM est un composant fondamental des puces et sa taille permet en général de se donner une bonne idée des process. Cependant il faut être assez méfiant, les constructeurs annonçant parfois des "records" de densité qu'ils n'utilisent pas forcément en production. Nous avons rapporté dans le tableau ci dessous les chiffres les plus bas (correspondant aux bibliothèques "hautes densité") pour TSMC, Samsung et Intel :

Par rapport au tableau, on notera qu'Intel n'utilise pas cette SRAM haute densité dans ses processeurs, mais de la SRAM 0.059 µm². Même en prenant cela en compte, Intel garde la meilleure densité à 16/14nm pour la SRAM. Le constructeur ne fournit pas encore d'infos sur ses futurs process.

TSMC n'a pas donné non plus de chiffre exact pour son 10nm, estimant simplement 50% de réduction par rapport à son 16nm sur la SRAM, ce qui nous vaut un chiffre entre parenthèses. Selon toutes vraisemblances, et conformément aux autres annonces sur la densité (2.1x d'après le constructeur), on estimera que TSMC devrait avoir une SRAM d'une taille légèrement inférieure à celle de Samsung.

Intel ne devrait pas effectuer d'annonce sur ce sujet lors de l'ISSCC, ce qui est assez dommage. Le constructeur devrait présenter les FPGA Altera Stratix 10 (14nm) tandis qu'AMD proposera une présentation plus en détails de Zen.

On notera aussi que Western Digital/Toshiba, ainsi que Samsung, présenterons des puces 3D NAND 512 Gbit TLC 64 couches. Dans le cas de Samsung, cette puce avait été annoncée cet été, plus de détails techniques devraient être disponibles. Pour Western Digital/Toshiba, cette puce avait été évoquée cet été comme objectif.

On notera que nos confrères pointent à raison un grand absent : une fois de plus, ni Intel, ni Micron, n'effectueront de présentation technique de leur mémoire 3D Xpoint !

AMD valide le 14nm LPP de GloFo

GlobalFoundries vient d'annoncer dans un communiqué qu'il avait livré à AMD des puces fonctionnelles gravées avec le process 14nm LPP (Low Power Plus), la version la plus avancée du procédé de fabrication Samsung 14nm FinFet (l'Apple A9 utilisant le 14nm LPE Low Power Early) qui est pour rappel également déployé chez GF.

Le fondeur précise qu'AMD a "taped out" plusieurs produit chez GF en 14nm LPP et qu'il est actuellement en train de valider les échantillons produit. Il semble donc qu'un premier produit ai été validé, GF parlant de "silicon success". AMD indique au passage qu'il compte utiliser le process 14nm LPP sur des produits CPU, APU mais aussi GPU. Jusqu'alors les GPU AMD étaient comme ceux de Nvidia fabriqués par TSMC, mais sachant qu'AMD a toujours des engagements contractuels sur des volumes avec GF qu'il peine à remplir il est logique qu'il favorise ce dernier si le process est à la hauteur. On devrait donc avoir droit en 2016 à une bataille d'architecture entre AMD et Nvidia combinée à une bataille de fondeurs avec d'un côté le 16nm FinFET+ de TSMC et de l'autre le 14nm LPP de Samsung/GlobalFoundries !

GlobalFoundries indique que le 14nm LPP a été qualifié au cours du troisième trimestre pour la production, cette dernière va débuter au cours de ce quatrième trimestre et arrivera à plein débit en 2016, sans plus de précision. Difficile pour le moment de savoir quand les premières puces AMD produites en 14nm LPP seront lancées en 2016, mais il serait étonnant que ce soit avant le second trimestre côté GPU et le dernier trimestre côté CPU. Vivement !

L'A9 d'Apple produit par Samsung et TSMC

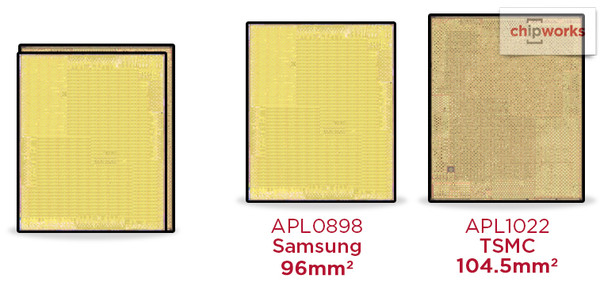

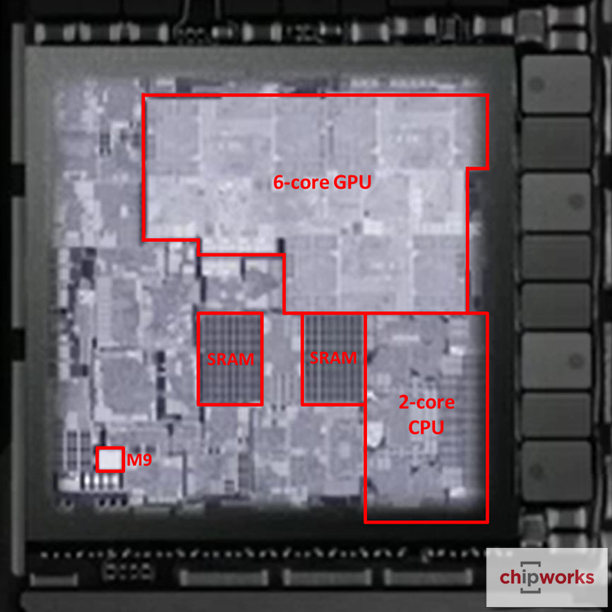

La société Chipworks a confirmé via son blog une semi surprise : l'A9, le SoC ARM custom présent dans l'iPhone 6s d'Apple existe en deux variantes, une produite par Samsung et l'autre par TSMC. Selon Chipworks, ils ont trouvé ces deux puces dans « deux modèles identiques », tandis que iFixit a trouvé la version Samsung dans un iPhone 6s et la version TSMC dans le modèle 6s Plus .

Les deux puces portent une référence différente (APL0898 et APL1022) et mesurent respectivement 96 mm2 et 104.5 mm2 (l'A8 en 20nm mesurait 89mm2 à titre de comparaison). Le nombre de transistor est inconnu, il était de 2 milliards sur l'A8. Le process de Samsung (partagé sous licence avec GlobalFoundries) est un 14nm FinFET tandis que celui de TSMC est un 16nm FinFET même si en pratique les nomenclatures ne veulent plus dire grand-chose. Samsung semble avoir tout de même un avantage de densité, quelque chose que l'on attendait, TSMC avait déjà annoncé dès l'année dernière qu'ils proposeraient une seconde version de leur process 16nm en 2016 (le 16 FinFET Plus) afin d'améliorer la densité et être plus compétitif avec la concurrence.

Au-delà de leurs tailles différentes, les puces semblent se comporter de manière similaire dans les premiers benchmarks que l'on a pu croiser, même s'il est encore tôt pour se faire une idée complète. Techniquement l'A9 est un SoC composé pour sa partie CPU d'un dual core basé sur une architecture ARM 64 bit custom et cadencé à 1.8 GHz accompagné de 3 Mo de cache L2. Un GPU issu de chez PowerVR avec « six cores » s'occupe de la partie graphique, le CPU et le GPU partageraient possiblement 8 Mo de cache L3. Apple annonçait +70% de performance CPU et +90% de performances graphiques par rapport à sa génération précédente gravée en 20nm par TSMC, des chiffres qui se vérifient à peu près dans les premiers benchmarks. Le SoC est de type PoP avec 2 Go de mémoire LPDDR4 au-dessus (et l'on notera pour l'anecdote la présence d'un contrôleur NAND PCIe/NVMe dans l'iPhone 6s !)

Si l'on s'attendait à voir Samsung et TSMC produire la nouvelle génération de puces d'Apple, beaucoup pensaient que Samsung aurait récupéré la production de l'A9 et TSMC celle de l'A9X (la version iPad du SoC). En juillet dernier, TSMC avait cependant semé le doute indiquant avoir déjà réalisé ses premières livraisons de puces à ses clients.

Le choix d'utiliser deux process distincts pour produire une même puce est original de la part d'Apple qui n'a toutefois pas les mêmes problèmes que tout le monde. Le volume de l'iPhone (13 millions vendus en un weekend, 200 millions attendus sur l'année) permet à la marque de justifier aisément le cout double de développements séparés pour deux process différents (les process sont incompatibles dans leurs règles et les designs doivent être adaptés pour chaque fondeur).

Cela permet également d'améliorer le volume de disponibilité dès le lancement - un problème particulièrement important sur des process de toute dernière génération, il suffit de regarder la disponibilité anémique des Skylake d'Intel pour s'en convaincre - et de minimiser les problèmes de yields que pourraient avoir l'un ou l'autre de ses fournisseurs.

Intel précise son process 14nm

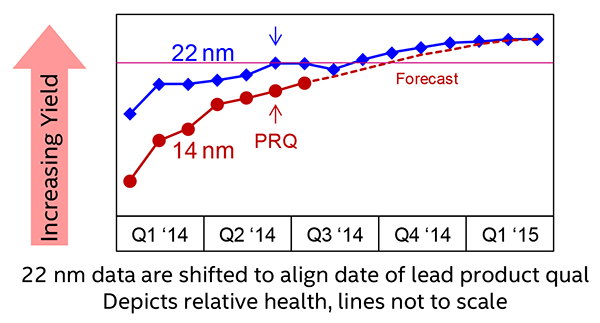

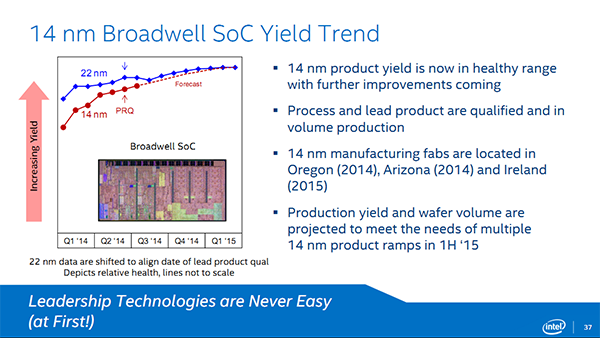

En marge de son annonce sur Broadwell-Y, Intel a partagé quelques détails sur son process 14nm. Comme vous le savez, le process 14nm d'Intel souffre de retards. Le constructeur avait annoncé qu'il décalerait la mise en production d'un trimestre en novembre dernier, tout en publiant des indications autour de ses yields qui laissaient entendre un retard de 6 mois.

En pratique, il est difficile de mesurer réellement le retard du process même si Intel a partagé ce nouveau graphique de yields :

Plusieurs choses à voir sur ce graph, d'abord, si vous vous souvenez du dernier graphique de yields présenté par Intel, celui-ci diffère fortement. Là où le premier était aligné par rapport au début du développement du process, les graphiques sont désormais alignés sur la qualification du premier produit (Ivy Bridge en 22nm, Broadwell-Y en 14nm), étape préalable à la mise en production. Intel indique sur ce graphique que la qualification de Broadwell-Y a eu lieu en fin de second trimestre et qu'il est actuellement en production en volume. Si l'on ne connait pas la date précise de qualification d'Ivy Bridge, on sait que la production en volume avait débuté au troisième trimestre 2011, ce qui met donc au minimum deux ans et neuf mois entre la mise en production en volume du 22nm et celle du 14nm.

L'autre point le plus important concerne (on passera sur l'échelle absente une fois de plus) l'écart de yields entre la mise en production d'Ivy Bridge et celle de Broadwell-Y. Le constructeur a choisi, comme nous le supposions en novembre dernier, de lancer la production avec des niveaux de yields inférieurs. En pratique, le décalage de yields pour la mise en production, si l'on prend en compte la prédiction pour les prochains mois est de quatre mois (voir la ligne violette que nous avons rajouté au graphique). Ce qui ne signifie pas quatre mois de retard pour ce process rappelez-vous que les graphiques ne sont plus alignés ! mais qu'Intel a anticipé la mise en production de quatre mois par rapport à celle d'Ivy Bridge. Il est probable que, plus que le niveau de yields, ce soit une date butoir qui ait été utilisée pour déterminer la mise en production afin de s'assurer qu'un produit soit « livré » cette année.

En soit, ce choix est logique : le constructeur peut ainsi proposer un peu plus tôt des produits quitte à sacrifier sur ses marges, tout en honorant - on l'imagine - des contrats auprès de ses partenaires et en pouvant montrer aux investisseurs qu'un produit en 14nm a bel et bien été lancé en 2014. En pratique, si Intel pourra effectivement « lancer » un premier produit cette année, le gros du volume en 14nm devra attendre. Le constructeur ne le cache pas en indiquant que ses yields devraient être acceptables au premier semestre 2015 pour la production en volume de produits vendus en plus larges quantités que les Broadwell-Y.

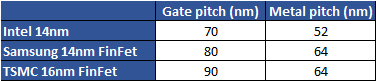

Intel est également revenu sur la compétition en proposant une nouvelle version de son graphique à propos de la densité qui avait largement fait débat :

Cette fois ci, le constructeur mélange IBM et TSMC parmi ses concurrents, et met de côté Samsung (pour rappel, Samsung et GlobalFoundries ont annoncé un partenariat sur le 14nm autour du process 14nm développé par Samsung, hors de la Common Platform l'alliance qui liait Samsung et GlobalFoundries à IBM). Le constructeur a le mérite d'indiquer la formule qu'il utilise pour mesurer la densité ce qui n'était pas le cas auparavant.

La densité des puces est un sujet pour le moins complexe et si la formule annoncée par Intel (gate pitch l'écart entre deux transistors multiplié par metal pitch l'écart de la couche métallique la plus basse qui sert à l'interconnexion des transistors) est correcte, elle ne prend en compte qu'en partie la question de la densité.

Intel a par exemple toujours été en retard sur ses concurrents sur la question du metal pitch. Le 22nm d'Intel disposait d'un metal pitch de 90nm tout comme le 28nm de TSMC. En pratique, pour le 14/16nm, voici les chiffres qui sont annoncés :

C'est sur cette formule (90x64 comparé à 70x52) qu'Intel annonçait un gain de 35% par rapport à TSMC. Bien sur, la densité finale d'une puce ne dépend pas que de cette formule, les règles de design, la taille des SRAM, et d'autres facteurs jouent de manière importante sur la densité « réelle » de transistors obtenus au mm2 sur une puce, la formule metal pitch x gate pitch n'indiquant que le cas « idéal ». C'est sur ces autres facteurs que TSMC estime gagner 15% de densité « réelle » au total entre son process 20 et 16nm. Si l'on ne peut pas reprocher à Intel de choisir la formule qui l'arrange le plus pour mettre ses produits en avant, on peut apprécier que cette fois ci, la formule choisie soit au moins précisée !

On notera par contre qu'Intel continue d'ignorer Samsung qui devrait pourtant être son plus sérieux concurrent sur le 14nm. Samsung pour rappel avait annoncé une production en volume de son process 14nm pour la fin de l'année 2014.

Sur le papier et comme indiqué plus tôt, le process d'Intel semble être supérieur aux autres process 16/14nm de première génération annoncés (on se souviendra que et TSMC, et Samsung ont annoncés une seconde version de leurs process), en partie par le choix fait d'obtenir une réduction forte sur la taille des interconnections atteignant un metal pitch de 52nm qui sera en avance pour la première fois depuis plusieurs process sur ce que proposeront ses concurrents.

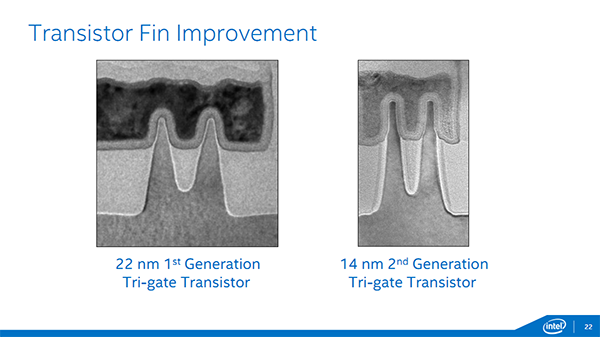

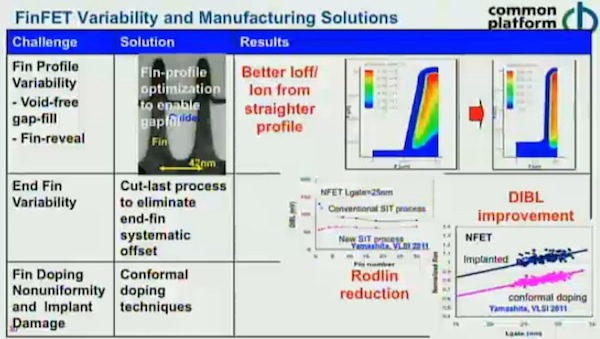

Il s'agira également de la seconde génération de FinFet pour Intel. Outre l'apprentissage effectué par le premier, on peut noter sur les photos fournies par le constructeur quelques changements dans la forme des Fin. Là ou en 22nm les gates avaient une forme trapézoidale, les fins ont désormais une forme rectangulaire plus proche de la forme idéale attendue. On se souviendra qu'IBM et la Common Platform avaient soulevés les questions de forme et de variabilité du process d'Intel :

Il sera intéressant de voir si Samsung (et TSMC) aura comme le laissait entendre IBM à l'époque appris de la première version du process d'Intel.

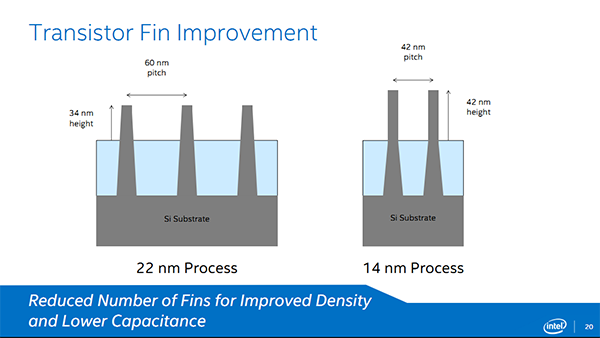

On notera également une augmentation de la hauteur des fins (de 34nm à 42nm) qui devrait permettre une amélioration des performances, quelque chose qui devrait être très utile notamment sur les usages SoC pour limiter la consommation. Si Intel ne donne pas de chiffre de performances concernant les transistors, le constructeur donne quelques chiffres concernant Broadwell-Y. Sur cette puce, et par rapport à son équivalent Haswell, les courants de fuites seraient réduits par deux, avec un rapport performance par watt de 2x.

Pour résumer, Intel semble avoir fortement optimisé son process pour les usages mobiles qui sont aujourd'hui les marchés les plus porteurs (qu'il s'agisse des PC portables ou des tablettes/smartphones) et il sera intéressant de voir comment les gains (forts) annoncés sur Broadwell-Y se traduiront sur le reste des produits 14nm du constructeur. Si le retard d'Intel dans la mise au point de son process est conséquent, et que le lancement de Broadwell-Y se fait dans des conditions non optimales (yields plus faibles qu'attendus, et produits à fort volumes repoussés en 2015), le constructeur semble disposer sur le papier d'un process solide et ambitieux, qui semble corriger les problèmes de sa première génération FinFet. Reste que les délais dans sa mise au point ont permis à la concurrence de se rapprocher - au moins dans les annonces avec un Samsung qui devrait être particulièrement agressif. L'avantage technique apporté par ses process de fabrication reste toujours réel et important pour Intel, et sur le papier son 14nm devrait permettre à Broadwell-Y des avancées notables. Mais la domination d'Intel sur le sujet des process ne semble plus - si l'on s'en tient aux annonces respectives des uns des autres - aussi hégémonique qu'elle le fut ces dernières années.