Les contenus liés au tag SK Hynix

Afficher sous forme de : Titre | FluxLa HBM2 Hynix dispo ce troisième trimestre

La HBM 2 SK Hynix en retard

Mémoire 20nm en production chez SK Hynix

SK Hynix annonce la R9 Fury X d'AMD

Focus: Comprendre la mémoire HBM introduite par AMD

Hynix sur les rangs pour la NAND Toshiba ?

Comme nous l'écrivions récemment, Toshiba cherche à vendre une partie de son activité semi-conducteurs afin de faire face à des problèmes de trésorerie. Et si nous évoquions la piste Western Digital, une autre attire aujourd'hui l'attention des analystes.

Comme le rapporte Business Korea , la réaction de SK Hynix vis à vis de cette porte laissée ouverte par Toshiba est très attendue.

D'une part, parce que cela donnerait à SK Hynix l'occasion de quitter le pied du podium des fabricants de NAND. Au troisième trimestre 2016, Samsung était solide leader (36,6% du marché), Toshiba second (19,8%), alors que SK Hynix ne pointait qu'à la quatrième place (10,4%).

D'autre part, et malgré le rachat en 2012 de la société américaine Link A Media Devices (qui avait dessiné notamment les contrôleurs des Corsair Neutron), SK Hynix pourrait profiter du savoir faire de Toshiba en matière de contrôleurs.

SK Hynix a également loupé récemment l'occasion d'accroître son activité dans les semi-conducteurs : alors que la société convoitait une usine de capteurs mise en vente par... Toshiba, Sony a profité de l'hésitation du constructeur coréen pour lui couper l'herbe sous le pied. SK Hynix n'aurait probablement pas envie de renouveler son erreur.

Enfin, les deux protagonistes ont mis fin il y a deux ans à un litige qui les opposait en matière de propriété intellectuelle et ont débuté une collaboration dans la technologie de lithographie par nano-impression, l'une des voies ouvertes vers le futur de la litographie.

Tous ces arguments mis bout à bout, rendent crédibles la participation de Hynix dans les activités de Toshiba. Aucune des deux entreprises n'a, pour l'heure, commenté cette hypothèse.

Deuxième génération de NAND 3D Intel mi 2017

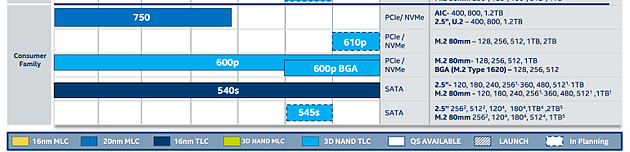

Le site benchlife.info a publié un extrait de la roadmap SSD grand public d'Intel. Après les modèles 600p lancés cet été, équipés de NAND 3D, Intel lancera l'année prochaine des 610p.

On ne sait pas encore grand chose de ces modèles, si ce n'est qu'ils seront équipés de la seconde génération de NAND 3D d'Intel.

Il s'agira là aussi de modèles M.2 de 80mm de long (M.2 2280) en PCIe/NVMe, ils seront proposés dans des capacités de 128, 256, 512 Go, ainsi que 1 et 2 To. Leur lancement est prévu d'après nos confrères au quatrième trimestre 2017.

Au troisième trimestre, on verra arriver deux autres nouveautés, avec d'abord une version "BGA" du 600p, il s'agira en pratique de M.2 compacts (M.2 1620). Cette version sera disponible en 128, 256 et 512 Go.

Enfin on notera que sur l'entrée de gamme, les actuels 540s seront eux aussi succédés par une version NAND 3D. Les 540s ont la particularité d'utiliser de la TLC 16nm SK Hynix contrairement à ses autres modèles. Le 545s utilisera donc de la NAND 3D et sera disponible à la fois au format SATA et M.2. Les capacités démarreront dans les deux cas à 256 Go et atteindront 2 To en SATA, et 1 To en M.2. Intel devrait tout de même selon la roadmap conserver les 540s dans sa gamme. Ces 545s devraient être lancés au troisième trimestre 2017.

ASML investit dans Carl Zeiss SMT pour l'EUV

ASML a annoncé hier qu'il comptait s'offrir un quart de Carl Zeiss SMT (24.9%) pour un montant de près de un milliard d'euros. Zeiss SMT est la filiale "Semiconductor Manufacturing Technology" du groupe allemand Zeiss spécialisé dans l'optique.

ASML indique dans son communiqué qu'il s'agit de renforcer la collaboration entre les deux sociétés, Zeiss SMT fournissant les systèmes optiques utilisés notamment dans les machines de lithographie EUV.

ASML investira en prime 220 millions d'euros dans le centre de recherche et développement de Zeiss SMT, et financera 540 millions d'investissements sur les 6 prochaines années.

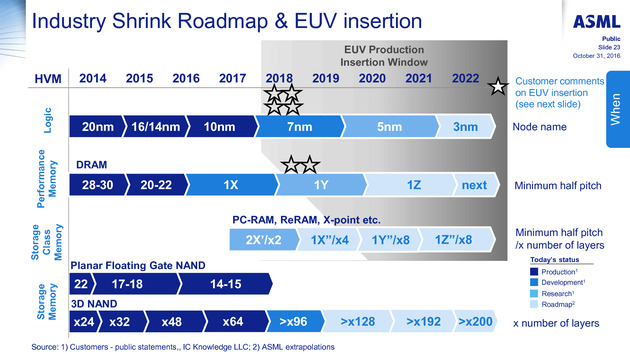

L'enjeu de l'investissement, selon ASML, concerne les futures générations d'EUV avec la possibilité d'étendre la durée de vie de la technologie. Car si certains fabricants de semiconducteurs comme Samsung disent désormais (enfin !) qu'ils utiliseront l'EUV à 7nm, les très nombreux retards de la technologie font qu'elle court le risque de voir sa fenêtre d'utilisation réduite, au risque d'être remplacée par d'autres technologies.

Des systèmes optiques plus complexes avec une ouverture numérique de 0.5 (contre 0.33 pour les premières générations d'EUV) est ce que vise ASML dans cet investissement, qui ne devrait porter ses fruits que d'ici 2024. Il permettrait cependant d'étendre la durée de vie de l'EUV sous les 5nm et pour "plusieurs générations". On sait - en parallèle - qu'autour de 5nm, on atteindra les limites du silicium et l'utilisation d'autres matériaux deviendra nécessaire.

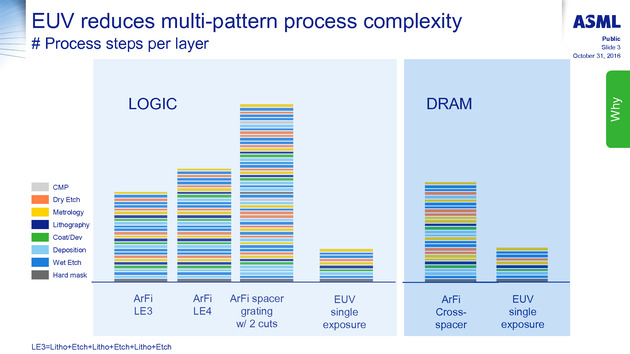

L'intérêt de la lithographie EUV est pour rappel de remplacer la source lumineuse utilisée actuellement par les scanners (elle est générée par des lasers à exciplexe Argon/Fluor avec une longueur d'onde de 193nm) par une source dont la longueur d'onde n'est que de 13.5nm, améliorant fortement les possibilités et réduisant le nombre d'étapes nécessaires pour arriver a fabriquer les puces en évitant la généralisation du multi-patterning.

ASML aurait réitéré à nos confrères d'EEtimes que quatre fabricants de puces, et deux fabricants de mémoires, se sont engagés à faire entrer l'EUV en production en 2018, quelque chose que la firme avait également indiqué dans une présentation aux investisseurs (qui évoquait 2018/2019). Une affirmation qui nous parait bien optimiste !

Aujourd'hui, seuls Samsung et GlobalFoundries se sont engagés publiquement à 7nm, pour des dates qui coïncident. En ce qui concerne TSMC, il faudra attendre le 5nm pour le voir arriver de manière extensive, sa production risque est prévue pour 2019 uniquement. Intel avait annoncé de son côté qu'il n'utiliserait pas l'EUV à 10nm, et qu'au mieux l'EUV était "une option" pour le 7nm. Le 7nm d'Intel utilisera une solution de lithographie a immersion classique. Et côté dates, 2019 semble extrêmement optimiste considérant l'exécution d'Intel ces dernières années (retards massifs sur le 14nm, introduction de Kaby Lake pour retarder le 10nm, lancement du 10nm repoussé à fin 2017 et uniquement sur des références mobiles, sans parler de l'introduction dans la roadmap de Coffee Lake en 2018... et en 14nm !).

En ce qui concerne les fabricants mémoire, Samsung avait évoqué la possibilité sans pour autant s'engager fermement. SK Hynix évoquait l'utilisation de l'EUV vers 2019.

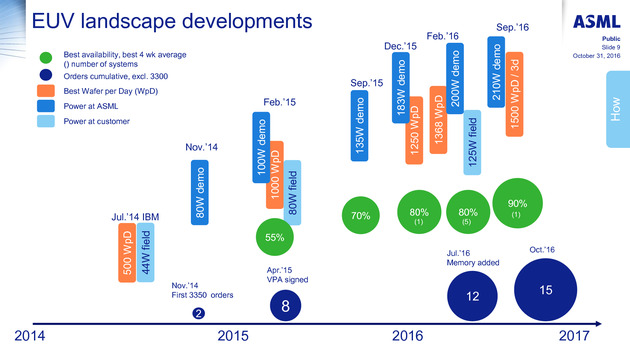

Les machines qui seront utilisées en production, les NXE:3400B, atteindraient d'après ASML un débit de 125 wafers/heure, un progrès notable par rapport à mars 2015 ou ASML se félicitait de 42 wafers/heure (entre 50 et 100 wafers/heure étaient considérés comme le minimum pour éventuellement utiliser la technologie d'après Mark Bohr d'Intel). Pour arriver à ce chiffre, ASML devra augmenter fortement la puissance de la source lumineuse. Le constructeur aurait livré des sources 125W à ses clients cette année qui ont permis d'atteindre 85 wafers/heure.

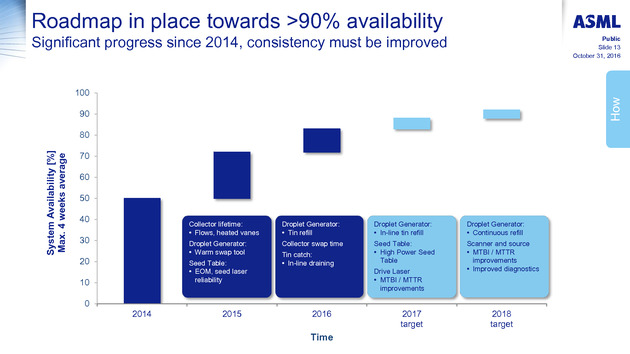

La question de la disponibilité des machines semble également être meilleure, de seulement 55% à l'époque, ASML atteint aujourd'hui entre 70 et 80%, avec l'objectif d'être a 90% en 2018.

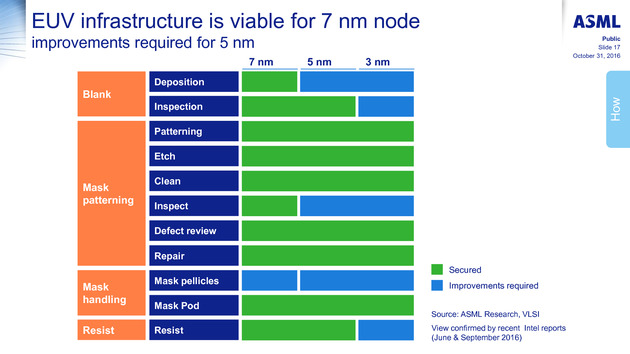

L'enthousiasme d'ASML - le seul à se lancer dans l'EUV - est forcément élevé pour sa technologie mais il faut une fois de plus rappeler que les scanners ne sont qu'une partie de la chaîne de fabrication. Les progrès réalisés, bien qu'importants, ne veulent pas dire que l'EUV est "prêt", loin de là.

La question des masques (la plaque transparente qui contient l'image de la puce à graver) et de l'inspection de leurs éventuels défauts n'a pas encore été résolue. Et si là aussi ASML tente d'apporter sa propre réponse, en pratique le problème reste complexe a solutionner avec des conséquences massives sur la viabilité de la technologie en production (plus de détails dans cet excellent article ).

Samsung évoque la GDDR6

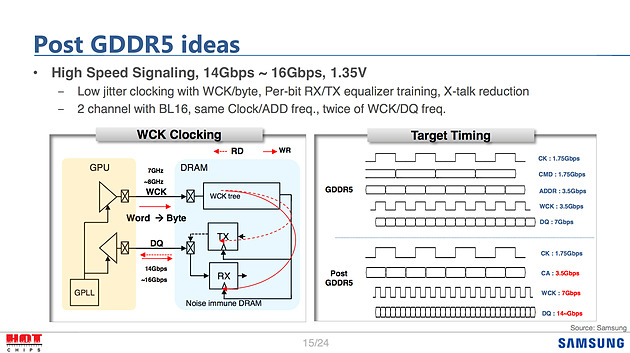

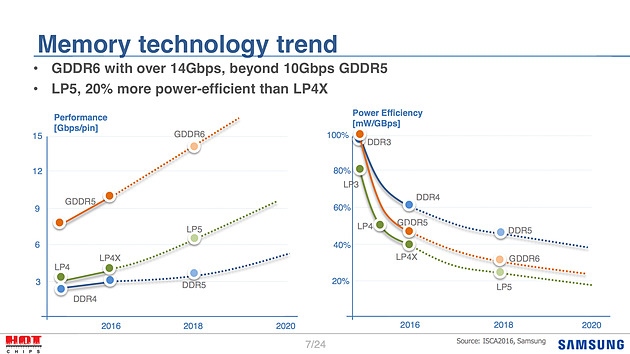

En parallèle à la mémoire HBM, Samsung à évoqué le futur de la GDDR5, ignorant quelque peu l'existence de la GDDR5X de Micron qui, bien que standardisée par le JEDEC, n'a pas été adoptée par ses concurrents.

Pour la GDDR6, Samsung évoque certaines des pistes de travail envisagées. Côté objectifs la mémoire visera dans un premier temps 14 à 16 Gbps, ce qui était la cible haute pour rappel de la GDDR5X lors de sa présentation par Micron. Lors de la certification de la GDDR5X par le JEDEC, 14 Gbps est devenu le maximum visé. On notera que la GTX 1080 utilise pour rappel de la GDDR5X 10 Gbps. Techniquement, la GDDR5X abaissait la tension de la GDDR5 à 1.35V et doublait la bande passante en doublant le prefetch.

Samsung donne ici quelques idées sur la GDDR6, reprenant par exemple l'idée de la tension à 1.35V. L'élaboration de la spécification finale se fera au sein du consortium JEDEC dans les mois à venir.

Côté timing, Samsung évoque 2018, aligné avec la DDR5 et la LPDDR5, et un gain d'efficacité énergétique autour des 30%. On notera au passage que Samsung continue lui aussi de pousser son propre standard "X" avec la LPDDR4X, une variante de la mémoire mobile LPDDR4 qui fait "seulement" baisser la tension VDDQ à 0.6V pour obtenir un gain d'efficacité de 20%. Si le JEDEC n'a pas encore ratifié la LPDDR4X, on notera que SK Hynix avait annoncé en juin qu'il produirait lui aussi ce type de mémoire.

SK Hynix et Samsung parlent de HBM

Comme tous les ans, c'est à la fin de l'été que se tient la conférence Hot Chips (28ème édition) ou les divers acteurs du milieu présentent leurs nouveautés. Parmi les attractions de cette année, on attendra, dans la nuit de mardi à mercredi, "A New, High Performance x86 Core Design from AMD" qui devrait probablement nous en dire un peu plus sur Zen.

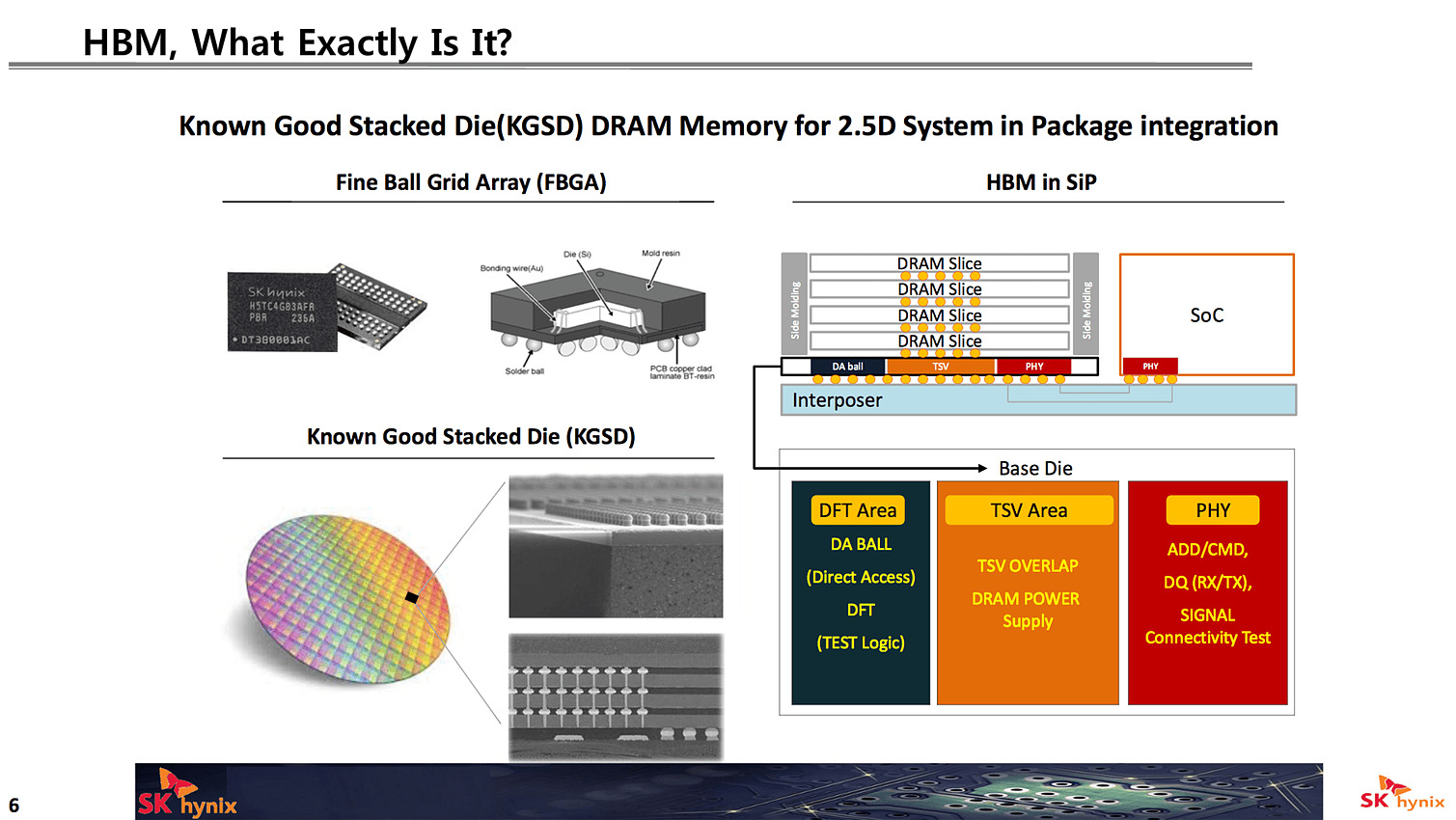

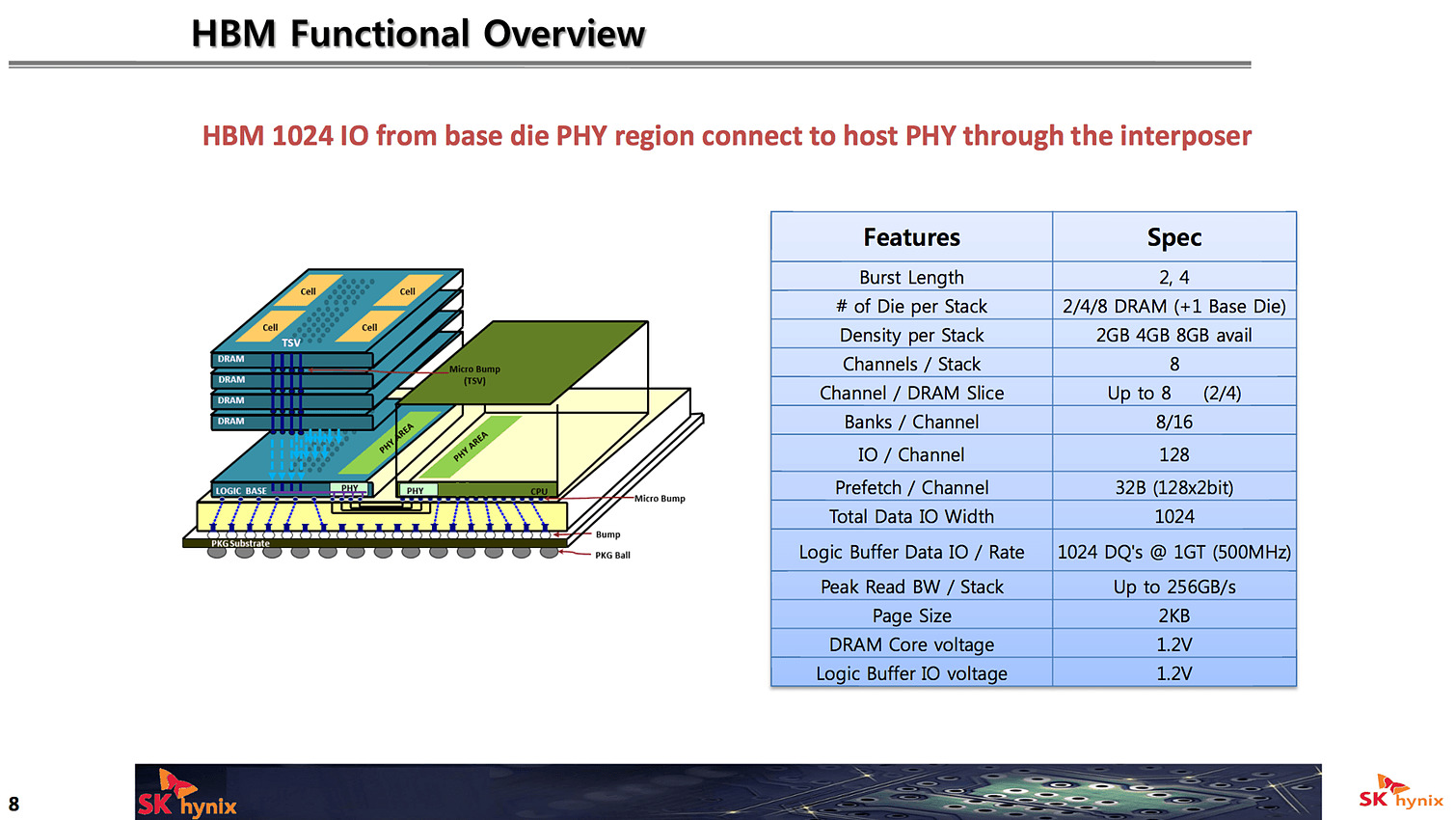

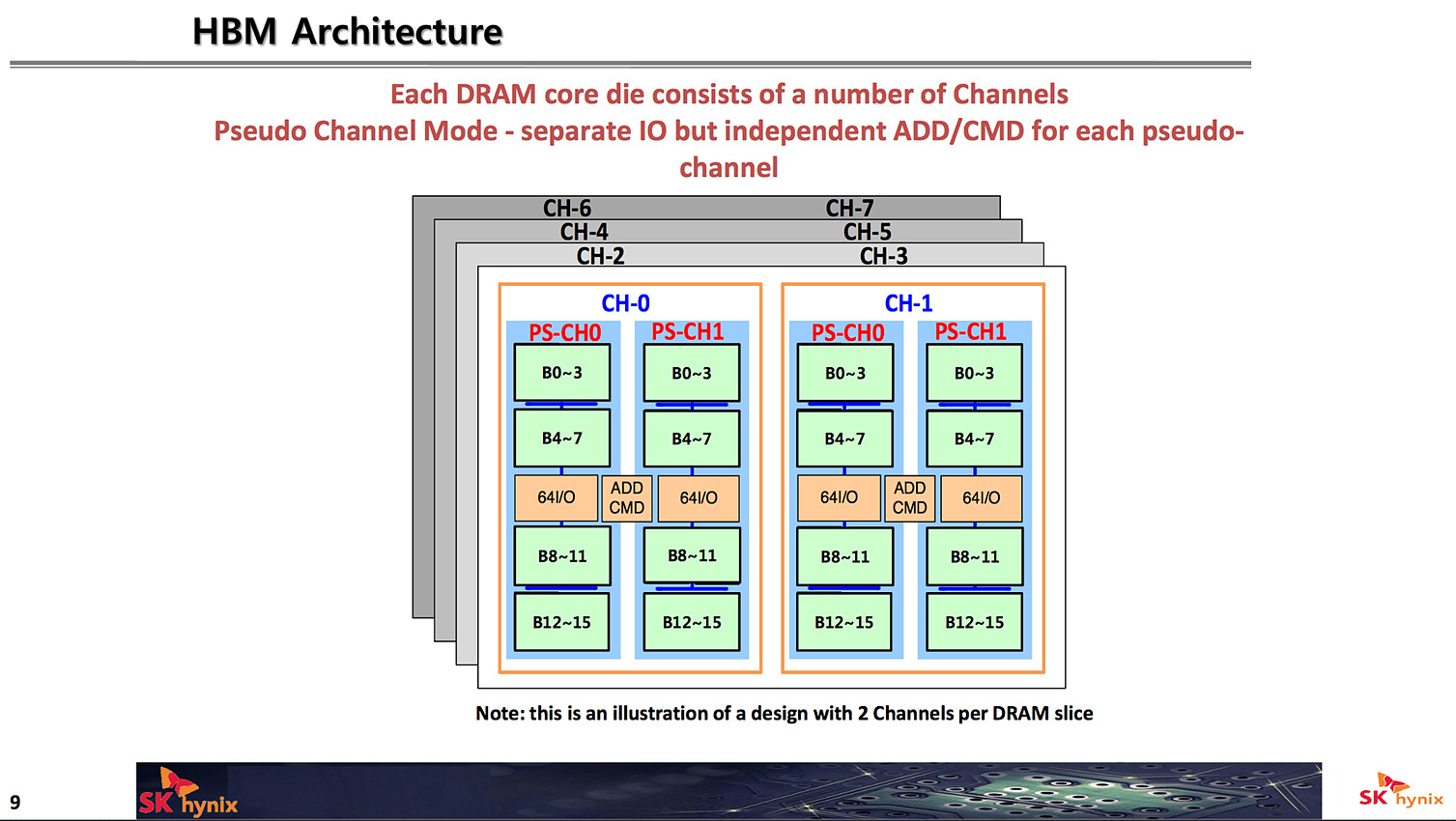

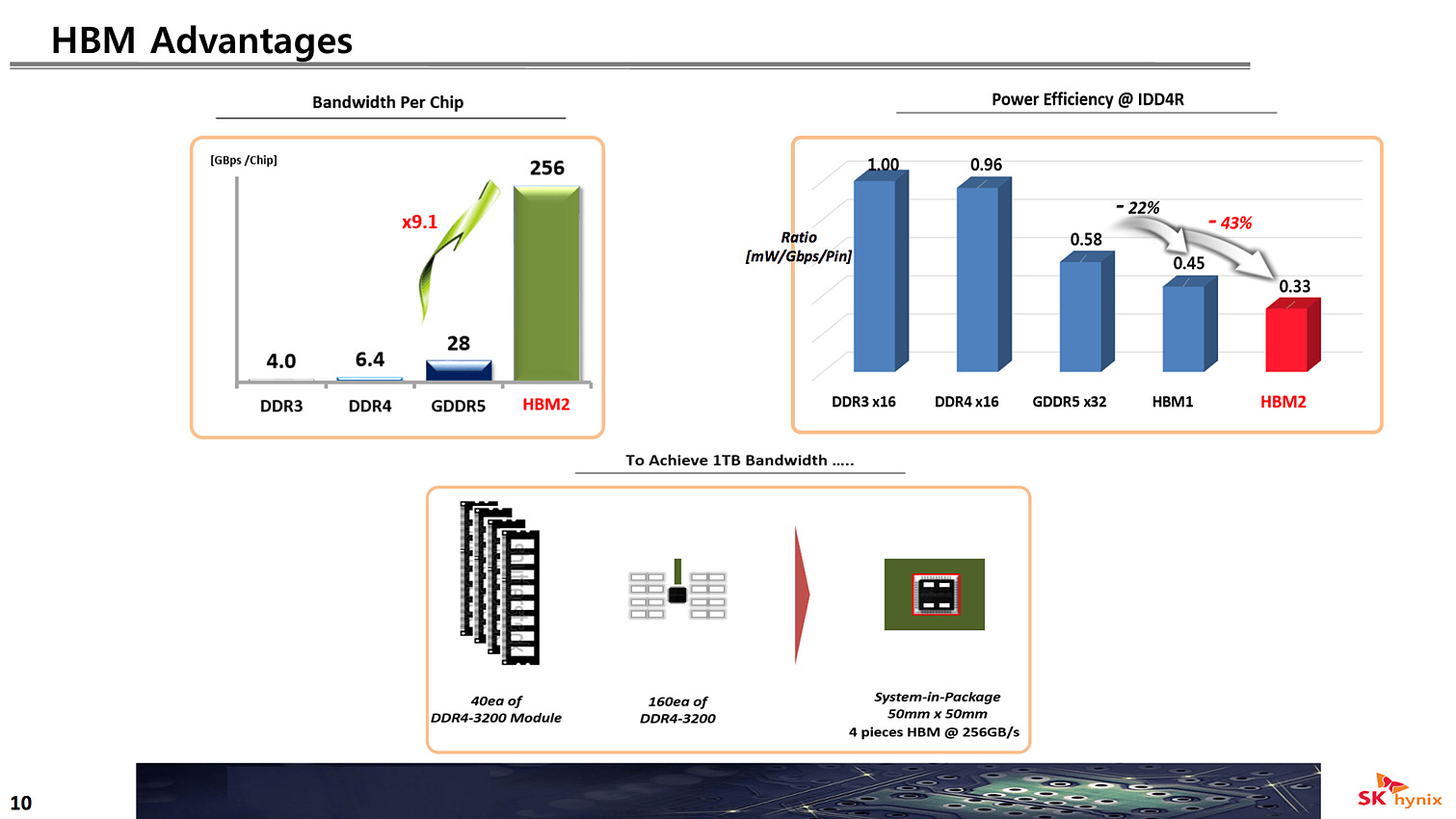

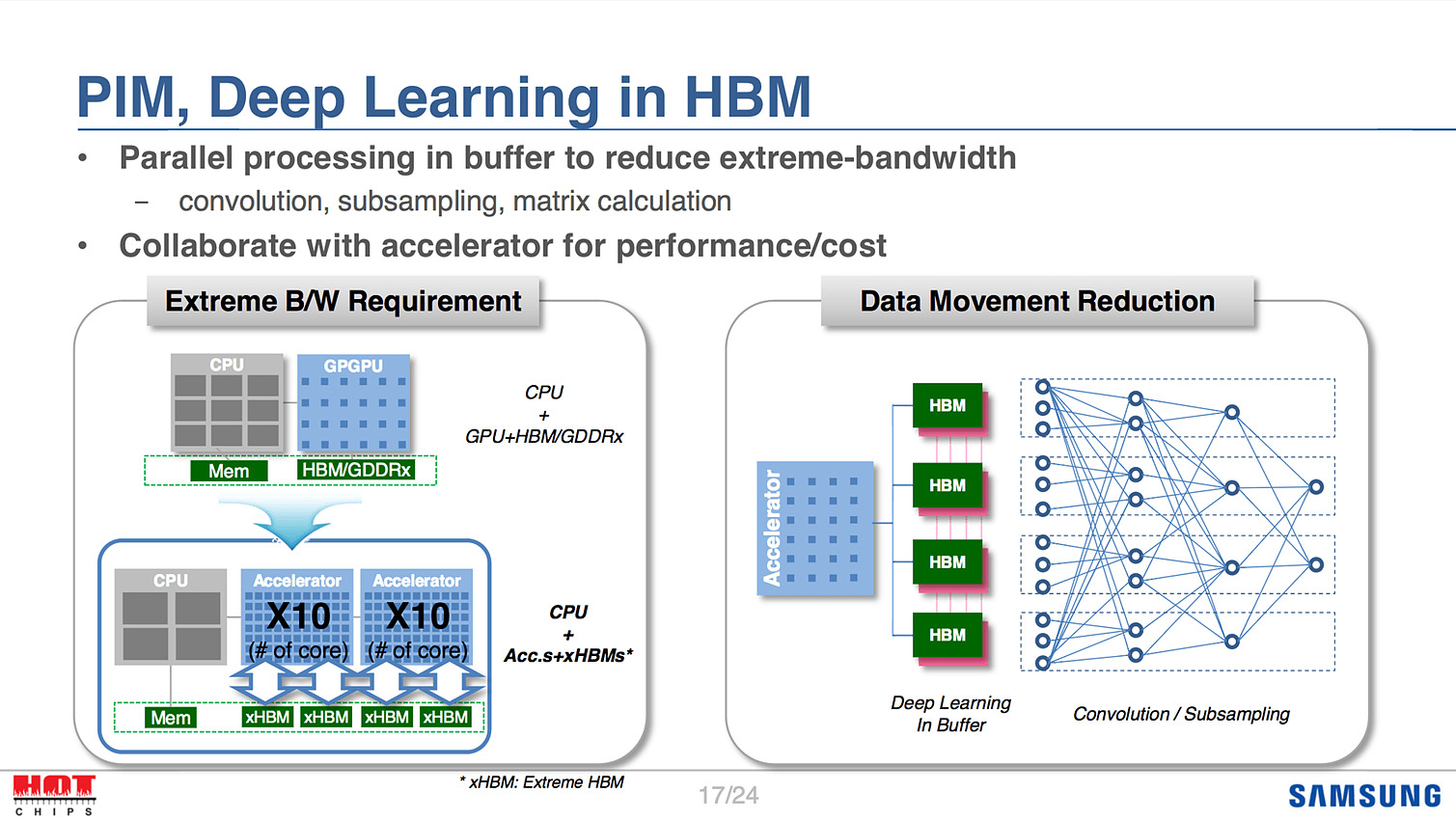

La première matinée de conférence avait lieu hier, dédiée à l'utilisation des nouvelles technologies mémoires. Chez SK Hynix et Samsung, la HBM était au programme. Pour rappel, la mémoire HBM est l'assemblage sur une même puce d'un die, en dessous, contenant les contrôleurs mémoires, et sur lequel on empile plusieurs dies de mémoire DRAM traditionnelle.

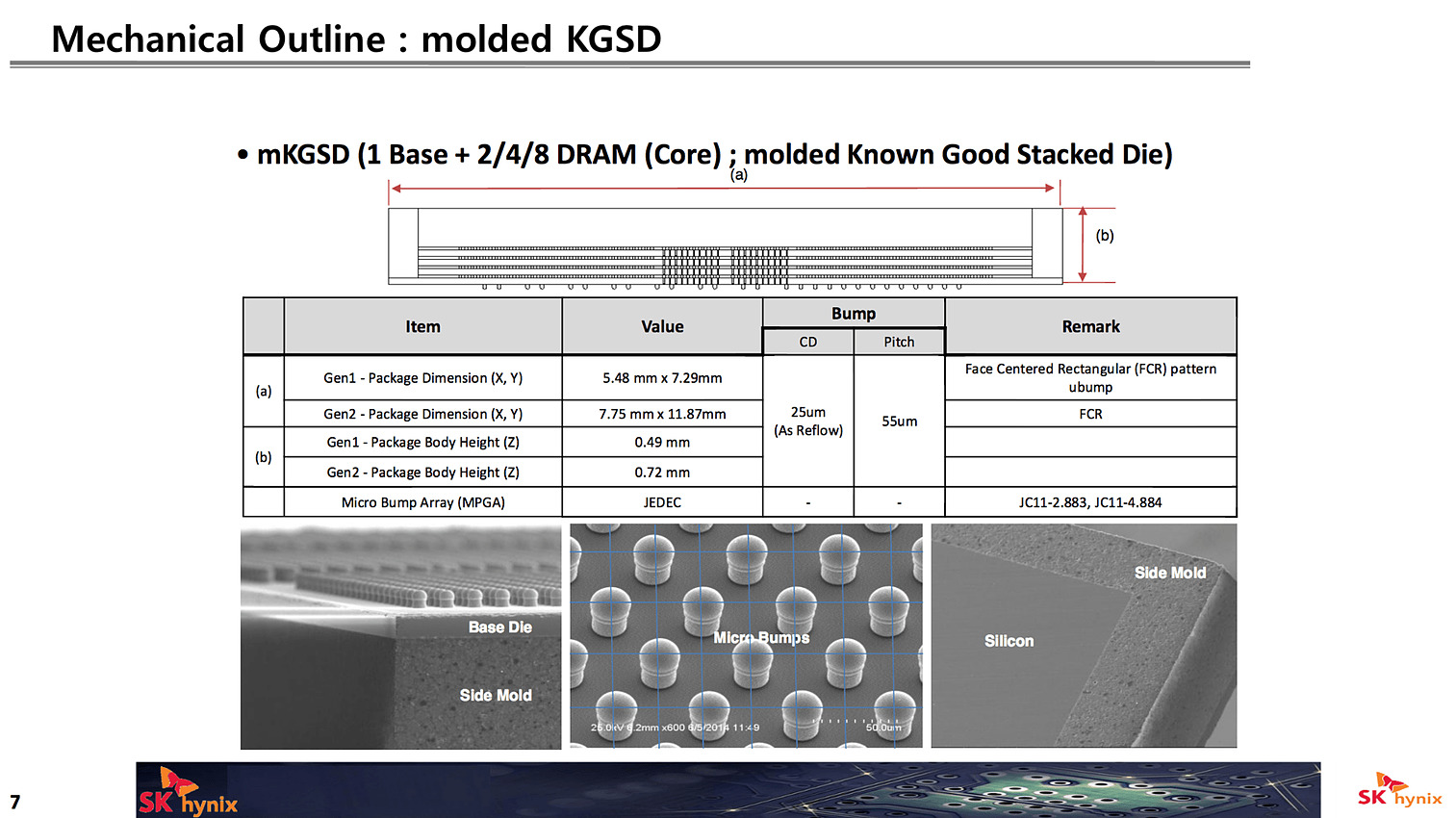

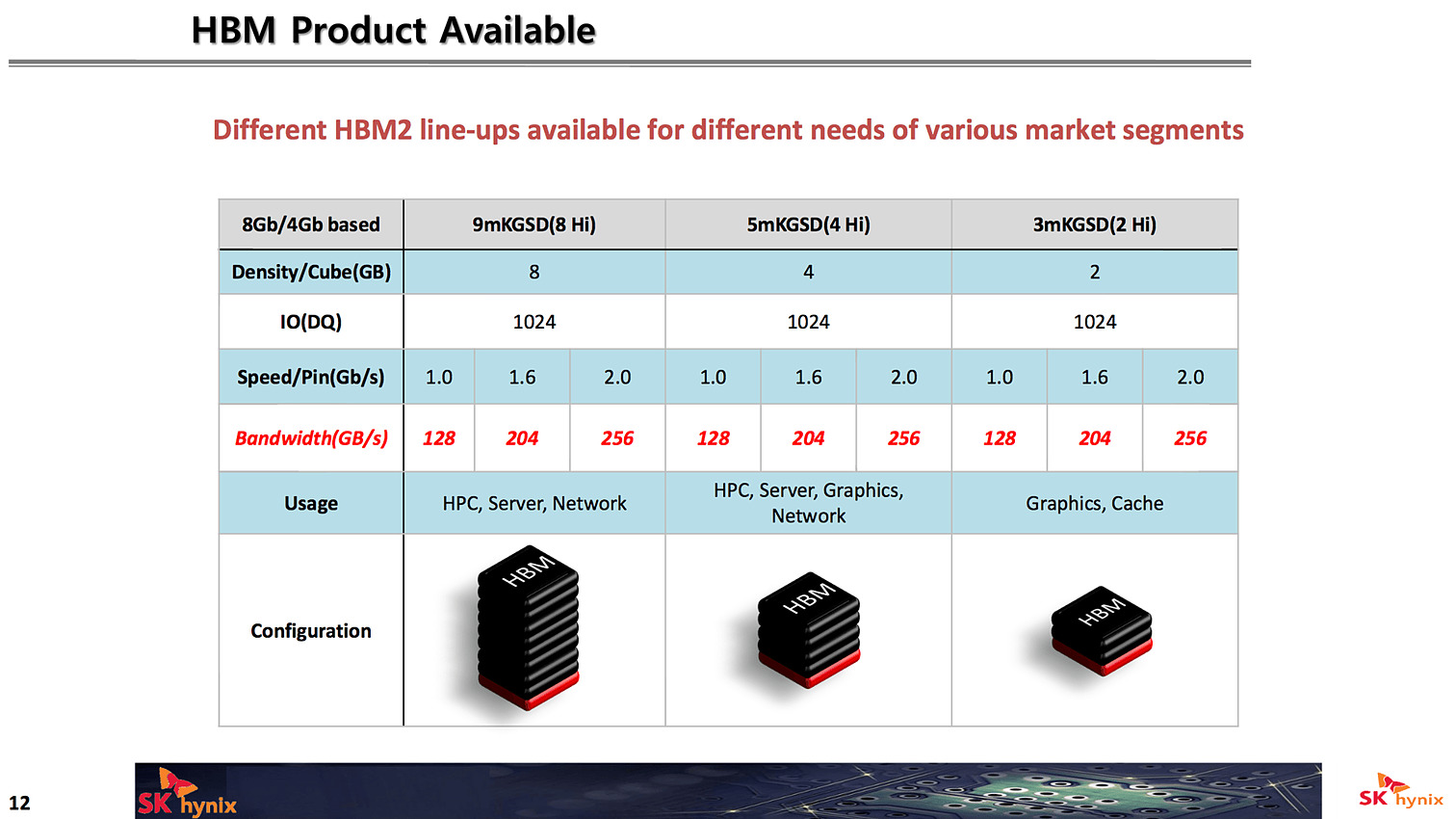

SK Hynix a confirmé ses ambitions sur la HBM2, qui pour rappel est standardisée par le JEDEC. Contrairement à la première version utilisée nottament par AMD sur les Fiji, la HBM2 utilise pour rappel des dies mémoire de 1 Go, empilés par deux, quatre ou huit. SK Hynix devrait lancer les premières puces, en version 4hi (quatre dies mémoire pour 4 Go au total) durant ce troisième trimestre.

Les versions 2Hi et 8Hi devraient suivre (soit 2 Go et 8 Go), et l'on notera qu'en plus des versions proposant 256 Go/s et 204 Go/s de bande passante, une version 128 Go/s sera également disponible au catalogue dans les différentes capacités.

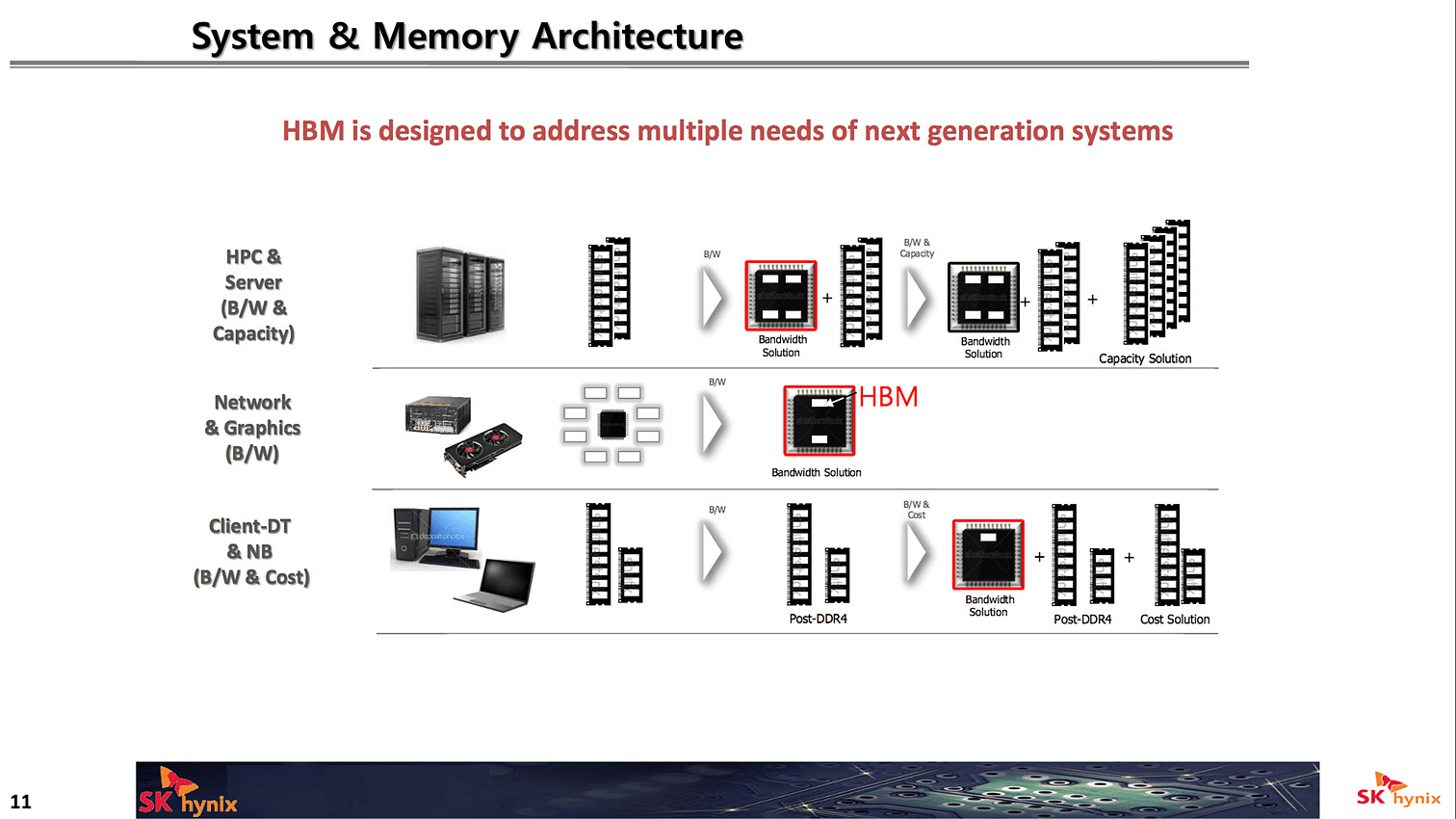

Côté utilisations, si les cartes graphiques ont été les premières à utiliser la HBM, SK Hynix envisage des utilisations dans le monde du HPC et des serveurs ou la HBM servirait de cache intermédiaire. Certaines déclinaisons de Zen pour serveurs devraient utiliser de la HBM, par exemple. SK Hynix voit également la HBM arriver en volume plus large dans les PC portables et desktop.

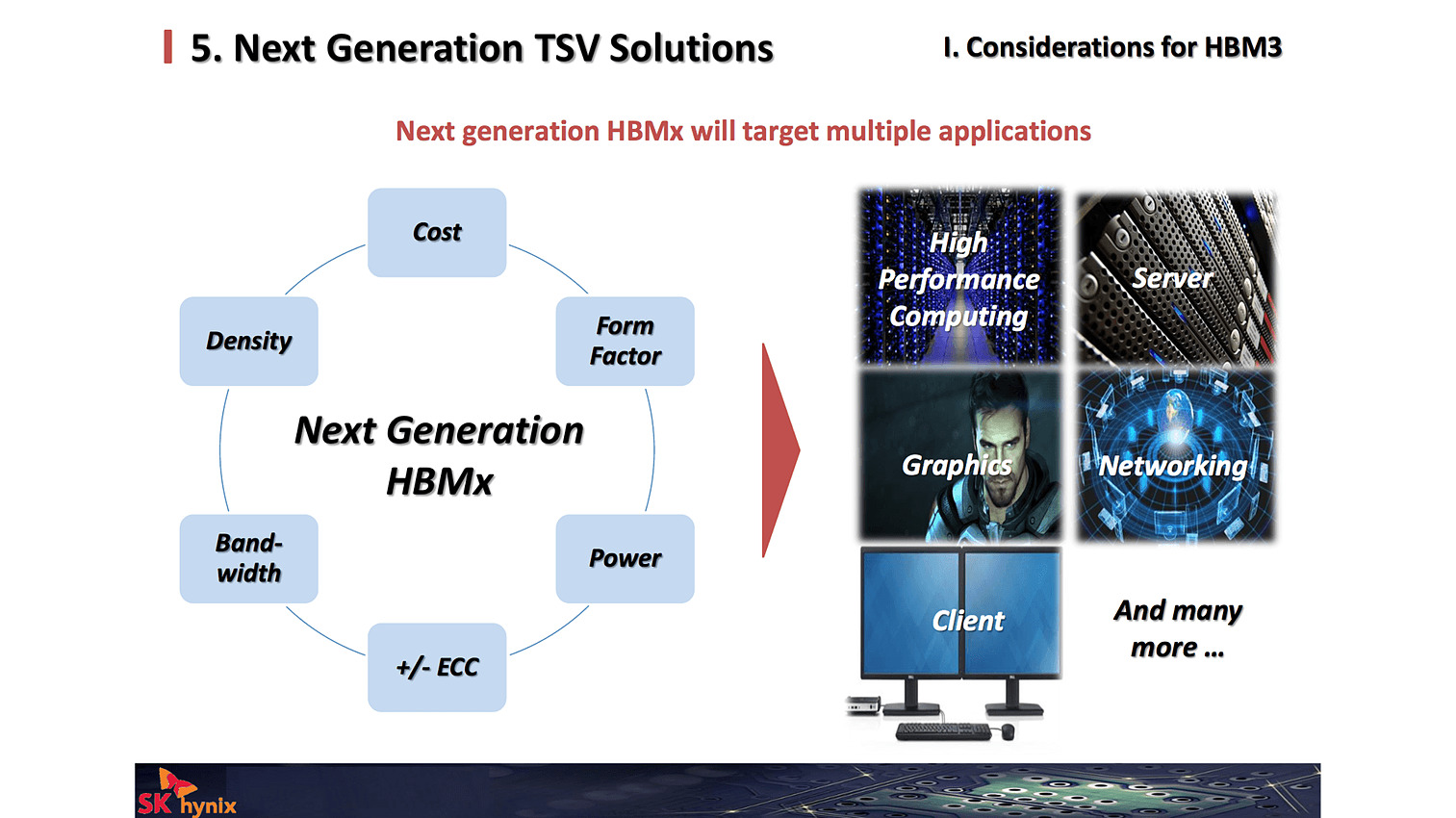

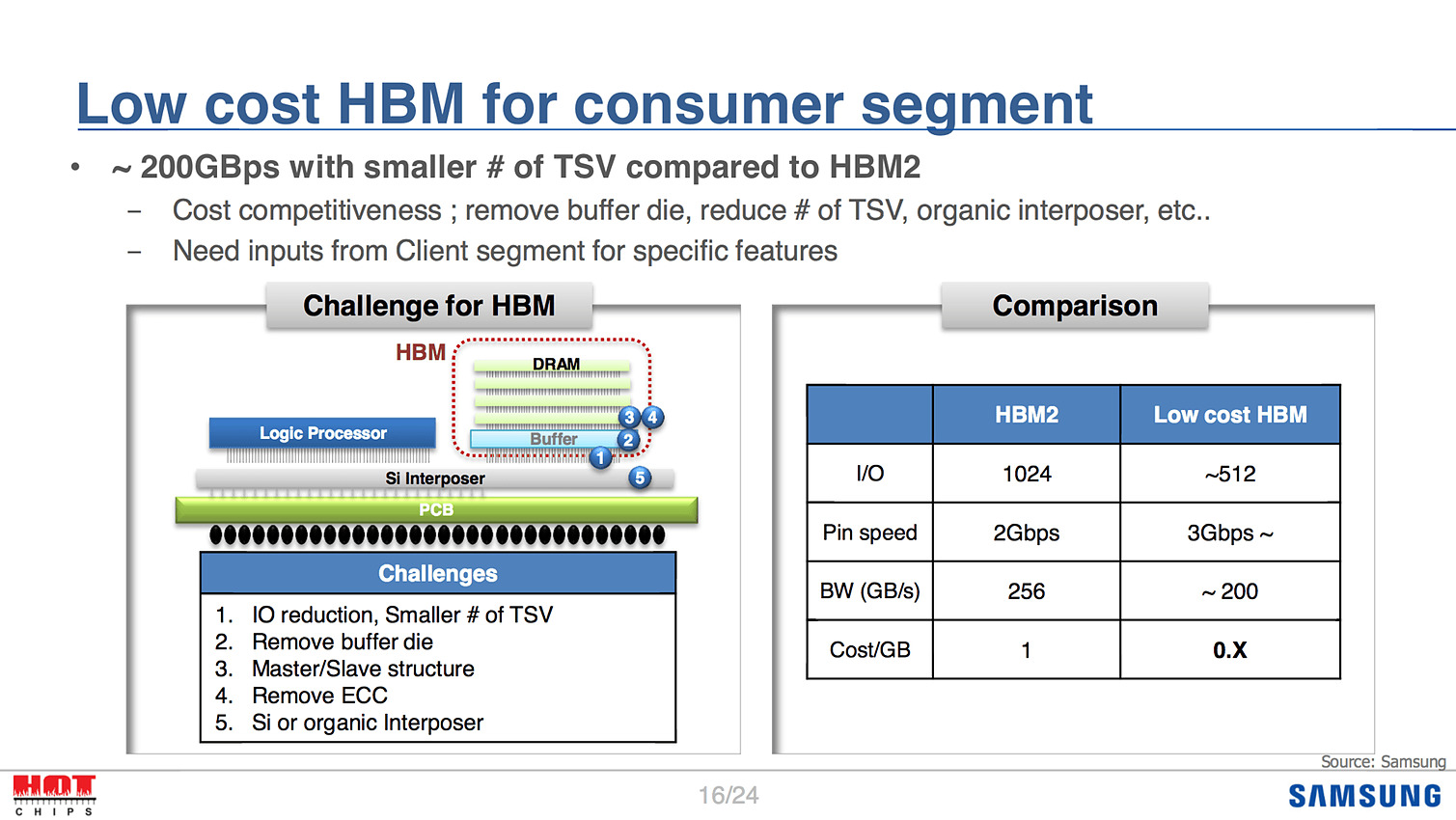

Côté Samsung, qui doit lancer aussi la HBM2 cette année, on parle surtout d'une version low cost de la HBM, qui ne serait pas de la HBM2 mais une variante plus abordable, en 512 bits (au lieu de 1024) et qui réduirait le nombre de TSV (Through Silicon Vias, les fils qui traversent les dies pour les relier les uns les autres). Le tout offrant tout de même 200 Go/s de bande passante. Un développement qui devrait s'effectuer en parallèle de celui de la HBM3 qui a pour objectif de doubler, sur le haut de gamme, la bande passante par rapport à la HBM2.