SK Hynix et Samsung parlent de HBM

Comme tous les ans, c'est à la fin de l'été que se tient la conférence Hot Chips (28ème édition) ou les divers acteurs du milieu présentent leurs nouveautés. Parmi les attractions de cette année, on attendra, dans la nuit de mardi à mercredi, "A New, High Performance x86 Core Design from AMD" qui devrait probablement nous en dire un peu plus sur Zen.

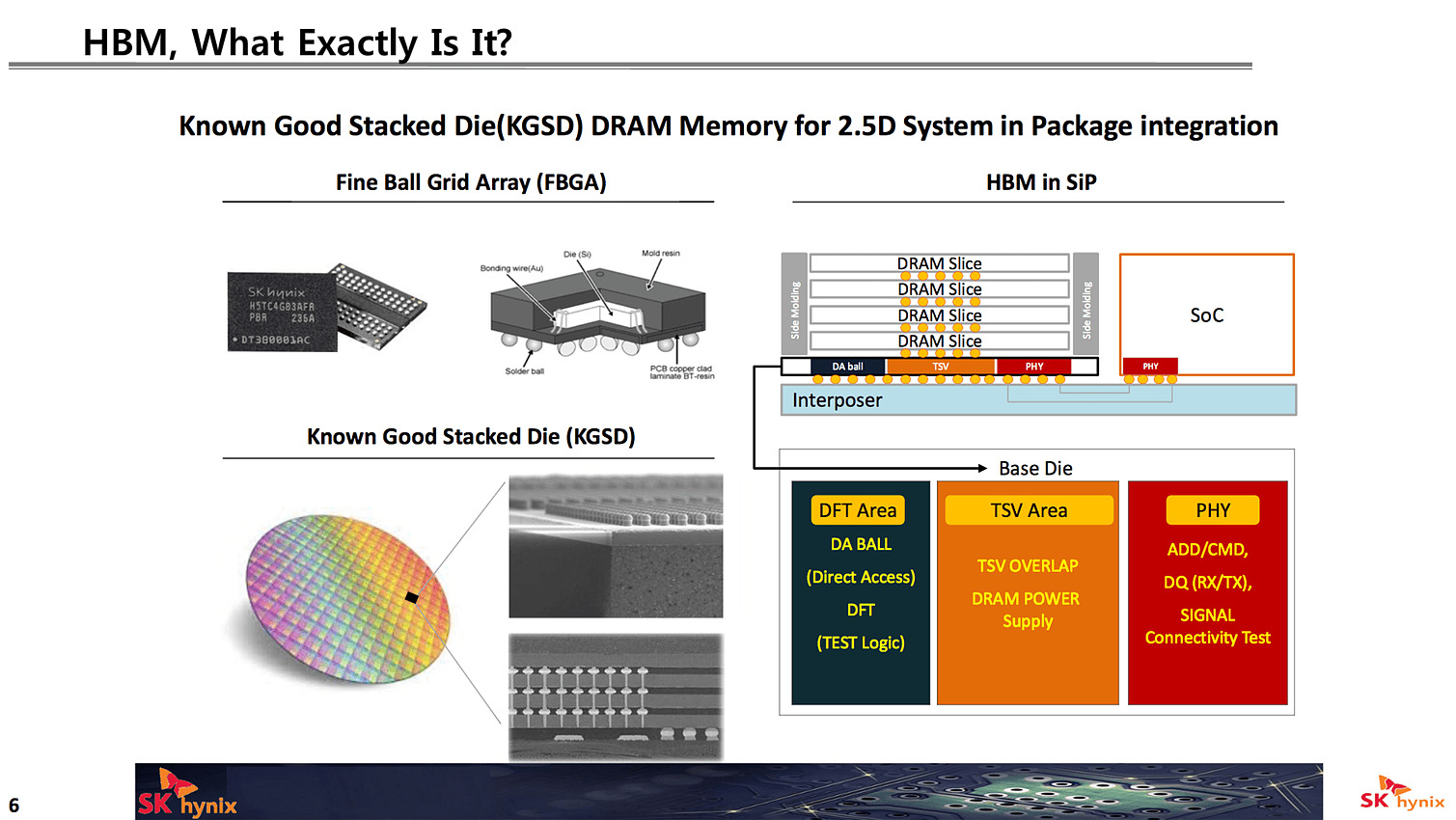

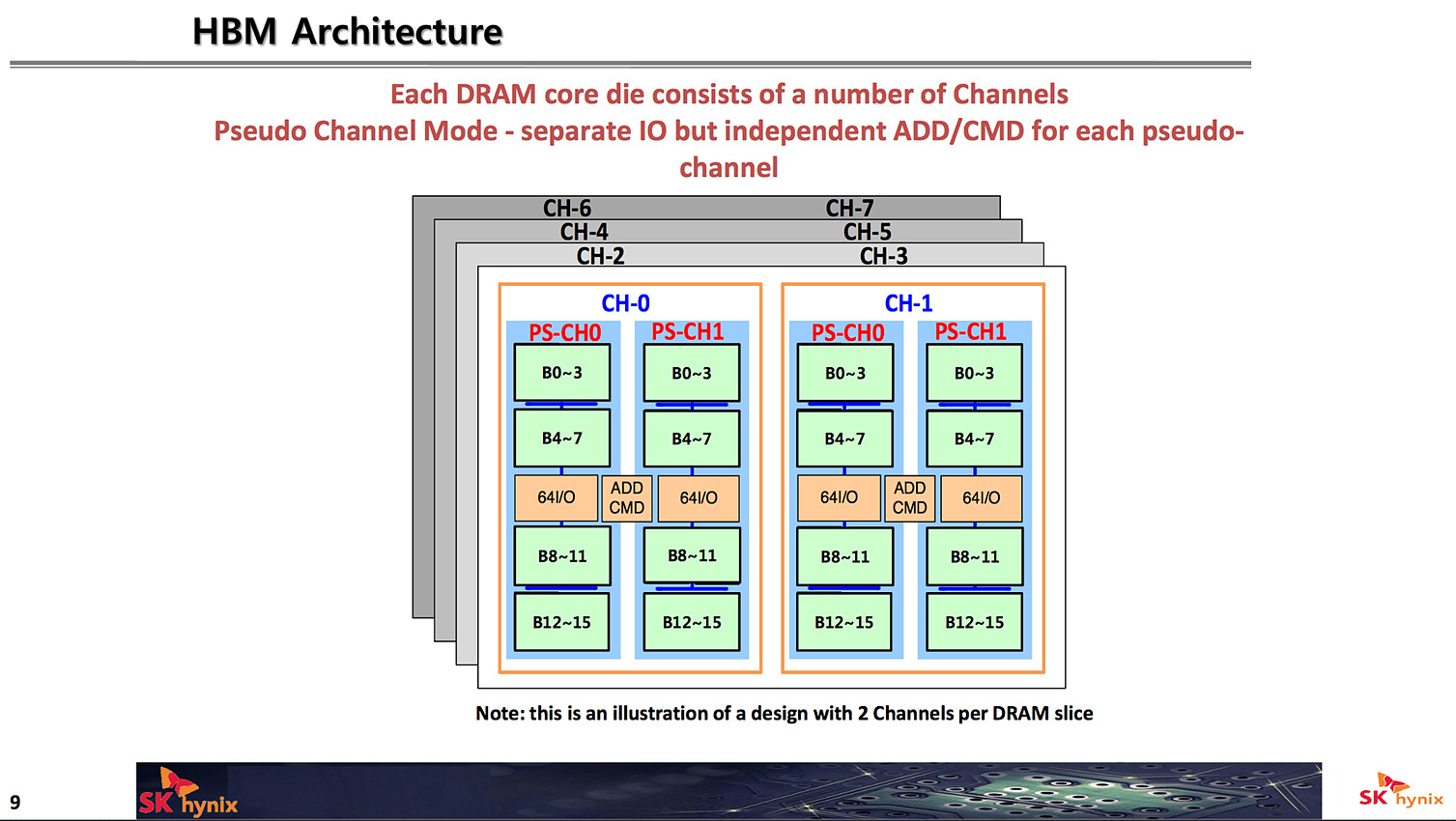

La première matinée de conférence avait lieu hier, dédiée à l'utilisation des nouvelles technologies mémoires. Chez SK Hynix et Samsung, la HBM était au programme. Pour rappel, la mémoire HBM est l'assemblage sur une même puce d'un die, en dessous, contenant les contrôleurs mémoires, et sur lequel on empile plusieurs dies de mémoire DRAM traditionnelle.

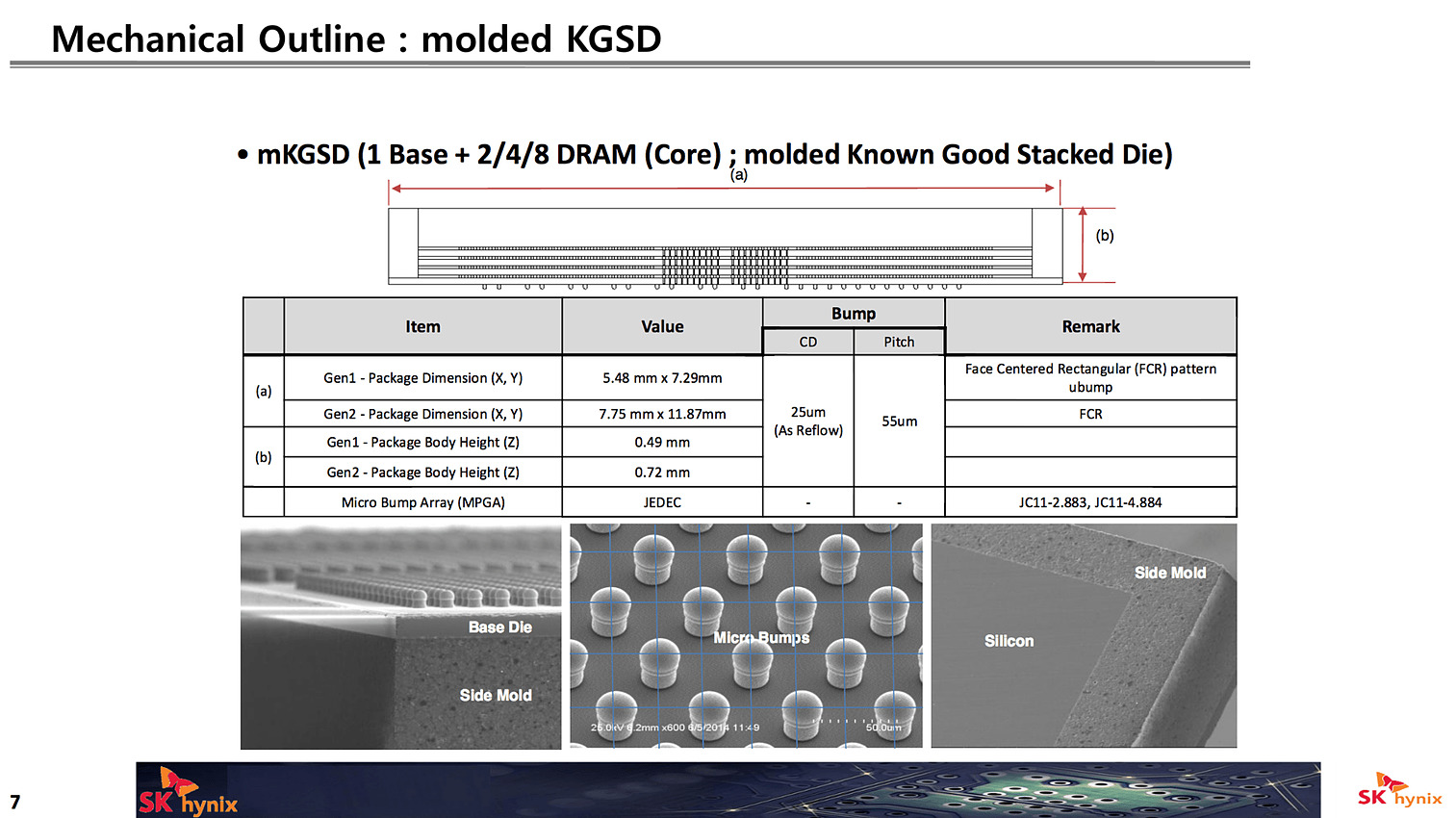

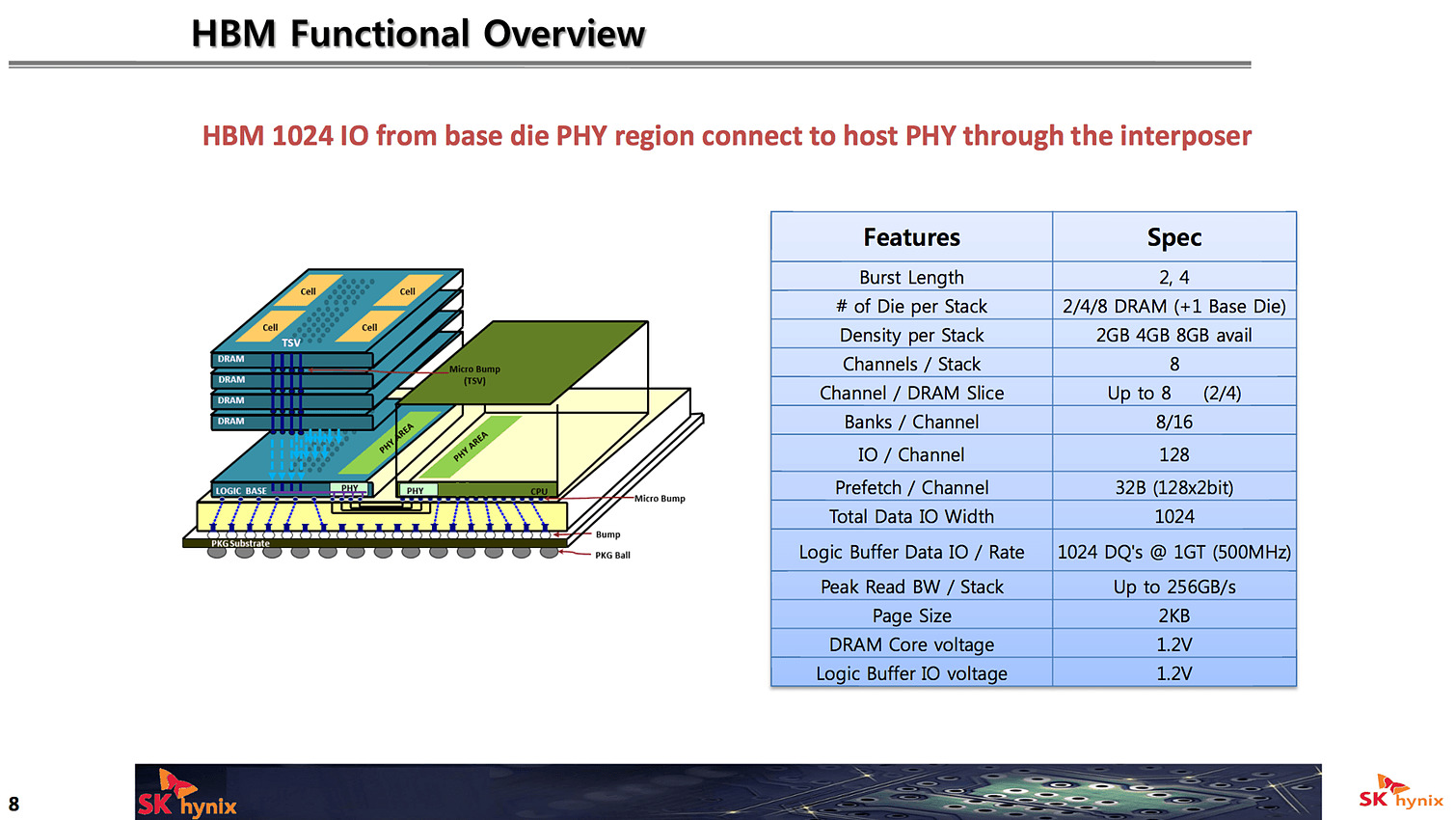

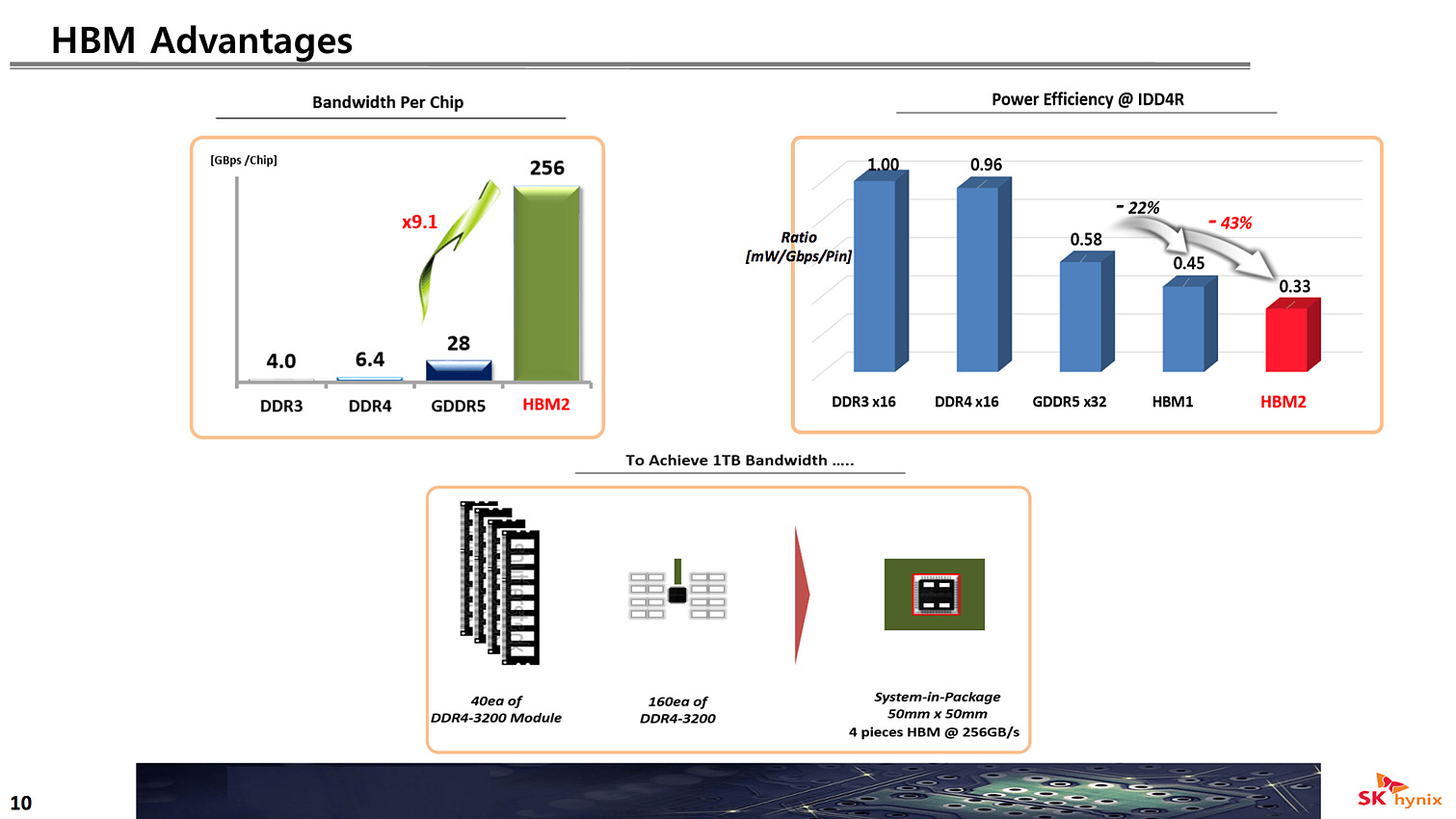

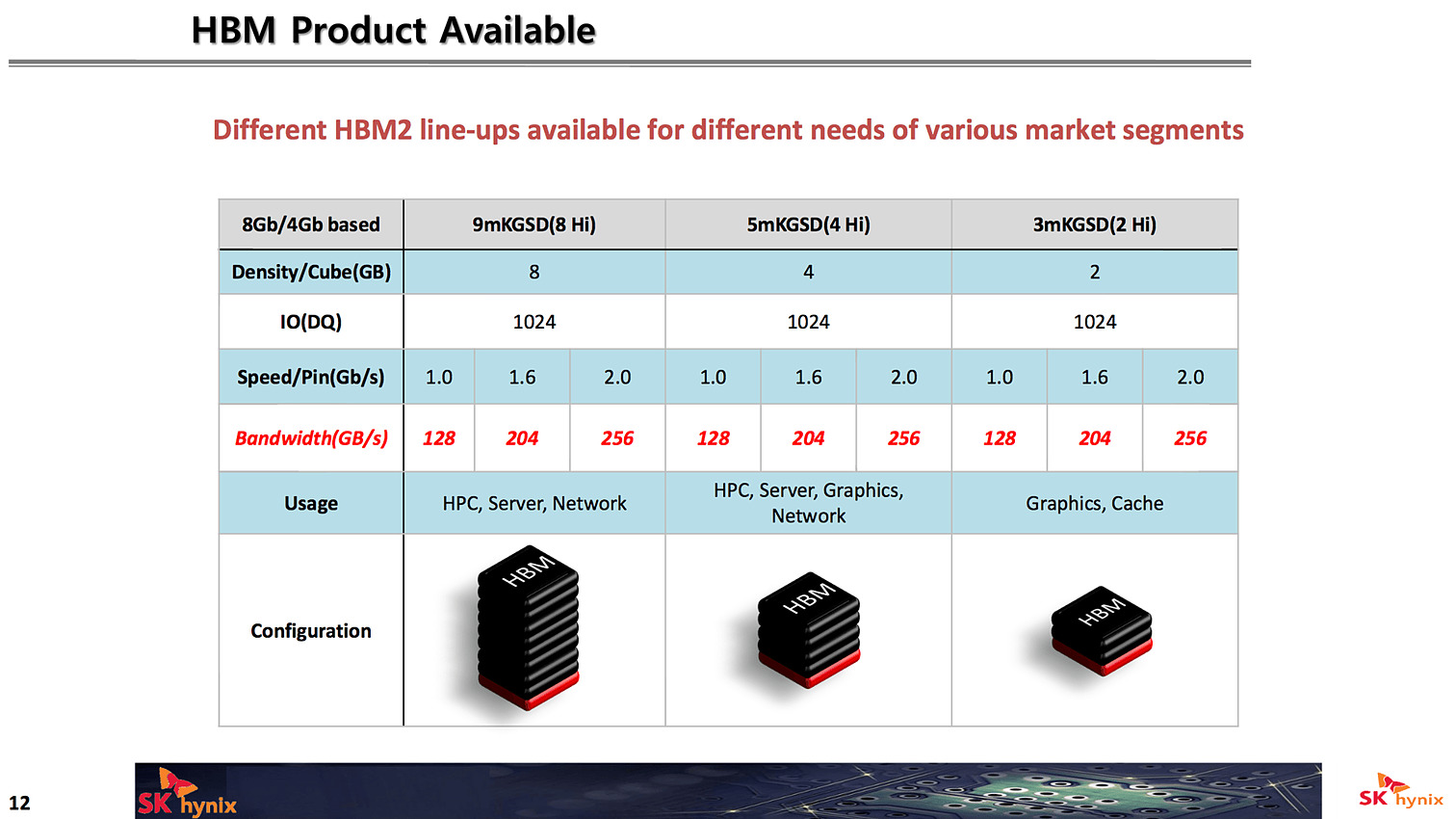

SK Hynix a confirmé ses ambitions sur la HBM2, qui pour rappel est standardisée par le JEDEC. Contrairement à la première version utilisée nottament par AMD sur les Fiji, la HBM2 utilise pour rappel des dies mémoire de 1 Go, empilés par deux, quatre ou huit. SK Hynix devrait lancer les premières puces, en version 4hi (quatre dies mémoire pour 4 Go au total) durant ce troisième trimestre.

Les versions 2Hi et 8Hi devraient suivre (soit 2 Go et 8 Go), et l'on notera qu'en plus des versions proposant 256 Go/s et 204 Go/s de bande passante, une version 128 Go/s sera également disponible au catalogue dans les différentes capacités.

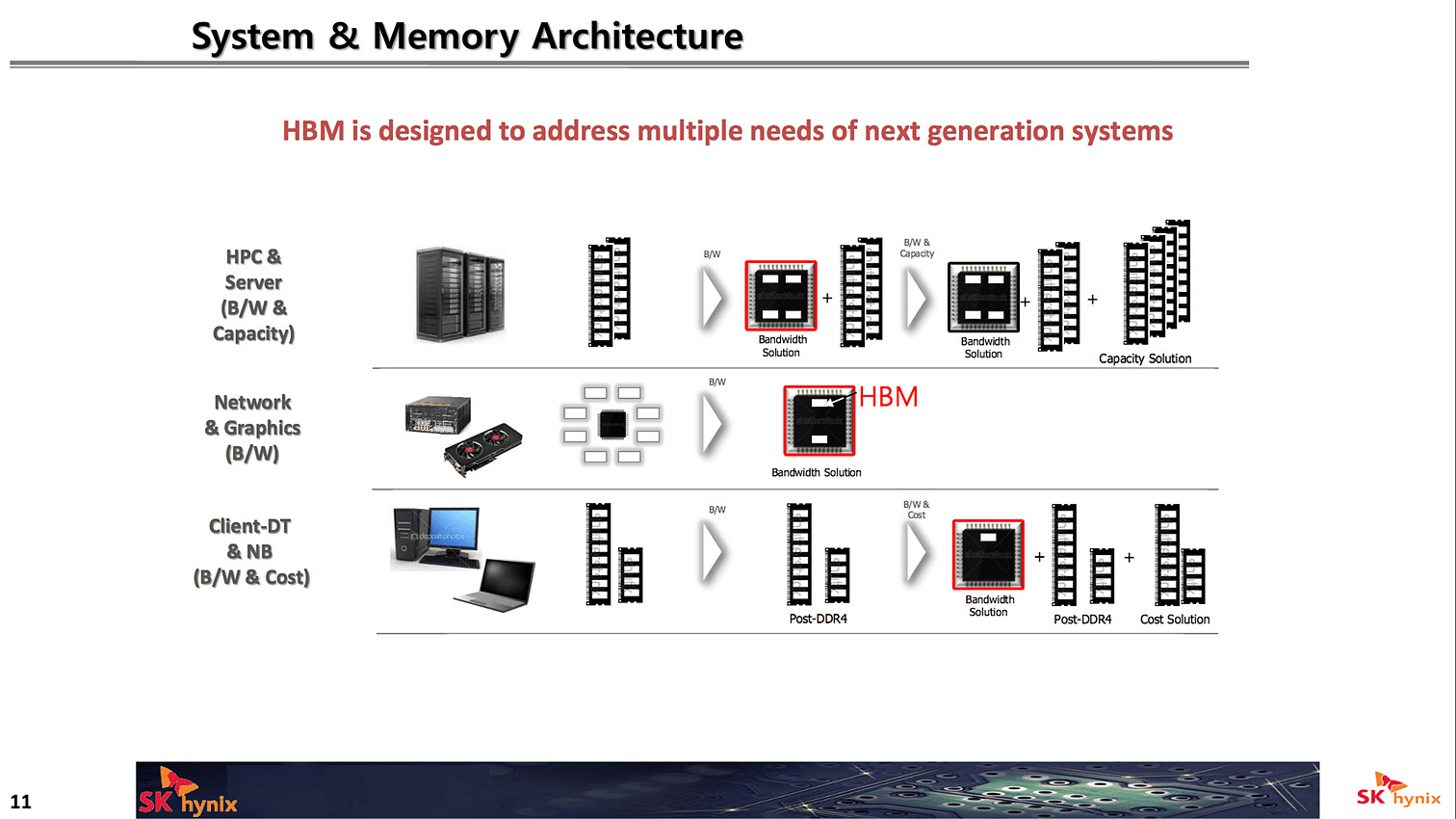

Côté utilisations, si les cartes graphiques ont été les premières à utiliser la HBM, SK Hynix envisage des utilisations dans le monde du HPC et des serveurs ou la HBM servirait de cache intermédiaire. Certaines déclinaisons de Zen pour serveurs devraient utiliser de la HBM, par exemple. SK Hynix voit également la HBM arriver en volume plus large dans les PC portables et desktop.

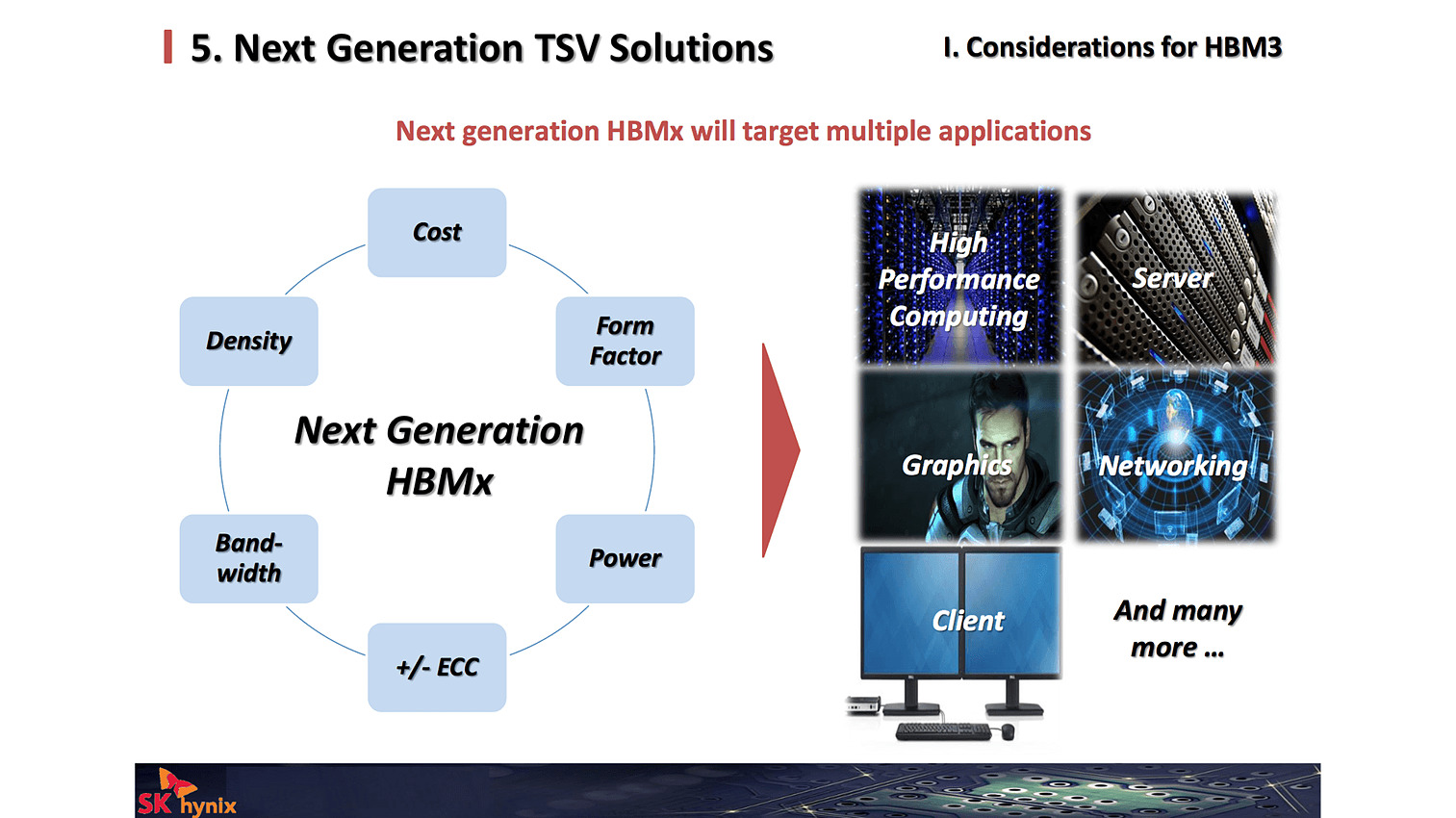

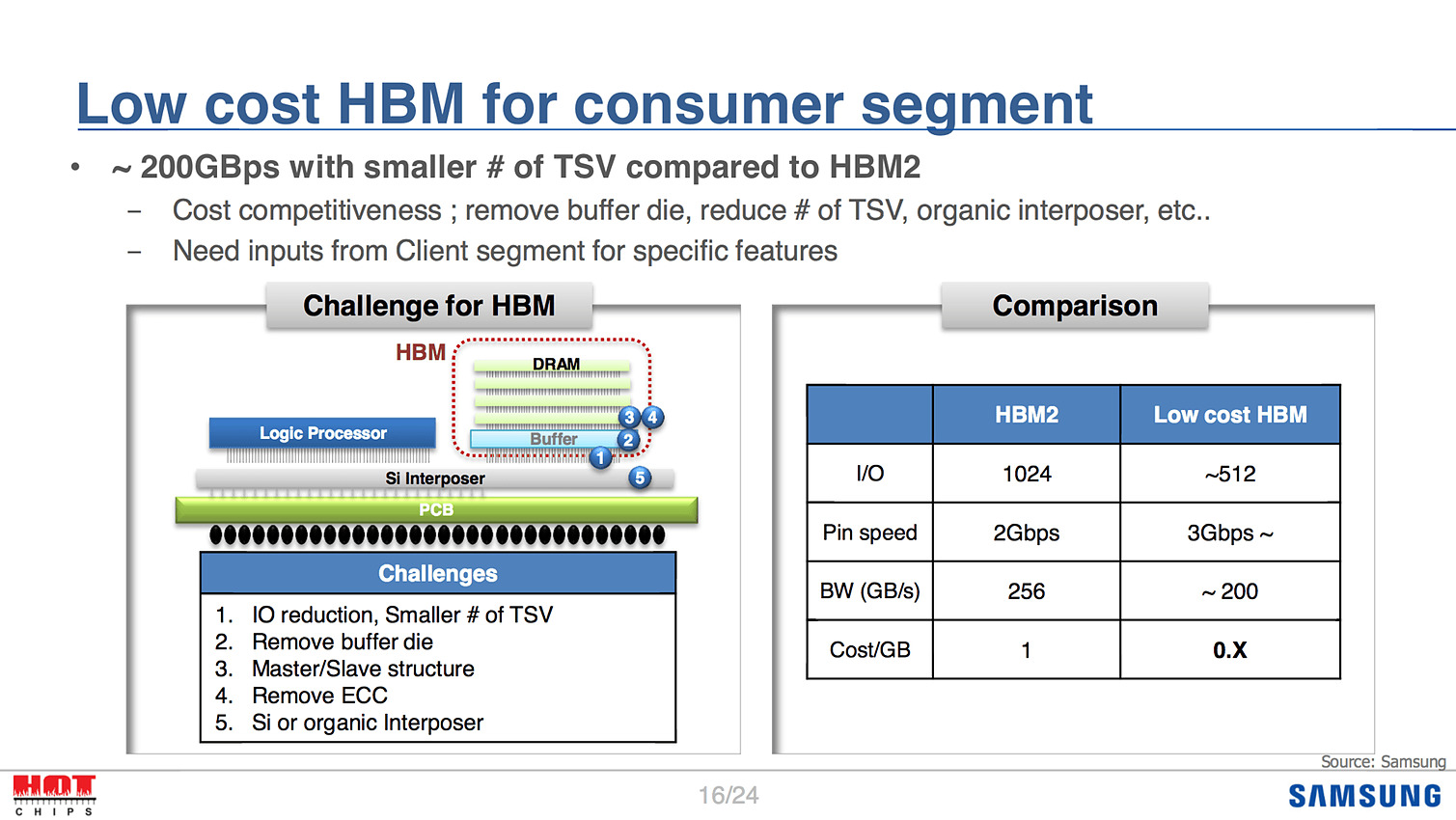

Côté Samsung, qui doit lancer aussi la HBM2 cette année, on parle surtout d'une version low cost de la HBM, qui ne serait pas de la HBM2 mais une variante plus abordable, en 512 bits (au lieu de 1024) et qui réduirait le nombre de TSV (Through Silicon Vias, les fils qui traversent les dies pour les relier les uns les autres). Le tout offrant tout de même 200 Go/s de bande passante. Un développement qui devrait s'effectuer en parallèle de celui de la HBM3 qui a pour objectif de doubler, sur le haut de gamme, la bande passante par rapport à la HBM2.

Contenus relatifs

- [+] 18/07: Samsung augmente la production de H...

- [+] 13/10: Alliance autour d'un nouveau bus mé...

- [+] 29/08: Hot Chips : M1, SVE, Parker, InFo e...

- [+] 22/08: Samsung évoque la GDDR6

- [+] 22/08: HMC, DDR5 et 3D XPoint pour Micron

- [+] 22/08: SK Hynix et Samsung parlent de HBM

- [+] 15/07: La HBM2 Hynix dispo ce troisième tr...

- [+] 26/04: AMD lance la Radeon Pro Duo à 1650

- [+] 05/04: GTC: Nvidia Tesla P100: 10 Tflops, ...

- [+] 15/03: GDC: AMD annonce la Radeon Pro Duo