Alliance autour d'un nouveau bus mémoire

Plusieurs acteurs majeurs de l'industrie viennent d'annoncer une alliance dans le but de développer une nouvelle interface mémoire. Ils se sont regroupés au sein d'un consortium baptisé Gen-Z.

La page de description du consortium insiste sur un mode de fonctionnement transparent et ouvert. Le consortium en lui même est une organisation à but non lucratif (pour les puristes, une entreprise américaine de type "not for profit"). Le mode de développement sera transparent, et le standard final sera publié, disponible et utilisable gratuitement.

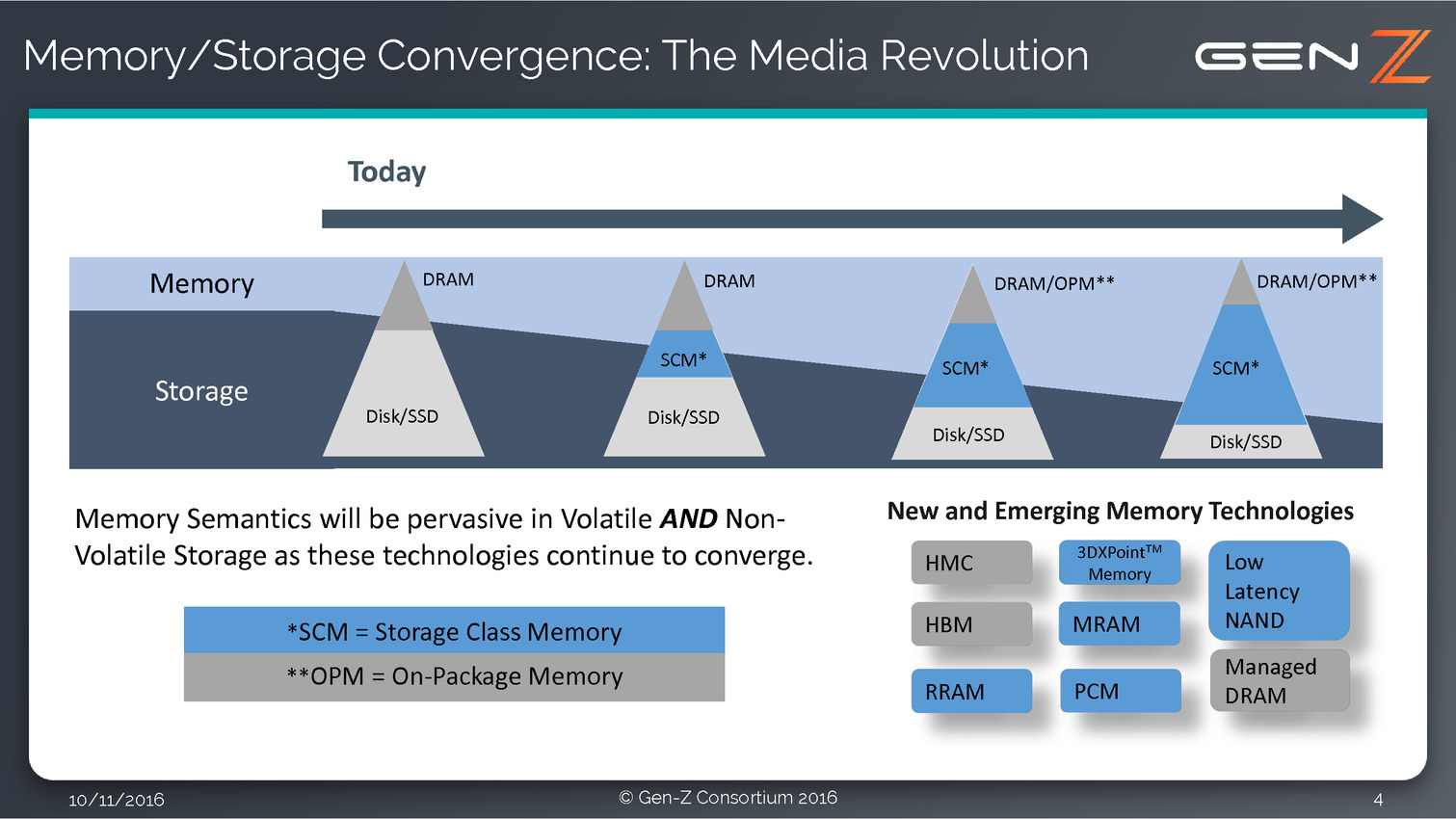

Techniquement il s'agit de proposer une nouvelle manière d'interconnecter la mémoire, ou plutôt les multiples types de mémoires qui pourront coexister à l'avenir.

Le consortium prend l'exemple des nouveaux "types" de mémoires, appelés SCM (Storage Class Memory) comme peuvent l'être les RRAM, MRAM, ou les implémentations commerciales annoncées comme 3D XPoint chez Intel/Micron ou la Z-NAND de Samsung. Ces nouveaux types de mémoires viennent s'ajouter à la mémoire traditionnelle (DRAM) qui voit aussi arriver de nouvelles variantes (HBM ou HMC).

L'idée de base du consortium est de proposer une interface avec des commandes très simples, proches de celles utilisées pour la DRAM, mais qui puissent être utilisées aussi bien au sein d'un package, sur la carte mère, ou au delà (communication entre serveurs dans un data center). Le tout se doit de rester compatible avec l'existant, y compris les systèmes d'exploitations qui pourront exploiter ces nouvelles mémoires de manière transparente. Un but assez noble tant la question de comment adresser ce nouveau tiers de mémoire avait été évitée jusqu'ici.

Le consortium annonce qu'il utilisera entre autre le protocole IEEE 802.3 (Ethernet) comme protocole de communication interne (on pourra aussi utiliser Ethernet pour la couche physique de transport). En plus des protocoles, un nouveau connecteur devrait être annoncé pour tenter de standardiser ces futurs types de mémoire, il supportera jusque 112 GT/s.

Les objectifs fixés sont particulièrement audacieux, et on ne pourra que se féliciter de voir tant d'acteurs majeurs de l'industrie s'associer pour tenter de proposer un nouveau standard :

L'absent le plus notable est Intel, et il est difficile de ne pas voir cette alliance comme formée contre la firme de Santa Clara qui a tendance à développer ses bus de manière propriétaires, particulièrement pour tout ce qui touche au monde serveur.

Il est tout de même intéressant de voir que Micron, partenaire d'Intel sur 3D Xpoint est présent dans le consortium (3D Xpoint est même mentionné dans les slides de présentation). Il sera intéressant de suivre l'évolution de ce standard qui pourrait apporter des solutions concrètes aux problématiques d'interconnexions.

Vous pouvez retrouver la présentation du consortium ci dessous :

Contenus relatifs

- [+] 18/07: Samsung augmente la production de H...

- [+] 17/03: La MRAM débarque sur un SSD PCIe

- [+] 17/10: 16 et 32 Go pour les premiers Intel...

- [+] 13/10: Alliance autour d'un nouveau bus mé...

- [+] 29/08: Hot Chips : M1, SVE, Parker, InFo e...

- [+] 22/08: Samsung évoque la GDDR6

- [+] 22/08: HMC, DDR5 et 3D XPoint pour Micron

- [+] 22/08: SK Hynix et Samsung parlent de HBM

- [+] 11/08: V-NAND Gen4 et Z-NAND pour Samsung

- [+] 10/08: PRAM 3D XPoint QuantX pour Micron