Intel Core i7-4770K et i5-4670K : Haswell en test

Publié le 01/06/2013 par Guillaume Louel et Marc Prieur

Si les améliorations du côté de l'architecture CPU sur Haswell étaient particulièrement nombreuses, du côté de l'IGP intégré les modifications sont un peu plus légères. Commençons d'abord par les API, on retrouve ici la gestion de DirectX 11.1, d'OpenGL 4.0 et d'OpenCL 1.2.

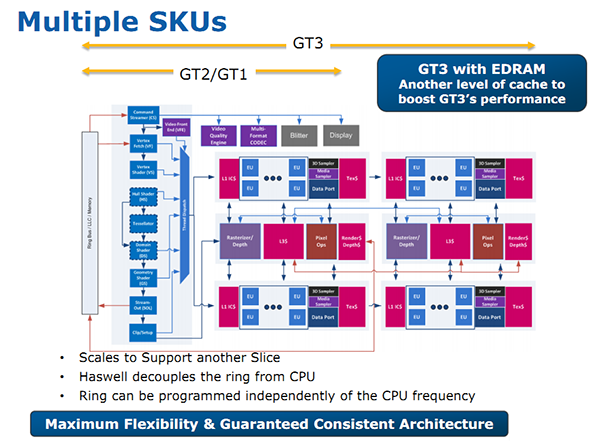

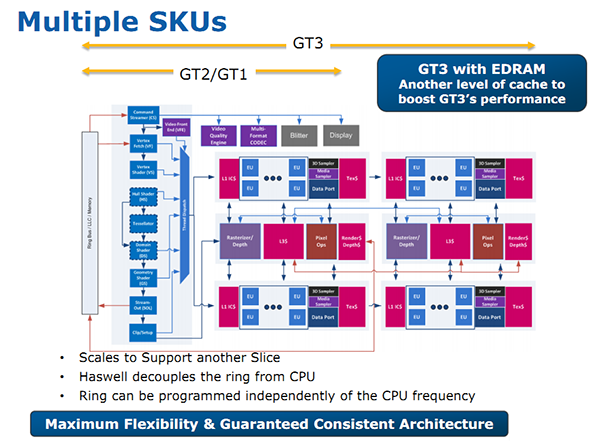

Avec Haswell, Intel a décidé de rendre son architecture GPU un peu plus flexible. En plus des deux versions traditionnelles, GT2 et GT1 qui profitent au passage d'une hausse notable de leurs unités, Intel rajoute une version GT3 qui double le nombre d'unités d'exécution (passant de 20 à 40) :

- GT1 : 10 Execution Units (6 sur IVB)

- GT2 : 20 Execution Units (16 sur IVB)

- GT3 : 40 Execution Units

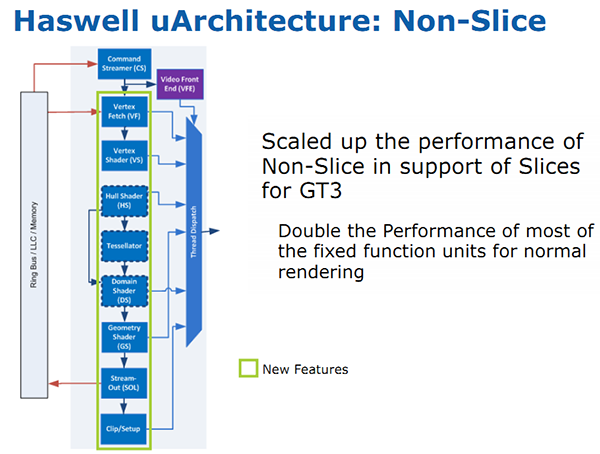

Comme indiqué précédemment, Intel a découplé la fréquence du ring bus de celle des curs processeurs, ce qui permet un peu plus de flexibilité pour le GPU lors des accès mémoire. Connecté au ring bus se trouve le gestionnaire de commandes, tout en haut du pipeline graphique.

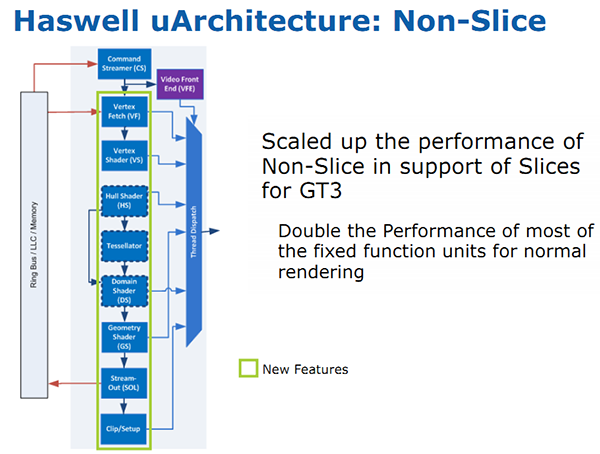

Sur ce dernier, Intel indique avoir ajouté un gestionnaire de ressource qui effectue ainsi un certain nombre de tâches qui étaient effectuée par le pilote précédemment (côté CPU). Les autres parties fixes du pipeline voient également une amélioration de leur performances, certaines étant doublées selon Intel qui ne précise cependant pas lesquelles.

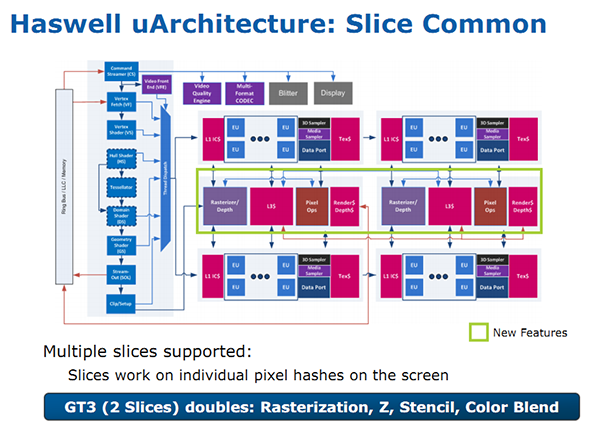

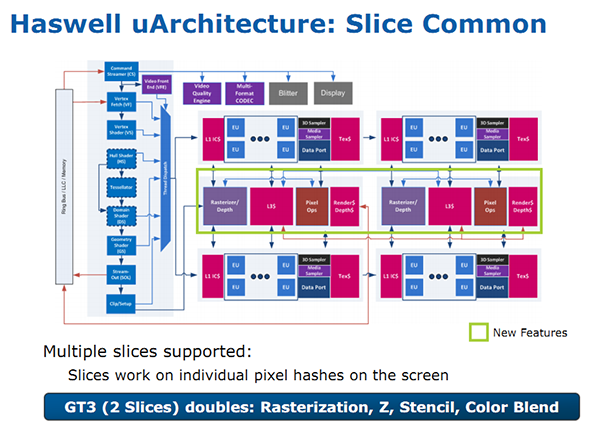

Pour ce qui s'agit des shaders, les diverses étapes de rendues peuvent dispatcher des threads vers le bloc de la puce qui continent les unités d'exécution, ce qu'Intel appelle désormais des slices. Dans le cas de GT3 ou deux slices sont présentes, chaque slice travaillera sur des pixels différents. Les slices disposent de rasterizers et de buffers Z, stencil et color blend indépendants.

Le dernier changement majeur concerne les performances du sampler de textures dont le débit à été multiplié par quatre pour certains formats de textures (là encore, non précisés).

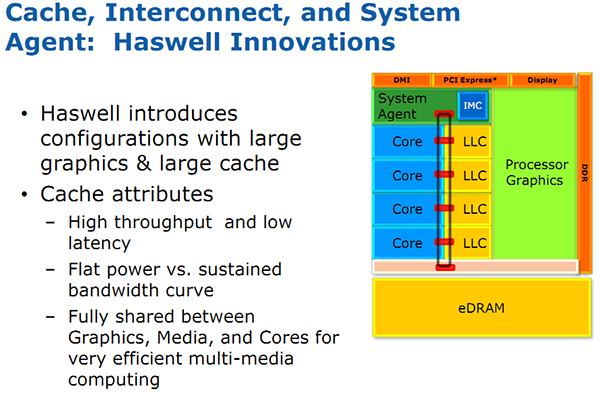

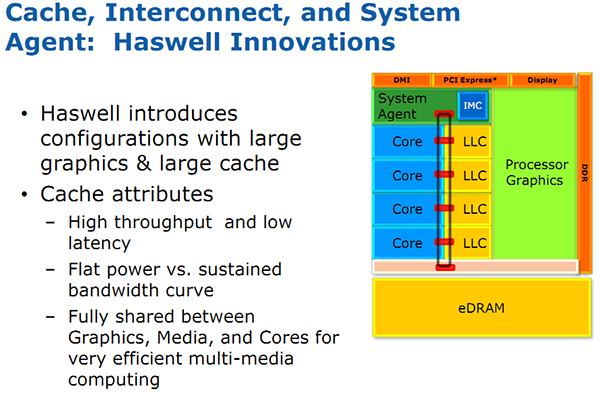

L'utilisation du nom LLC pour distinguer le cache de niveau trois est légèrement abusive dans Haswell, puisque ce dernier peut être configuré avec un cache de niveau 4. C'est l'une des nouveautés les plus originales, en effet Intel proposera des SKU utilisant GT3e, une version de GT3 accompagnée d'un puce d'eDRAM (de la mémoire DRAM embarquée) ajoutée au package.

Sur ce point, Intel est pour le moins muet puisque le constructeur n'a rien confirmé sur les caractéristiques des puces intégrées. Il s'agit en fait de 128 Mo de mémoire interfacée en 512 bits offrant une bande passante de 50 Go /s dans chaque sens (100 Go /s au total). Gravée en 22nm, cette eDRAM mesure 84mm² pour une consommation de 0.5-1w au repos et 3.5-4.5 watts en charge (source ).

Sur ce rare schéma fourni par Intel on peut voir que le ring bus s'arrêterait sur un bloc d'interface qui vient s'insérer à la place du stop dévolu précédemment à l'IGP. On ne sait pas cependant s'il s'agit d'une simple illustration ou non, mais la logique voudrait que ce bloc serve d'interconnexion directe entre le GPU et l'eDRAM sans devoir passer par le ring bus. Notez cependant que l'eDRAM est considérée comme le système comme un cache de niveau 4, au dessus du LLC, et qu'il est donc directement accessible aux cores CPU, ce qui ne sera probablement pas sans avoir un impact sur les performances CPU dans certains benchs. Intel indique que le cache est complètement partagé entre CPU et IGP, même si l'on ne sait pas quelle sera le niveau de priorité respectifs qui leur seront donnés.

Si Intel reste peut loquace sur le sujet, c'est avant tout parce que ces versions se retrouveront exclusivement dans des puces au format BGA (directement soudées sur la carte mère), que ce soit dans le but d'être intégrées dans des PC portables (plutôt haut de gamme) ou alors dans des machines tout en un (type iMac).

On ne peut donc qu'être déçu de ne pas avoir plus de détails sur le sujet pour l'instant, on peut penser que cela ne durera pas forcément longtemps et qu'Intel devrait annoncer plus de détails, par exemple autour du lancement d'un de ses partenaires.

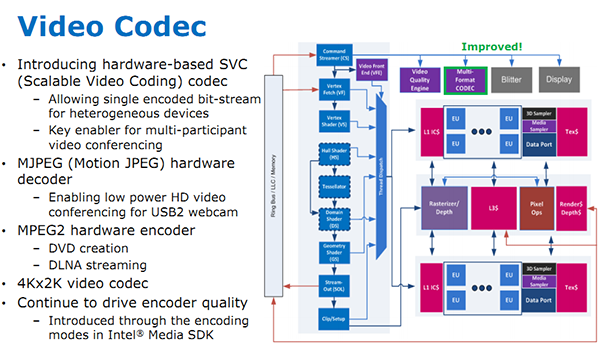

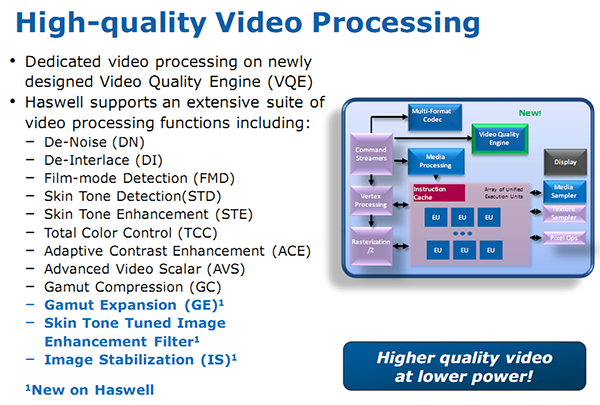

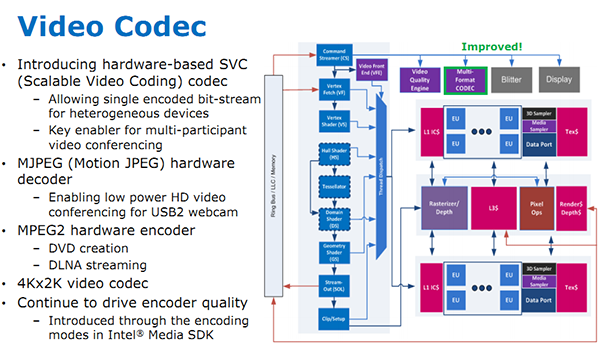

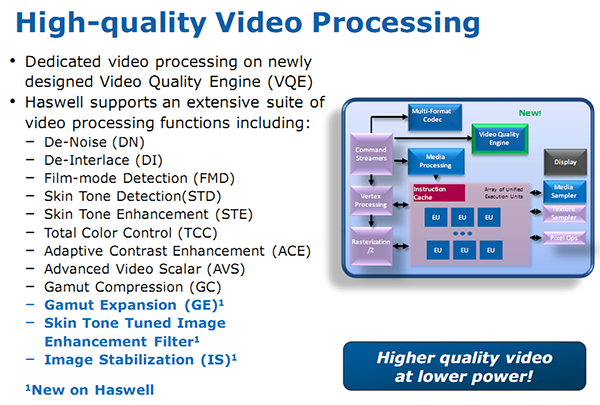

Au sein du GPU, on retrouve toujours QuickSync, la technologie de décodage et encodage vidéo d'Intel. Il s'agit de blocs d'unités fixes qui prennent en charge une grande partie des tâches de décodage et d'encodage vidéo et qui peuvent également envoyer des tâches de traitements vidéo sur les unités d'exécution (par exemple pour réduire le bruit ou désentrelacer les vidéos).

Du côté des décodeurs, Intel ajoute la gestion du format MJPEG surtout utilisé dans les appareils d'entrée de gamme. Côté encodage, deux nouveaux formats à noter, la première est l'arrivée du MPEG-2 (le standard utilisé sur les DVD) mais aussi celle du SVC, une version "scalable" du codec AVC/H.264. On retrouve avec SVC un container prévu pour le streaming de vidéo, et surtout au niveau du contenu, la possibilité de dégrader progressivement la qualité en fonction de la bande passante. L'autre nouveauté notable concerne la gestion du 4K à tous les niveaux, aussi bien niveau décodage, encodage qu'affichage.

Côté post processing, Intel étend les possibilités offertes avec l'ajout de nouveaux filtres, les plus notables sont la conversion de frame rate et la stabilisation d'images.

Qu'il s'agisse des filtres ou des codecs, Intel expose toutes les possibilités de QuickSync pour les développeurs au sein de son MediaSDK. Il est à noter qu'Intel dit proposer un peu plus d'options pour les développeurs dans le but d'améliorer la qualité, ce sur quoi nous reviendrons en pratique. Autre point, Intel dit travailler avec différents acteurs de l'open source, notamment les développeurs de HandBrake pour proposer un support de QuickSync dans leur logiciel. Une licence spécifique Open Source est proposée par le constructeur pour la version 2013 de son MediaSDK, un bon point.

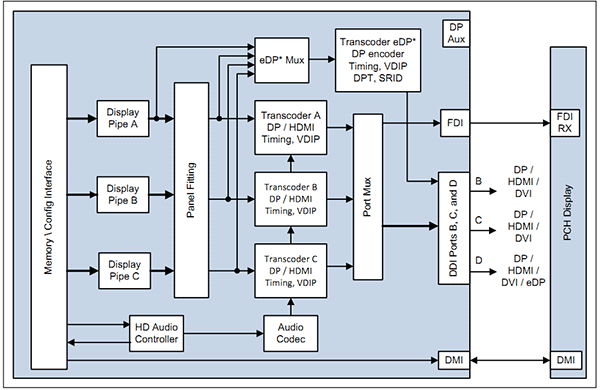

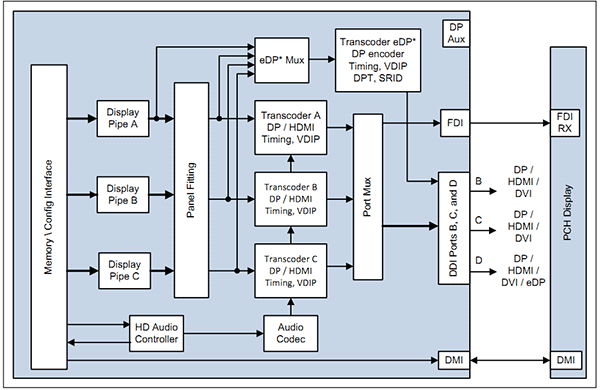

La gestion des écrans sur les plateformes précédentes d'Intel était relativement complexe puisque le signal vidéo était retransmis du processeur vers le chipset par un lien FDI, le chipset disposant d'une gestion interne. Tout ceci évolue dans Haswell, le processeur propose désormais quatre brins DDI qui pourront être utilisés pour configurer trois écrans au maximum. Il est possible de mutualiser les brins en effet pour atteindre des résolutions plus élevées (comme le support du 4k). Ces brins DDI sont uniquement utilisables pour des sorties numériques, à savoir DisplayPort, HDMI et DVI.

En parallèle, Intel utilise toujours un brin FDI qui est relié au chipset, ce brin étant utilisé pour une éventuelle sortie VGA (analogique) gérée directement par le chipset.

Côté nombre d'écrans, Haswell dispose de trois "Display Pipe" qui pourront être utilisés en simultanée pour piloter trois écrans physiques. Il est désormais possible en effet d'utiliser trois sorties en simultanée, y compris de mixer VGA et deux sorties numériques, ou trois sorties numériques. Sur ce dernier point, la datasheet d'Intel est quelque peu cryptique indiquant que toutes les permutations sont autorisées, sauf un mélange de HDMI et de DVI. Ce que nous en comprenons, c'est que pour utiliser trois sorties numériques, au minimum l'une d'entre elle doit être de type DisplayPort. Côté résolutions maximales, on peut atteindre 3840x2160 en 60Hz en DisplayPort, et 4096x2304 en 24 Hz (4k) et 2560x1600 à 60 Hz en HDMI/DVI. Notez enfin que le contrôleur HD Audio gère deux streams audio simultanés qui peuvent être assignés sur n'importe lequel des trois ports DDI.

Les améliorations de l'architecture CPU

LGA 1150, Régulateur de tension intégré

Les améliorations de l'architecture CPU

LGA 1150, Régulateur de tension intégré

Avec Haswell, Intel a décidé de rendre son architecture GPU un peu plus flexible. En plus des deux versions traditionnelles, GT2 et GT1 qui profitent au passage d'une hausse notable de leurs unités, Intel rajoute une version GT3 qui double le nombre d'unités d'exécution (passant de 20 à 40) :

- GT1 : 10 Execution Units (6 sur IVB)

- GT2 : 20 Execution Units (16 sur IVB)

- GT3 : 40 Execution Units

Comme indiqué précédemment, Intel a découplé la fréquence du ring bus de celle des curs processeurs, ce qui permet un peu plus de flexibilité pour le GPU lors des accès mémoire. Connecté au ring bus se trouve le gestionnaire de commandes, tout en haut du pipeline graphique.

Sur ce dernier, Intel indique avoir ajouté un gestionnaire de ressource qui effectue ainsi un certain nombre de tâches qui étaient effectuée par le pilote précédemment (côté CPU). Les autres parties fixes du pipeline voient également une amélioration de leur performances, certaines étant doublées selon Intel qui ne précise cependant pas lesquelles.

Pour ce qui s'agit des shaders, les diverses étapes de rendues peuvent dispatcher des threads vers le bloc de la puce qui continent les unités d'exécution, ce qu'Intel appelle désormais des slices. Dans le cas de GT3 ou deux slices sont présentes, chaque slice travaillera sur des pixels différents. Les slices disposent de rasterizers et de buffers Z, stencil et color blend indépendants.

Le dernier changement majeur concerne les performances du sampler de textures dont le débit à été multiplié par quatre pour certains formats de textures (là encore, non précisés).

eDRAM : (trop) peu de détails

L'utilisation du nom LLC pour distinguer le cache de niveau trois est légèrement abusive dans Haswell, puisque ce dernier peut être configuré avec un cache de niveau 4. C'est l'une des nouveautés les plus originales, en effet Intel proposera des SKU utilisant GT3e, une version de GT3 accompagnée d'un puce d'eDRAM (de la mémoire DRAM embarquée) ajoutée au package.

Sur ce point, Intel est pour le moins muet puisque le constructeur n'a rien confirmé sur les caractéristiques des puces intégrées. Il s'agit en fait de 128 Mo de mémoire interfacée en 512 bits offrant une bande passante de 50 Go /s dans chaque sens (100 Go /s au total). Gravée en 22nm, cette eDRAM mesure 84mm² pour une consommation de 0.5-1w au repos et 3.5-4.5 watts en charge (source ).

Sur ce rare schéma fourni par Intel on peut voir que le ring bus s'arrêterait sur un bloc d'interface qui vient s'insérer à la place du stop dévolu précédemment à l'IGP. On ne sait pas cependant s'il s'agit d'une simple illustration ou non, mais la logique voudrait que ce bloc serve d'interconnexion directe entre le GPU et l'eDRAM sans devoir passer par le ring bus. Notez cependant que l'eDRAM est considérée comme le système comme un cache de niveau 4, au dessus du LLC, et qu'il est donc directement accessible aux cores CPU, ce qui ne sera probablement pas sans avoir un impact sur les performances CPU dans certains benchs. Intel indique que le cache est complètement partagé entre CPU et IGP, même si l'on ne sait pas quelle sera le niveau de priorité respectifs qui leur seront donnés.

Si Intel reste peut loquace sur le sujet, c'est avant tout parce que ces versions se retrouveront exclusivement dans des puces au format BGA (directement soudées sur la carte mère), que ce soit dans le but d'être intégrées dans des PC portables (plutôt haut de gamme) ou alors dans des machines tout en un (type iMac).

On ne peut donc qu'être déçu de ne pas avoir plus de détails sur le sujet pour l'instant, on peut penser que cela ne durera pas forcément longtemps et qu'Intel devrait annoncer plus de détails, par exemple autour du lancement d'un de ses partenaires.

QuickSync

Au sein du GPU, on retrouve toujours QuickSync, la technologie de décodage et encodage vidéo d'Intel. Il s'agit de blocs d'unités fixes qui prennent en charge une grande partie des tâches de décodage et d'encodage vidéo et qui peuvent également envoyer des tâches de traitements vidéo sur les unités d'exécution (par exemple pour réduire le bruit ou désentrelacer les vidéos).

Du côté des décodeurs, Intel ajoute la gestion du format MJPEG surtout utilisé dans les appareils d'entrée de gamme. Côté encodage, deux nouveaux formats à noter, la première est l'arrivée du MPEG-2 (le standard utilisé sur les DVD) mais aussi celle du SVC, une version "scalable" du codec AVC/H.264. On retrouve avec SVC un container prévu pour le streaming de vidéo, et surtout au niveau du contenu, la possibilité de dégrader progressivement la qualité en fonction de la bande passante. L'autre nouveauté notable concerne la gestion du 4K à tous les niveaux, aussi bien niveau décodage, encodage qu'affichage.

Côté post processing, Intel étend les possibilités offertes avec l'ajout de nouveaux filtres, les plus notables sont la conversion de frame rate et la stabilisation d'images.

Qu'il s'agisse des filtres ou des codecs, Intel expose toutes les possibilités de QuickSync pour les développeurs au sein de son MediaSDK. Il est à noter qu'Intel dit proposer un peu plus d'options pour les développeurs dans le but d'améliorer la qualité, ce sur quoi nous reviendrons en pratique. Autre point, Intel dit travailler avec différents acteurs de l'open source, notamment les développeurs de HandBrake pour proposer un support de QuickSync dans leur logiciel. Une licence spécifique Open Source est proposée par le constructeur pour la version 2013 de son MediaSDK, un bon point.

Gestion des écrans

La gestion des écrans sur les plateformes précédentes d'Intel était relativement complexe puisque le signal vidéo était retransmis du processeur vers le chipset par un lien FDI, le chipset disposant d'une gestion interne. Tout ceci évolue dans Haswell, le processeur propose désormais quatre brins DDI qui pourront être utilisés pour configurer trois écrans au maximum. Il est possible de mutualiser les brins en effet pour atteindre des résolutions plus élevées (comme le support du 4k). Ces brins DDI sont uniquement utilisables pour des sorties numériques, à savoir DisplayPort, HDMI et DVI.

En parallèle, Intel utilise toujours un brin FDI qui est relié au chipset, ce brin étant utilisé pour une éventuelle sortie VGA (analogique) gérée directement par le chipset.

Côté nombre d'écrans, Haswell dispose de trois "Display Pipe" qui pourront être utilisés en simultanée pour piloter trois écrans physiques. Il est désormais possible en effet d'utiliser trois sorties en simultanée, y compris de mixer VGA et deux sorties numériques, ou trois sorties numériques. Sur ce dernier point, la datasheet d'Intel est quelque peu cryptique indiquant que toutes les permutations sont autorisées, sauf un mélange de HDMI et de DVI. Ce que nous en comprenons, c'est que pour utiliser trois sorties numériques, au minimum l'une d'entre elle doit être de type DisplayPort. Côté résolutions maximales, on peut atteindre 3840x2160 en 60Hz en DisplayPort, et 4096x2304 en 24 Hz (4k) et 2560x1600 à 60 Hz en HDMI/DVI. Notez enfin que le contrôleur HD Audio gère deux streams audio simultanés qui peuvent être assignés sur n'importe lequel des trois ports DDI.

Sommaire

1 - Introduction

2 - Les améliorations du jeu d'instruction x86 : TSX et AVX2

3 - Les améliorations de l'architecture CPU

4 - Les améliorations côté GPU

5 - LGA 1150, Régulateur de tension intégré

6 - Overclocking plus libre sur K, plus strict par ailleurs

7 - Chipsets Intel Serie 8, Lynx Point et Lynx Point-LP

8 - Les gammes Haswell

9 - Core i7-4770K, i5-4670K, i5-4430 et cartes mères

10 - Bug de l'USB 3.0 sur C1, compatibilité des alimentations

11 - Consommation, efficacité énergétique

12 - Températures, overclocking et undervolting

13 - HD Graphics 4600 : Consommation, Overclocking, Jeux

2 - Les améliorations du jeu d'instruction x86 : TSX et AVX2

3 - Les améliorations de l'architecture CPU

4 - Les améliorations côté GPU

5 - LGA 1150, Régulateur de tension intégré

6 - Overclocking plus libre sur K, plus strict par ailleurs

7 - Chipsets Intel Serie 8, Lynx Point et Lynx Point-LP

8 - Les gammes Haswell

9 - Core i7-4770K, i5-4670K, i5-4430 et cartes mères

10 - Bug de l'USB 3.0 sur C1, compatibilité des alimentations

11 - Consommation, efficacité énergétique

12 - Températures, overclocking et undervolting

13 - HD Graphics 4600 : Consommation, Overclocking, Jeux

14 - HD Graphics 4600 : OpenCL, Quicksync

15 - Protocole CPU, Rendu 3D : Mental Ray et V-Ray

16 - CPU Compilation : Visual Studio et MinGW/GCC

17 - CPU Compression : 7-zip et WinRAR

18 - CPU Encodage : x264 et Rovi H.264

19 - CPU Traitement photo : Lightroom et Bibble

20 - CPU IA d'échecs : Houdini et Fritz

21 - CPU Jeux 3D : Crysis 2 et Arma II : OA

22 - CPU Jeux 3D : Rise of Flight et F1 2012

23 - CPU Jeux 3D : Total War Shogun 2 et Skyrim

24 - CPU Jeux 3D : Starcraft II et Anno 2070

25 - Gains et Moyennes CPU

26 - Conclusion

15 - Protocole CPU, Rendu 3D : Mental Ray et V-Ray

16 - CPU Compilation : Visual Studio et MinGW/GCC

17 - CPU Compression : 7-zip et WinRAR

18 - CPU Encodage : x264 et Rovi H.264

19 - CPU Traitement photo : Lightroom et Bibble

20 - CPU IA d'échecs : Houdini et Fritz

21 - CPU Jeux 3D : Crysis 2 et Arma II : OA

22 - CPU Jeux 3D : Rise of Flight et F1 2012

23 - CPU Jeux 3D : Total War Shogun 2 et Skyrim

24 - CPU Jeux 3D : Starcraft II et Anno 2070

25 - Gains et Moyennes CPU

26 - Conclusion

Vos réactions

Contenus relatifs

- [+] 09/05: AMD Ryzen 7 2700, Ryzen 5 2600 et I...

- [+] 05/04: Pas de MAJ Microcode pour les Gulft...

- [+] 03/04: Intel lance la 2ème vague de sa 8èm...

- [+] 07/02: Windows 10, Meltdown et Spectre : q...

- [+] 05/10: Intel Core i7-8700K, Core i5-8600K,...

- [+] 12/09: Core i7-7820X : Un Skylake-X mieux ...

- [+] 07/09: Les Skylake en fin de vie chez Inte...

- [+] 23/08: Coffee Lake incompatible avec les L...

- [+] 29/06: Intel Core i9-7900X et Core i7-7740...

- [+] 03/01: Core i5-7600K et i7-7700K : pour qu...