Actualités informatiques du 15-03-2012

- Sondage: Allez-vous passer à Ivy Bridge ?

- Focus: 34 cartes mères Z77 Express

- Hynix concentré sur la NAND

- Common Platform Technology Forum 2012

- Marvell 88SS9187, du nouveau pour les SSD

| Mars 2012 | ||||||

|---|---|---|---|---|---|---|

| L | M | M | J | V | S | D |

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 | 31 | |

Sondage : Allez-vous passer à Ivy Bridge ?

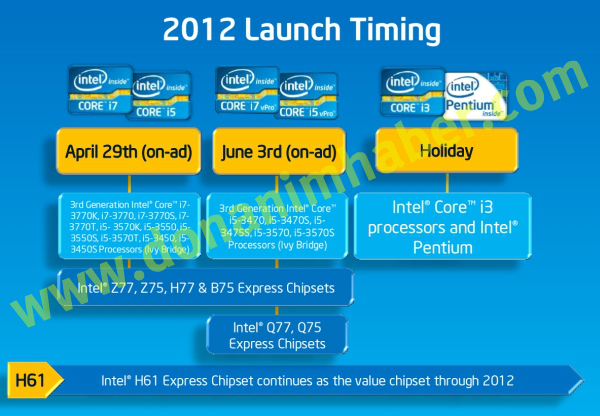

A un peu plus d'un mois de la sortie des futurs processeurs Ivy Bridge, voici un nouveau sondage concernant vos projets vis-à-vis de cette génération de processeur Intel en 22nm. Pour rappel, Ivy Bridge devrait apporter un gain d'environ 10% côté CPU et 50% côté iGPU par rapport aux actuels Core i5 et i7, le tout dans une enveloppe thermique plus réduite, avec un TDP qui passe de 95 à 77 watts sur les plus gros modèles.

Est-ce que vous comptez sur Ivy Bridge pour changer ou upgrader votre machine ? Conserverez-vous au contraire votre machine actuelle parce que l'évolution apportée par Ivy Bridge n'est pas suffisante ou ne vous est pas utile ? Dites-nous tout !

Focus : 34 cartes mères Z77 Express

Au fil des annonces, nous avons eu l’occasion de vous parler au cours des derniers jours des nouvelles cartes mères Z77 Express d’ASRock, ASUS, Gigabyte et MSI qui seront disponibles officiellement à partir du 9 avril prochain. Pour rappel, les chipsets Z77 Express et H77 Express succèdent respectivement au Z68 Express et H67 Express (le P67 express n'a pas de successeur a proprement parler).

Le principal changement par rapport aux puces actuelles est la gestion native de l'USB 3.0 - on est donc loin d'une révolution....

[+] Lire la suite

Hynix concentré sur la NAND

Au milieu des incertitudes dues à Elpida sur le marché de la mémoire DRAM, Hynix a indiqué vouloir cette année se concentrer principalement sur le marché de la mémoire flash NAND.

Nos confrères du Korea Herald rapportent les propos d'une conférence de presse tenue par le CEO d'Hynix qui aura indiqué qu'il envisage de convertir l'une de ses actuelles usines de production de DRAM (celle de Wuxi en Chine) vers la production de mémoire NAND pour augmenter la capacité de production de l'entreprise. Hynix dispose pour l'instant de 12% du marché de la NAND.

En attendant l'éventuelle transition de son usine chinoise, Hynix indique que la montée en production de sa Fab M12 (située à Ichon en Corée) augmentera sa capacité mensuelle de 130000 à 170000 wafers de NAND 300mm.

Côté mémoire Hynix indique travailler sur trois alternatives à la DRAM pour l'avenir, la Spin Transfer Torque RAM qui joue sur le fait que les électrons ont un léger mouvement cinétique lié à leur charge, mais aussi les mémoires à changement de phase (PRAM) que nous avons évoqués à plusieurs reprises ainsi que la ReRAM, évoquée entre autre par Elpida en début d'année.

Common Platform Technology Forum 2012

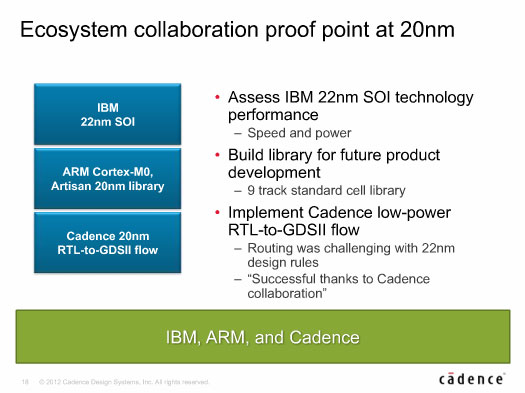

IBM, GlobalFoundries et Samsung tenaient aujourd'hui leur Technology Forum. Les trois sociétés travaillent pour rappel en commun sur le développement de leurs procédés de fabrications. Sans s'avancer réellement dans des annonces précises, les différentes sessions nous ont permis de noter quelques points intéressants.

D'abord, comme nous l'évoquions la semaine dernière, le 28nm développé par GlobalFoundries et ses autres partenaires fait l'impasse sur le SOI de type "partially-depleted" (PD-SOI), difficile à porter efficacement lorsque la finesse de gravure progresse, ce qui rend l'attrait de la technologie limitée. Si le PD-SOI est bel et bien mis au rebus (il a été confirmé qu'il ne refera pas son apparition sur le 20nm), cela ne signifie cependant pas l'arrêt total du SOI. Pour le 20nm et suivant, l'avenir selon le Dr Gary Patton d'IBM est au ETSOI. Il s'agit d'un type Fully Depleted, c'est-à-dire que le corps du transistor en lui-même qui aplani afin de contrer les effets du SOI classique. Si IBM aura mentionné plusieurs fois la présence de l'ETSOI, on notera que ce n'était pas le cas de ses partenaires qui ne se sont pas engagés précisément sur le sujet. L'allongement du délai de développement ainsi que le surcoût direct engendré sur les wafers peut en effet pousser les différents acteurs de la Common Platform à proposer, par exemple, un process avec ETSOI et un sans pour satisfaire la demande des clients. IBM aura confirmé au passage que l'ETSOI a été développé pour le 20nm en collaboration avec ST Micro.

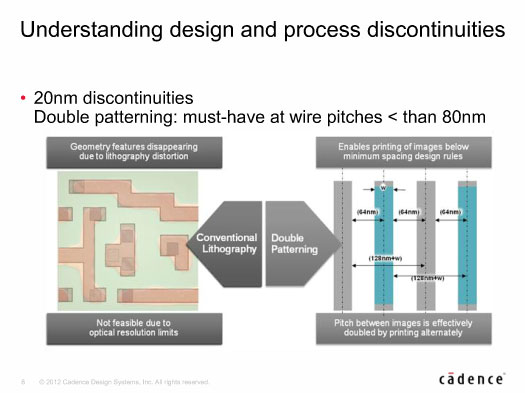

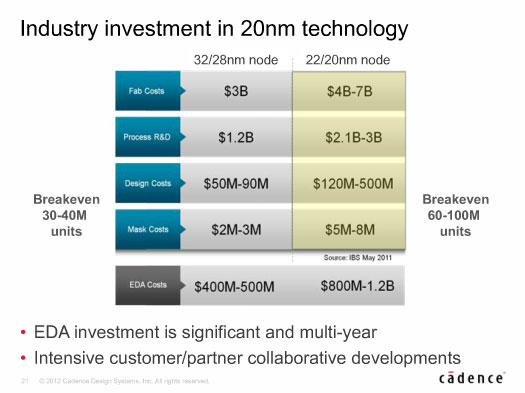

En ce qui concerne le 20nm, une annonce à tout de même été faite, celle de la nécessité du double patterning. La technologie consiste à utiliser deux expositions successives avec des masques différents pour réaliser une même couche métallique. Si toutes les couches ne sont pas concernées par la nécessité du double patterning, l'ajout des masques crée un surcoût notable. On aura noté d'ailleurs ce slide relativement édifiant sur les couts du 32/28 et du 22/20 nm :

Le surcoût sur les masques est particulièrement élevé tout comme le coût des outils de design (EDA) et du design en lui-même qui explosent en partie à cause de la complexification due au double patterning. Intel devrait lui aussi faire appel à de telles techniques pour le 16nm, cependant à notre connaissance ce n'est pas le cas pour le 22.

Autre annonce ferme, mais presque connue, l'arrivée des transistors FinFET. Pour rappel, Intel a décidé, dès le 22nm (qui arrivera sous peu avec les processeurs Ivy Bridge) de modifier la forme des transistors qui ne sont plus construits sur un plan, mais dans l'espace (voir notre focus sur le sujet pour plus de détails). Les membres de la Common Platform ont confirmé qu'il arriverait pour le 16nm, ce qui avait été sous entendu précédemment.

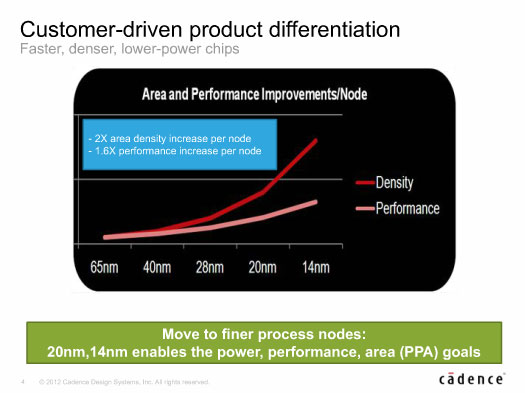

Le doublement de la densité à chaque node s'accompagne de gains de performances annoncés à 1.6x

En ce qui concerne l'au-delà du 10nm, considéré comme une barrière technologique pour les méthodes actuelles, IBM a évoqué plusieurs pistes comme l'utilisation de nanotubes de carbone. De ce côté, IBM a annoncé avoir développé de nouvelles méthodes pour trier plus facilement les nanotubes utilisables de ceux qui ne le sont pas. Gary Patton évoquait ainsi que 30% des nanotubes semi conducteurs produits étaient pleinement conducteurs et devaient donc être supprimés. En ce qui concerne la lithographie EUV, qui se fait attendre depuis plusieurs générations, il faudra encore attendre. Si IBM laissait entre ouverte une porte pour le 16nm, il est plus probable que la technologie ne soit pas à l'heure pour ce node.

Nous aurons noté enfin durant la conférence quelques petites phrases. D'abord, et à plusieurs reprises, des allusions sur le fait que les fabs 28nm de la Common Platform étaient fonctionnelles et non pas arrêtées. Un écho à un article relativement surprenant publié par nos confrères de SemiAccurate la semaine dernière qui indiquait que TSMC aurait stoppé complètement la production sur ses lignes 28nm il y a trois semaines de cela, pour un problème qui n'aurait pas été précisé. Une information difficile à vérifier et si nous avions entendu un temps des rumeurs sur d'éventuels retards de livraisons pour certains GPU produits par TSMC, elles se sont estompées depuis. La référence - multiple - à cette rumeur par les concurrents de TSMC était pour le moins originale.

On aura noté enfin, de la part de Subramani Kengeri de GlobalFoundries que si jusqu'ici la production de CPU et de GPU avait poussé en avant le développement des process de technologies, c'est aujourd'hui les SoC et les puces basse consommation qui forcent les décisions de design. AMD appréciera.

Marvell 88SS9187, du nouveau pour les SSD

Marvell annonce une nouvelle génération de contrôleur SSD, le 88SS9187. Cette puce prends la suite du 88SS9174 utilisé avec succès sur de nombreux SSD tels que les Corsair P3, Corsair Performance, Crucial C300, Crucial M4, Intel SSD 510, Plextor M2 ou encore Plextor M3.

Doté d'une interface Serial ATA 3.1 à 6 Gb/s, le 88SS9187 supporte la mémoire Flash sur 8 canaux. Chacun de ses canal peut utiliser un bus vers les puces Flash à 200 Mo /s et supporter jusqu'à 4 die de NAND par canal et 16 en utilisant des décodeurs externes, soit une capacité maximale de 1 To avec de puces de 8 Go.

En termes de performances globales Marvell se contente d'annoncer un débit en écriture de l'ordre de 500 Mo /s (la limite pratique de l'interface) même sur un SSD fragmenté et des accès aléatoires en écritures "best-in-class" (mais encore ?) avec un minimum d'over- provisioning et de dégradation des performances.

Le cache peut pour sa part atteindre les 1 Go et être de type DDR3, et Marvell met en avant un algorithme ECC avancé sans toutefois apporter plus de précision. Le Marvell 88SS9187 est également doté d'une technologie de RAID interne destinée à apporter une tolérance de panne au niveau des puces NAND, un peu comme le propose SandForce avec sa technologie RAISE . Ceci devrait surtout être utile pour de futurs SSD utilisant malheureusement des puces moins endurantes, on pense notamment à la TLC.

Cette technologie est annoncée comme flexible et activable (ou non) au niveau du firmware par les clients de Marvell et permettra de faire face à la perte de tout ou partie d'une puce NAND sans perte des données. La contrepartie devrait être double, à savoir une amputation partielle de l'espace qui sera disponible dès le départ (ex : 120 Go de disponible sur un SSD 128 Go) et une légère baisse des performances en écriture.

Marvell indique qu'un nombre significatif de fabricants de SSD haut de gamme devrait commencer à utiliser le Marvell 88SS9187 très prochainement, reste maintenant à attendre leurs annonces et surtout à voir ce que donneront ces nouveaux SSD en pratique !