Les derniers contenus liés au tag JEDEC

Afficher sous forme de : Titre | FluxLes NVDIMM ont un standard JEDEC

Le JEDEC ratifie la LPDDR4

CES: La GDDR5M victime des déboires d'Elpida

GDDR5M 4 Gbps en SO-DIMM pour Kaveri ?

Le JEDEC publie (enfin !) la spec. DDR4

Samsung évoque la GDDR6

HMC, DDR5 et 3D XPoint pour Micron

SK Hynix et Samsung parlent de HBM

Premières cartes UFS chez Samsung

Le JEDEC pose les bases de la HBM 2

Samsung évoque la GDDR6

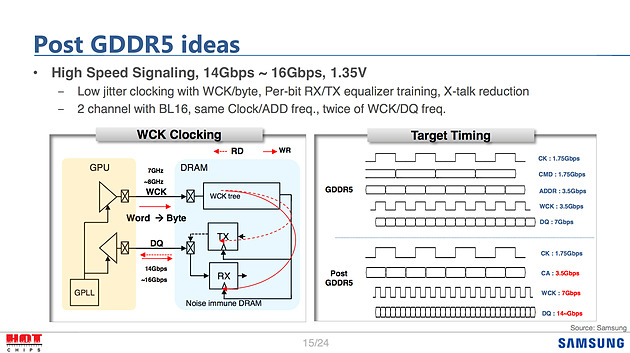

En parallèle à la mémoire HBM, Samsung à évoqué le futur de la GDDR5, ignorant quelque peu l'existence de la GDDR5X de Micron qui, bien que standardisée par le JEDEC, n'a pas été adoptée par ses concurrents.

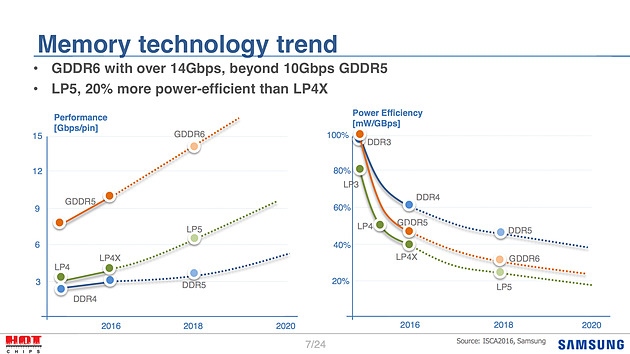

Pour la GDDR6, Samsung évoque certaines des pistes de travail envisagées. Côté objectifs la mémoire visera dans un premier temps 14 à 16 Gbps, ce qui était la cible haute pour rappel de la GDDR5X lors de sa présentation par Micron. Lors de la certification de la GDDR5X par le JEDEC, 14 Gbps est devenu le maximum visé. On notera que la GTX 1080 utilise pour rappel de la GDDR5X 10 Gbps. Techniquement, la GDDR5X abaissait la tension de la GDDR5 à 1.35V et doublait la bande passante en doublant le prefetch.

Samsung donne ici quelques idées sur la GDDR6, reprenant par exemple l'idée de la tension à 1.35V. L'élaboration de la spécification finale se fera au sein du consortium JEDEC dans les mois à venir.

Côté timing, Samsung évoque 2018, aligné avec la DDR5 et la LPDDR5, et un gain d'efficacité énergétique autour des 30%. On notera au passage que Samsung continue lui aussi de pousser son propre standard "X" avec la LPDDR4X, une variante de la mémoire mobile LPDDR4 qui fait "seulement" baisser la tension VDDQ à 0.6V pour obtenir un gain d'efficacité de 20%. Si le JEDEC n'a pas encore ratifié la LPDDR4X, on notera que SK Hynix avait annoncé en juin qu'il produirait lui aussi ce type de mémoire.

HMC, DDR5 et 3D XPoint pour Micron

Micron a également pris la parole pendant la première matinée de Hot Chips, comme nous le rapportent une fois de plus nos confrères de ComputerBase . Ces derniers qualifient d'une honnêteté rafraîchissante la présentation de Micron, ne cherchant pas forcément à annoncer des chiffres extravagants. La société aurait même regretté, si l'on en croit nos confrères, que son partenaire Intel ait annoncé beaucoup trop tôt la mémoire 3D XPoint !

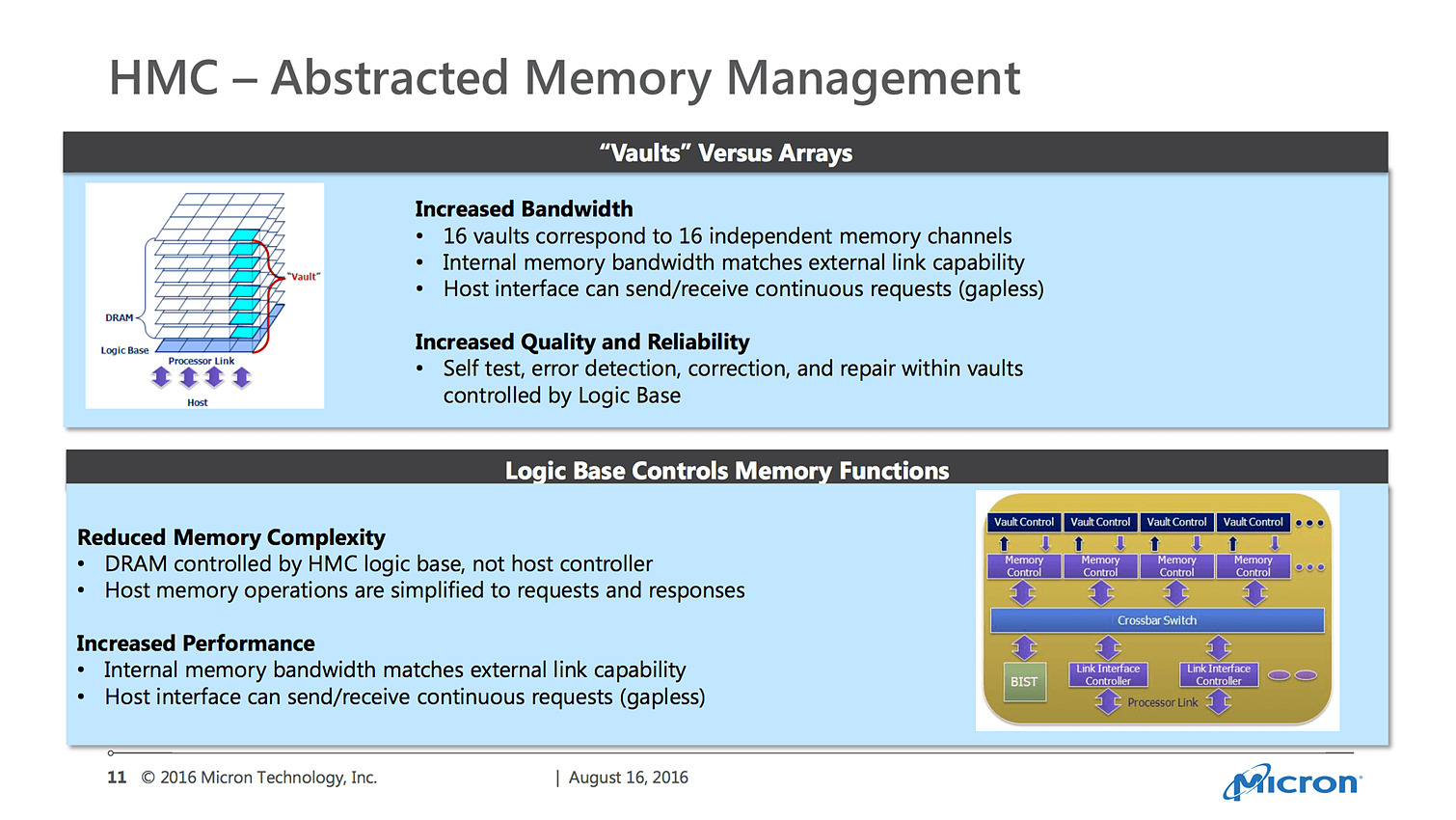

Dans le détail, Micron n'aura pas pu s'empêcher tout de même de qualifier la HBM de "mauvaise copie" de sa propre technologie Hybrid Memory Cube, plus complexe, coûteuse, et surtout assez peu disponible (elle devrait être présente sur le prochain Xeon Phi d'Intel, Knights Landing). Micron estime que la HMC dispose de nombreux avantages pour le marché du HPC, avec par exemple un meilleur algorithme de CRC que celui utilisé par le JEDEC pour la HBM.

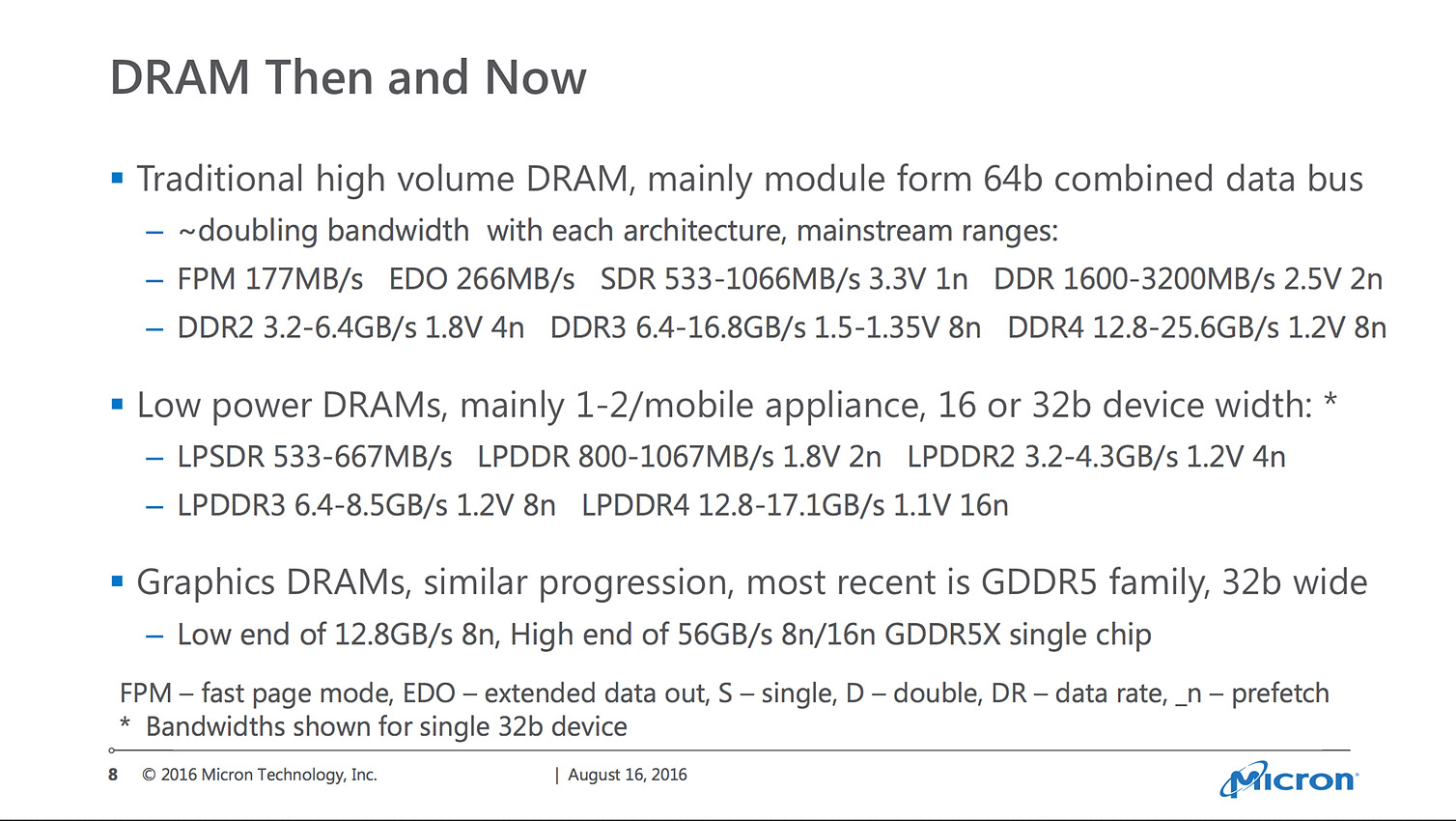

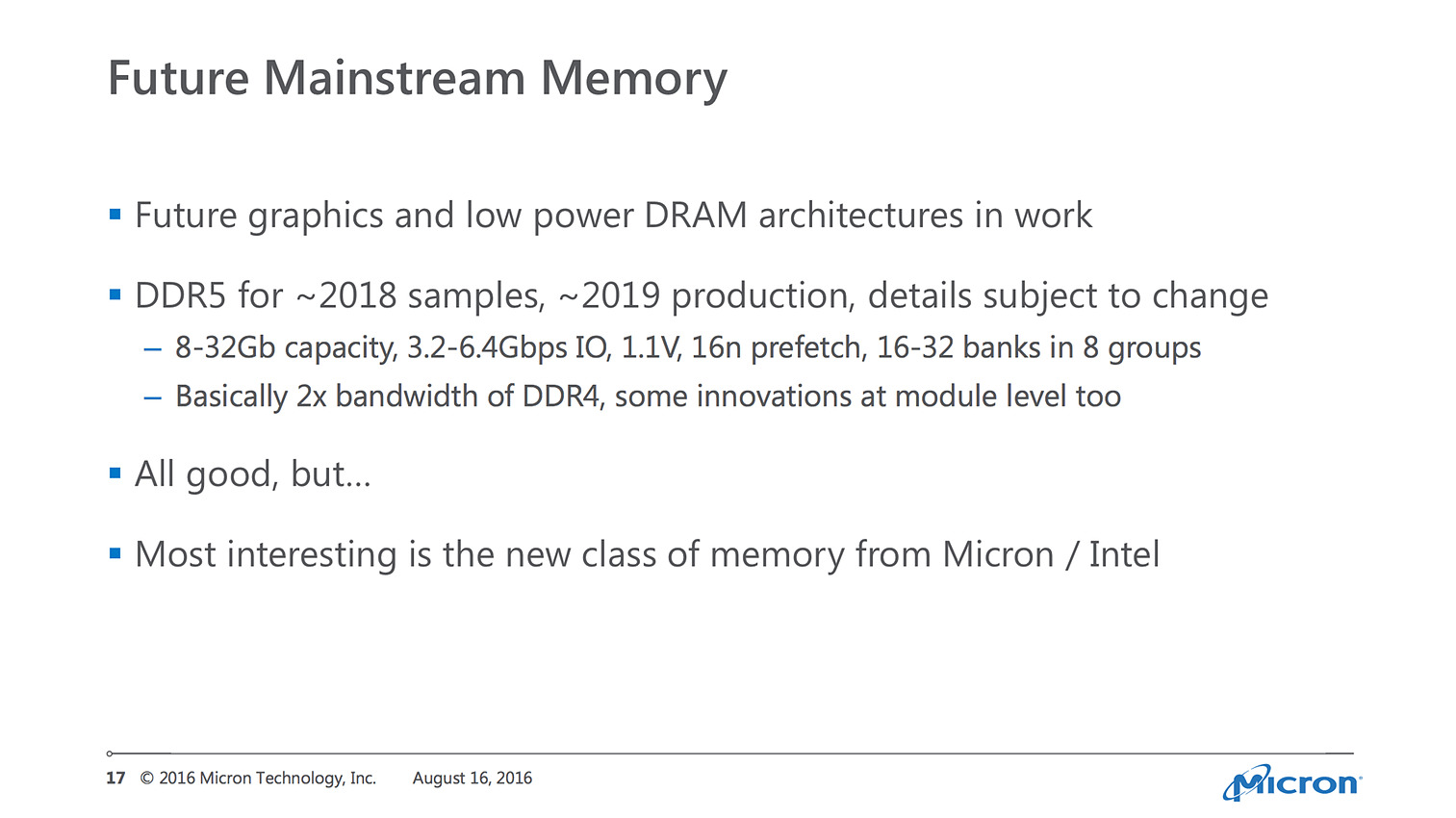

Micron aura également évoqué la DDR5 qui aura pour objectif de doubler la bande passante par rapport à la DDR4. Micron estime produire ses premiers échantillons courant 2018, avec une production en volume possiblement en 2019, mais plus probablement pour 2020.

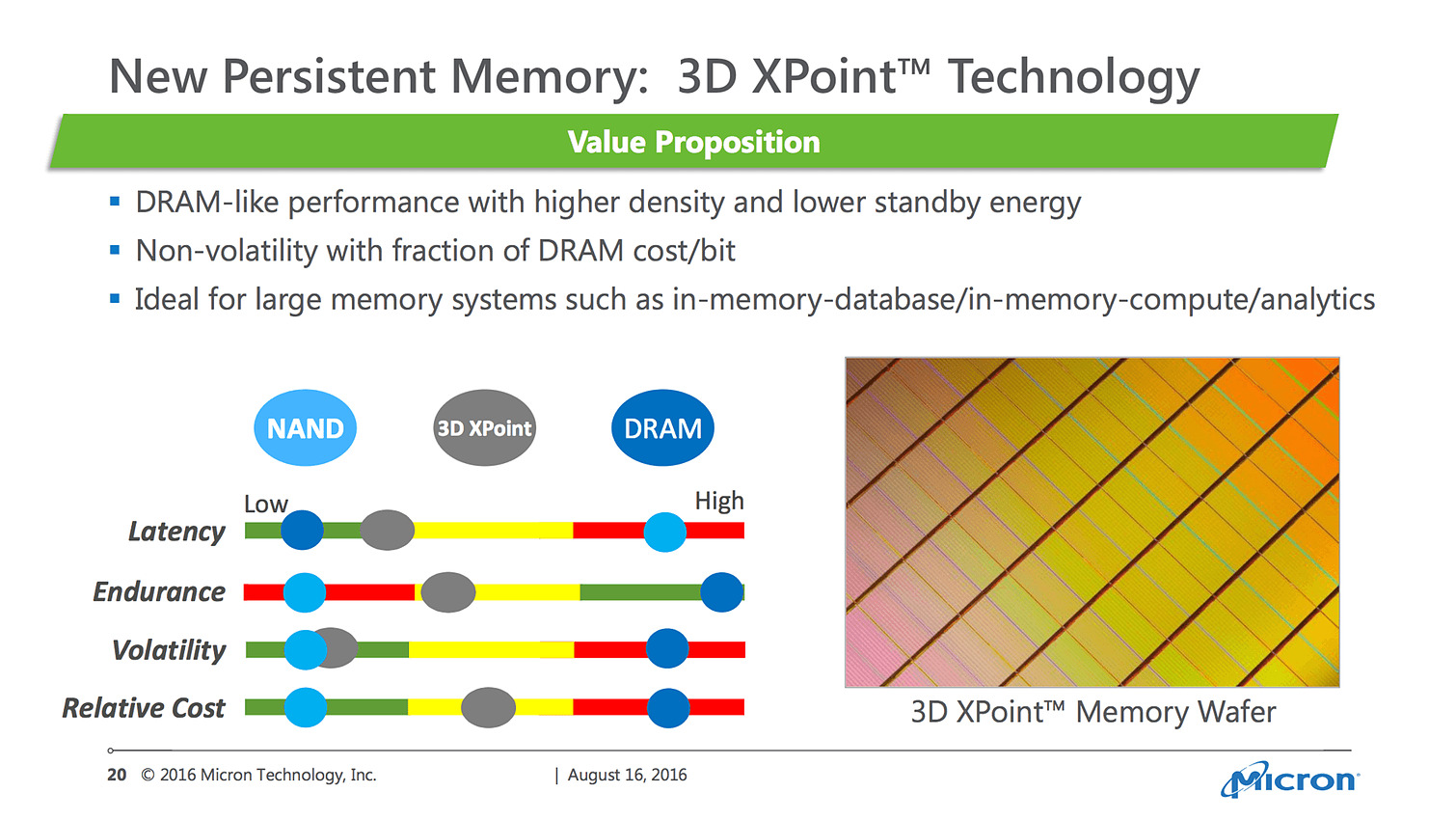

Outre le tacle envers son partenaire Intel sur la mémoire 3D XPoint, on ne retiendra pas beaucoup d'informations, si ce n'est que Micron confirme que ce nouveau type de mémoire sera en production avant la fin de l'année.

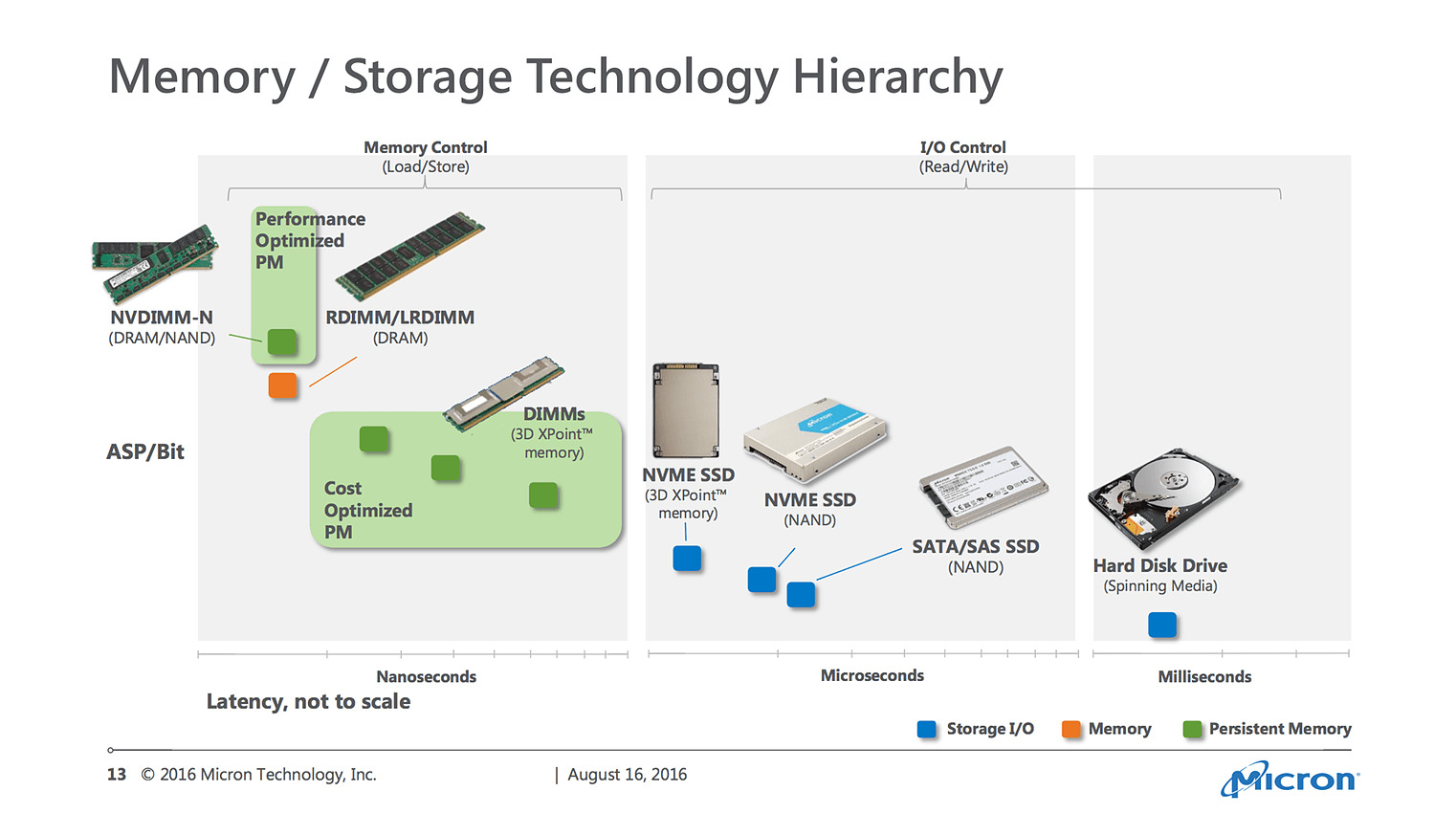

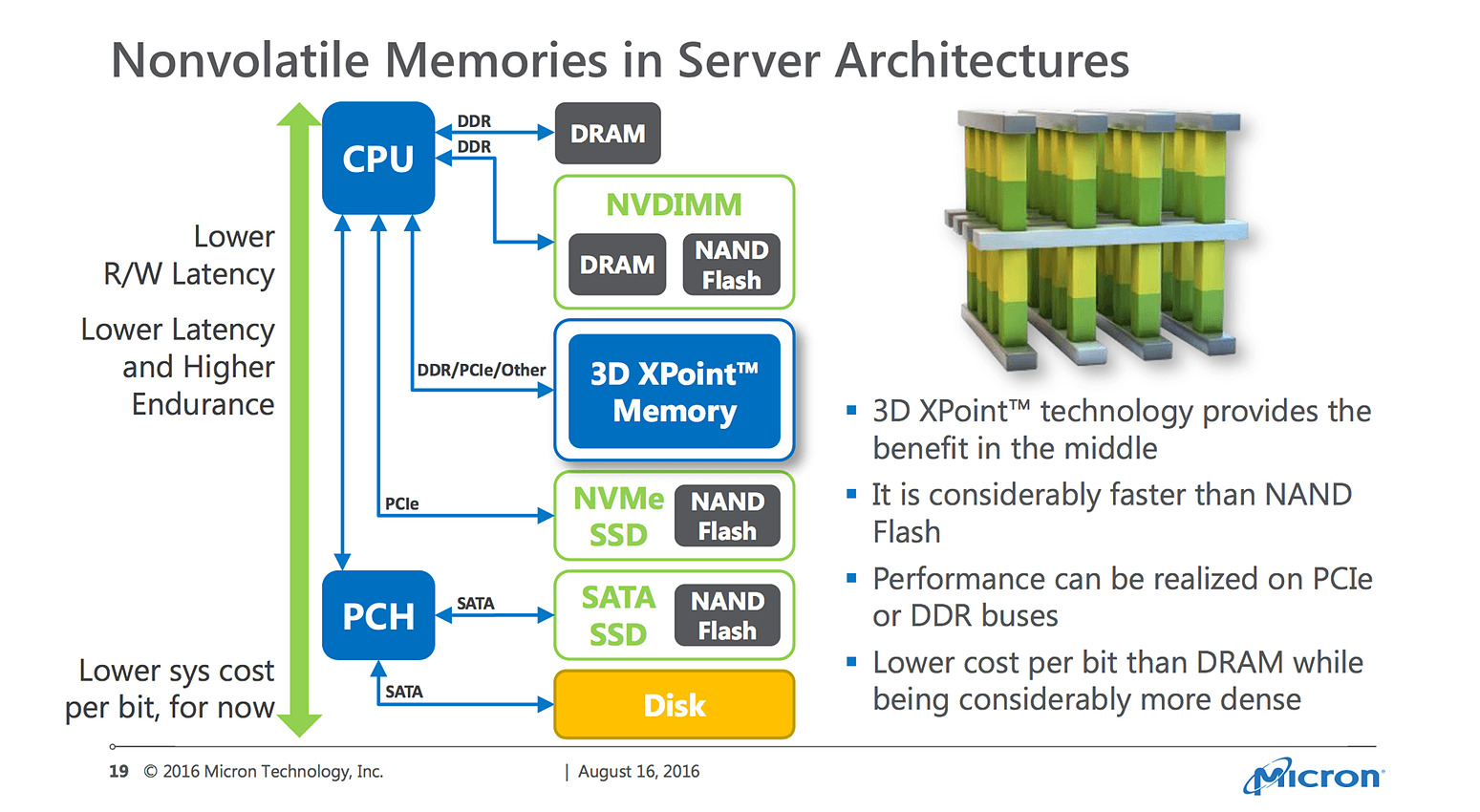

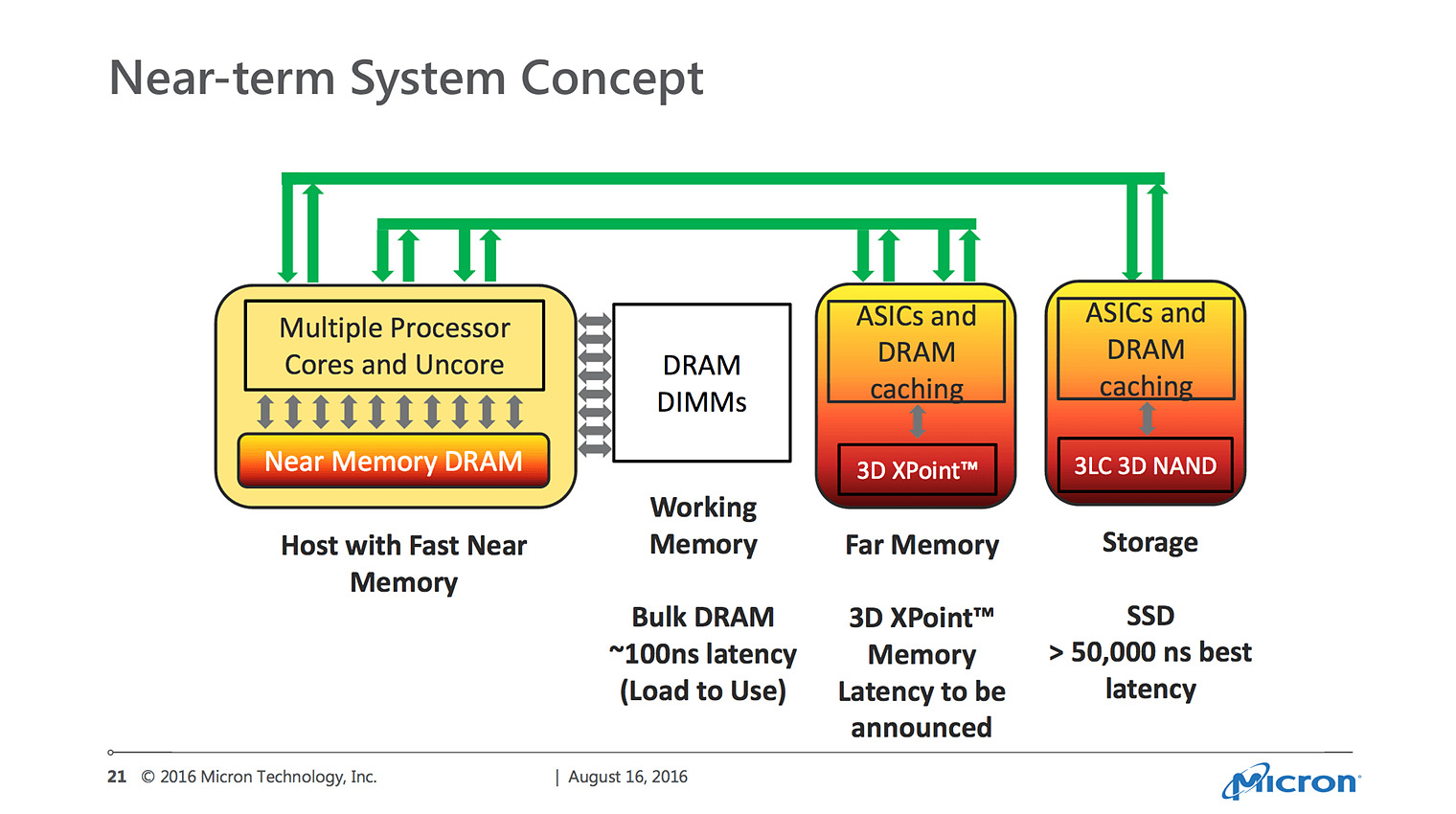

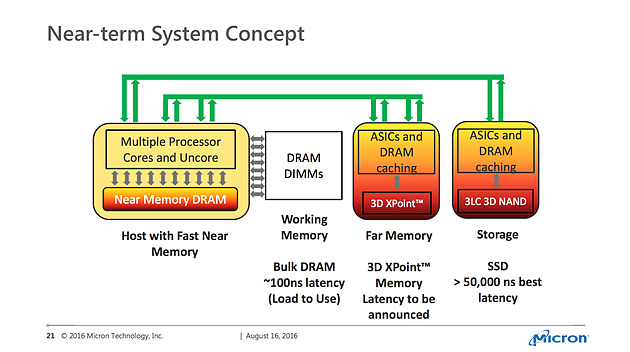

On retiendra ce dernier slide qui préfigure de ce que l'on devrait voir arriver sous peu sur les serveurs, avec deux tiers de mémoire DRAM. D'un côté une mémoire "proche", intégrée au processeur et rapide (HBM, ou plutôt HMC dans la vision de Micron) qui s'adjoint à la mémoire DRAM en barrettes plus classique. 3D XPoint et la 3D NAND proposant de leur côté deux tiers de stockages persistants.

Micron continue dans sa voie de l'originalité, dans un marché de la mémoire certes très concurrentiel. La société continue de mettre en avant sa GDDR5X, certes standardisée par le JEDEC mais qui n'a pas été adoptée par ses concurrents, mais aussi des solutions plus propriétaires comme l'Hybrid Memory Cube et 3D XPoint. Avec les ambitions de SK Hynix et de Samsung de pousser la HBM sur le terrain des PC clients, on peut cependant se demander si le pari d'ignorer la mémoire HBM ne se retournera pas contre Micron dans les mois à venir.

SK Hynix et Samsung parlent de HBM

Comme tous les ans, c'est à la fin de l'été que se tient la conférence Hot Chips (28ème édition) ou les divers acteurs du milieu présentent leurs nouveautés. Parmi les attractions de cette année, on attendra, dans la nuit de mardi à mercredi, "A New, High Performance x86 Core Design from AMD" qui devrait probablement nous en dire un peu plus sur Zen.

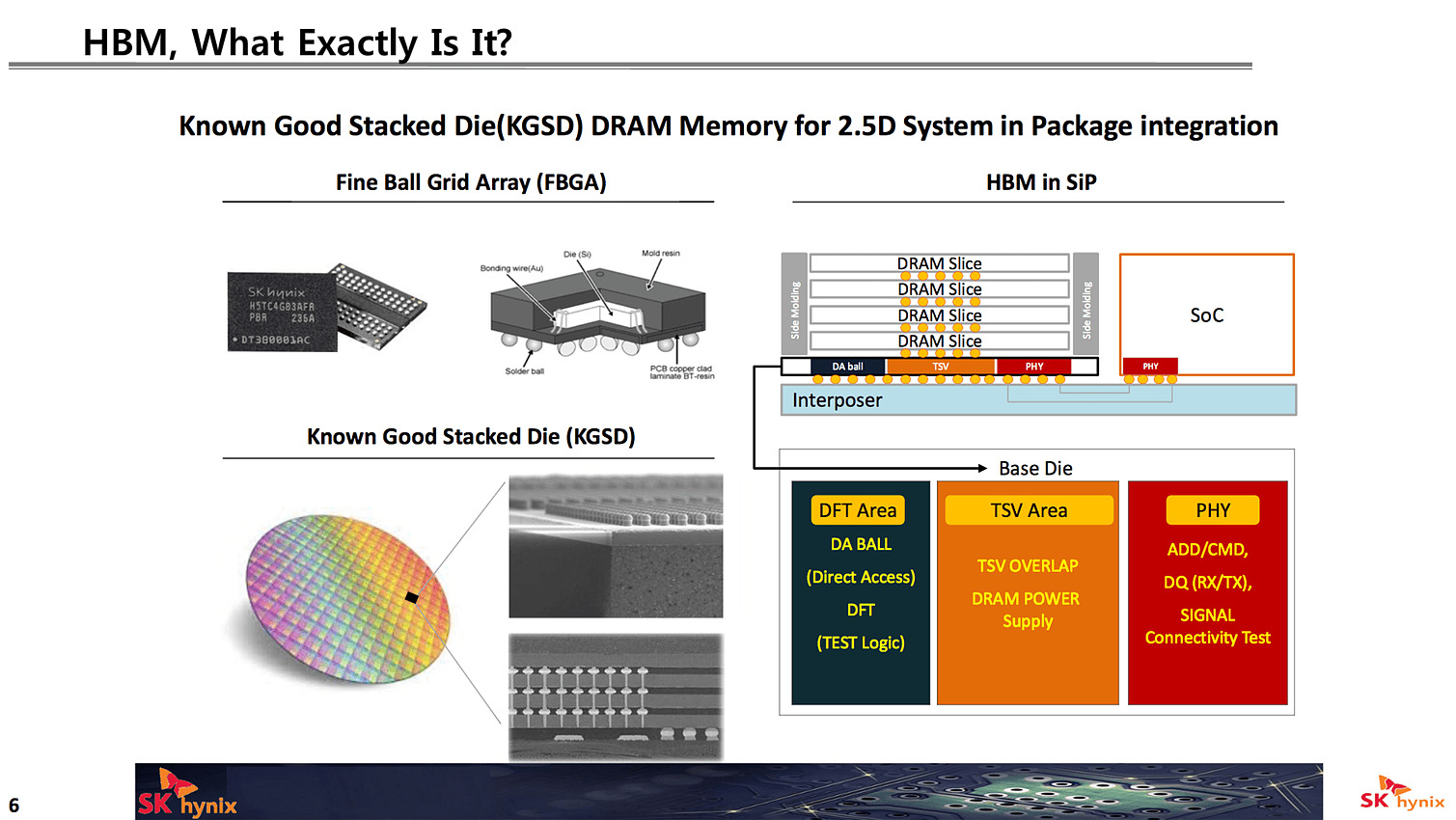

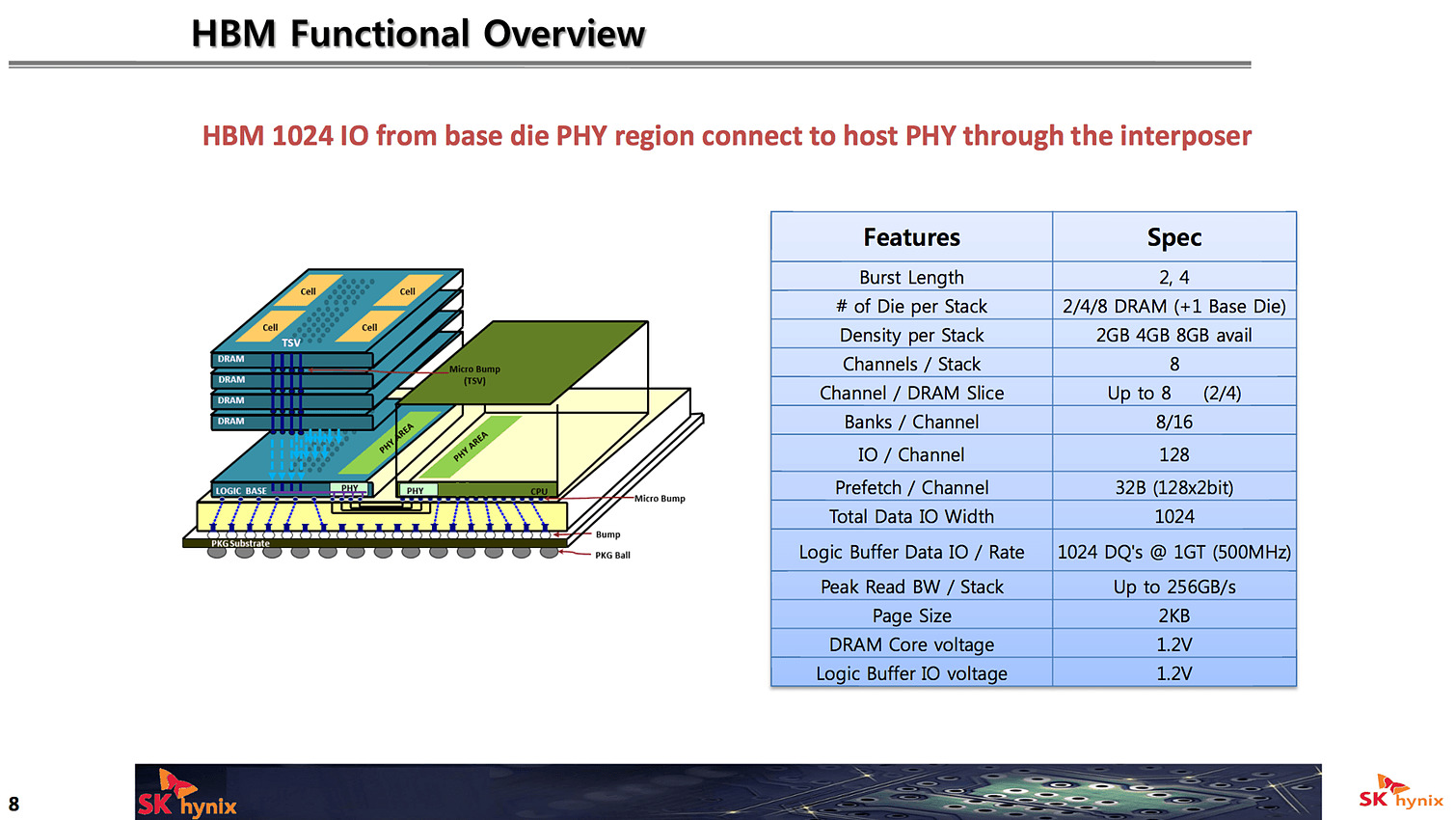

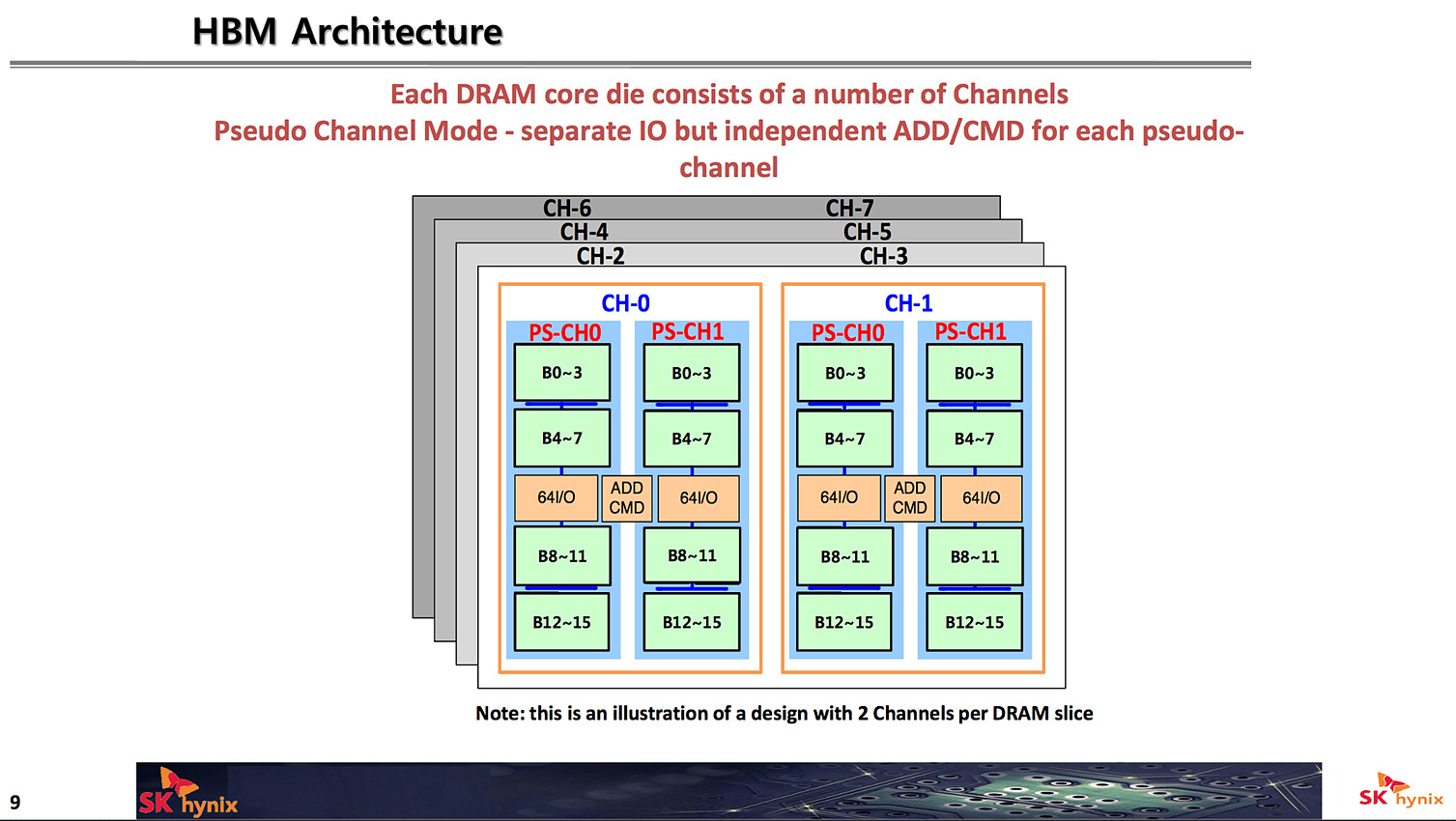

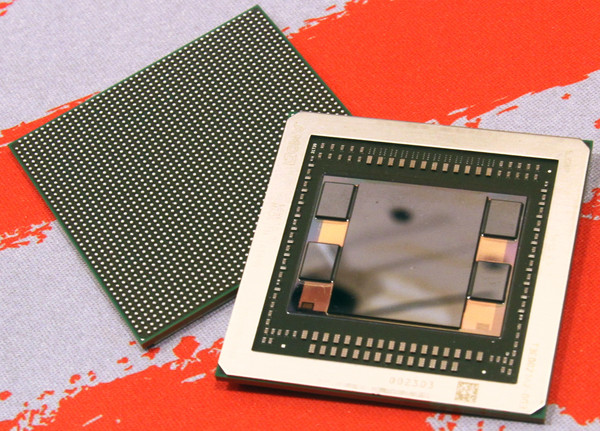

La première matinée de conférence avait lieu hier, dédiée à l'utilisation des nouvelles technologies mémoires. Chez SK Hynix et Samsung, la HBM était au programme. Pour rappel, la mémoire HBM est l'assemblage sur une même puce d'un die, en dessous, contenant les contrôleurs mémoires, et sur lequel on empile plusieurs dies de mémoire DRAM traditionnelle.

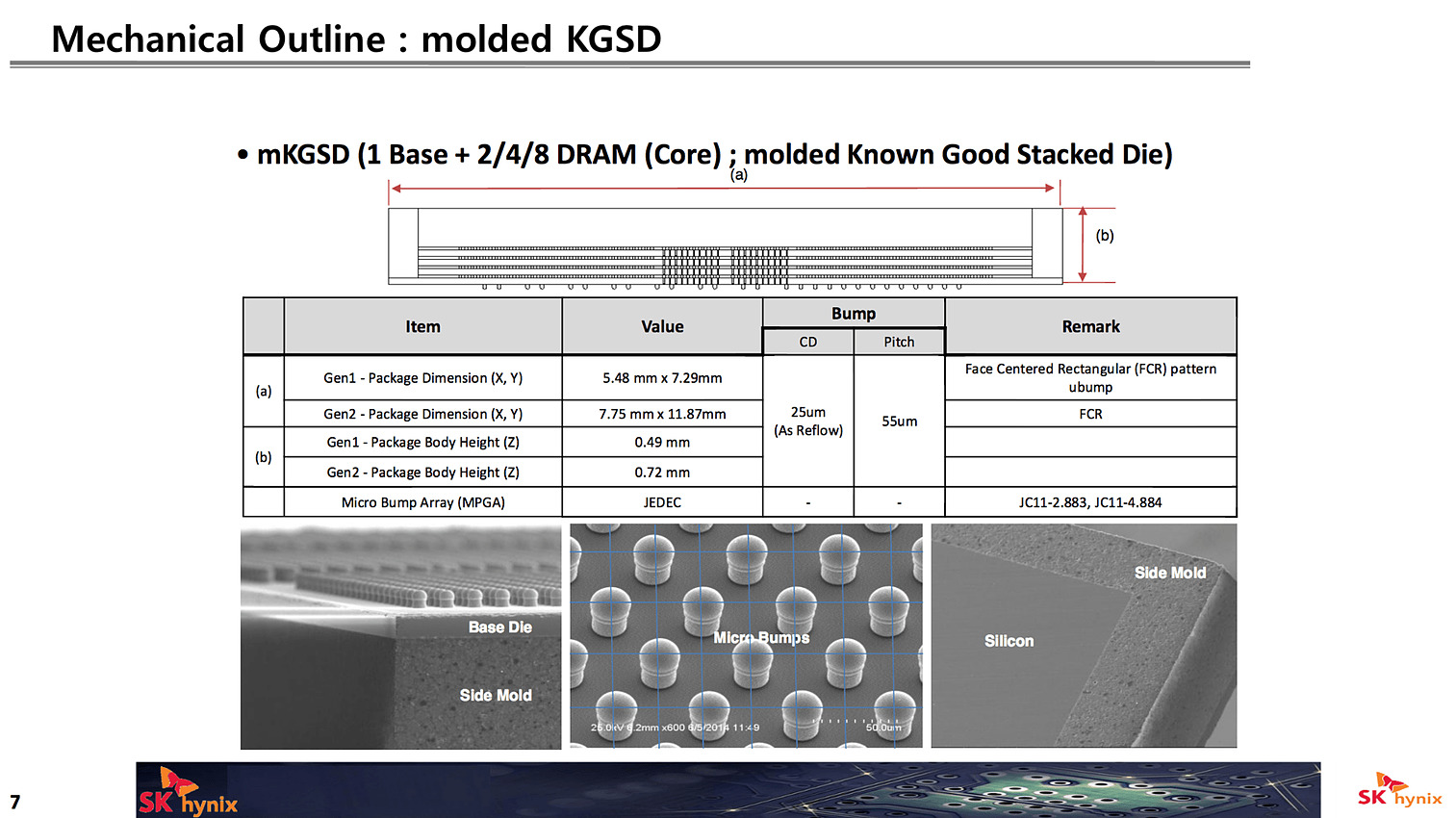

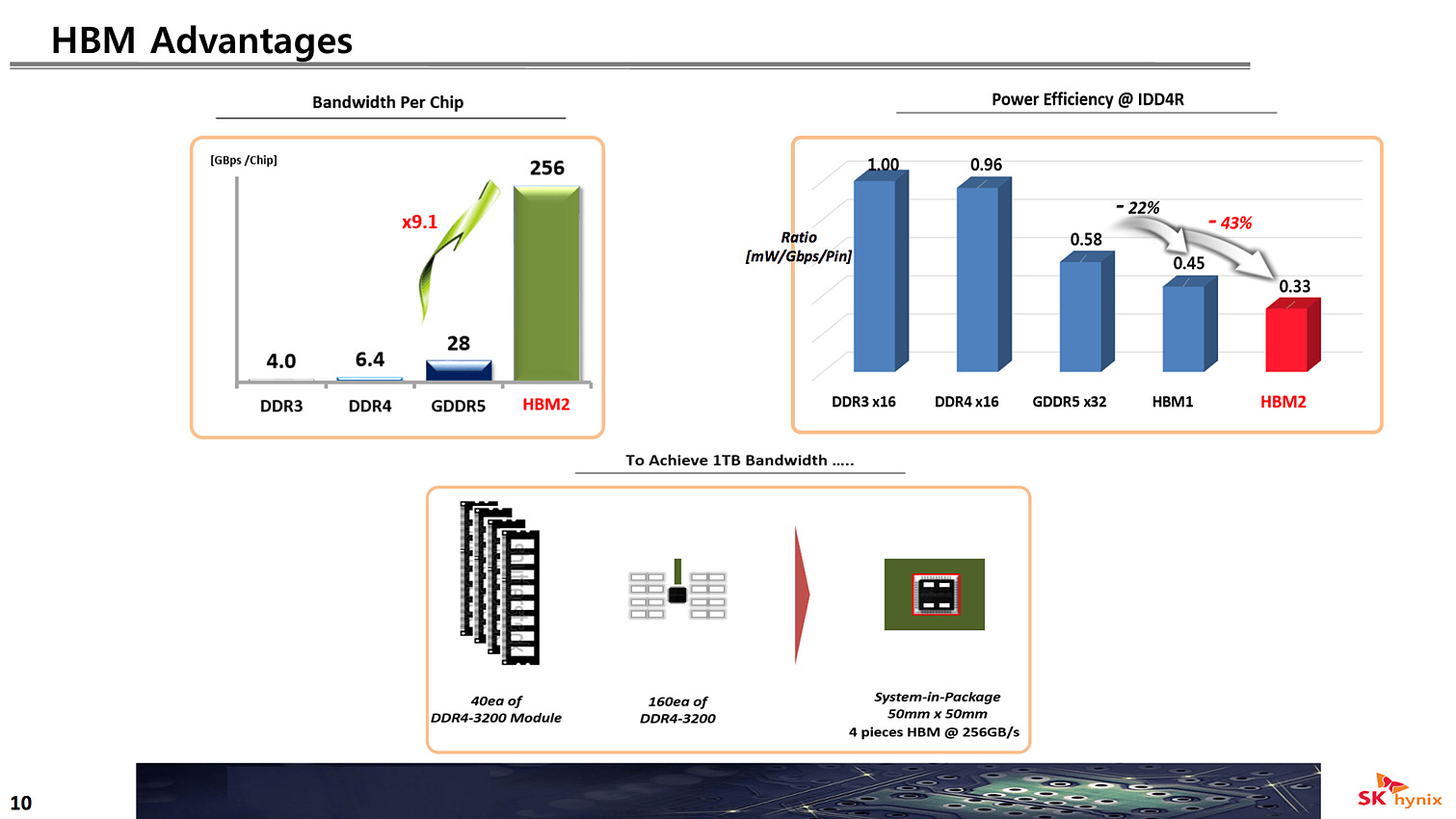

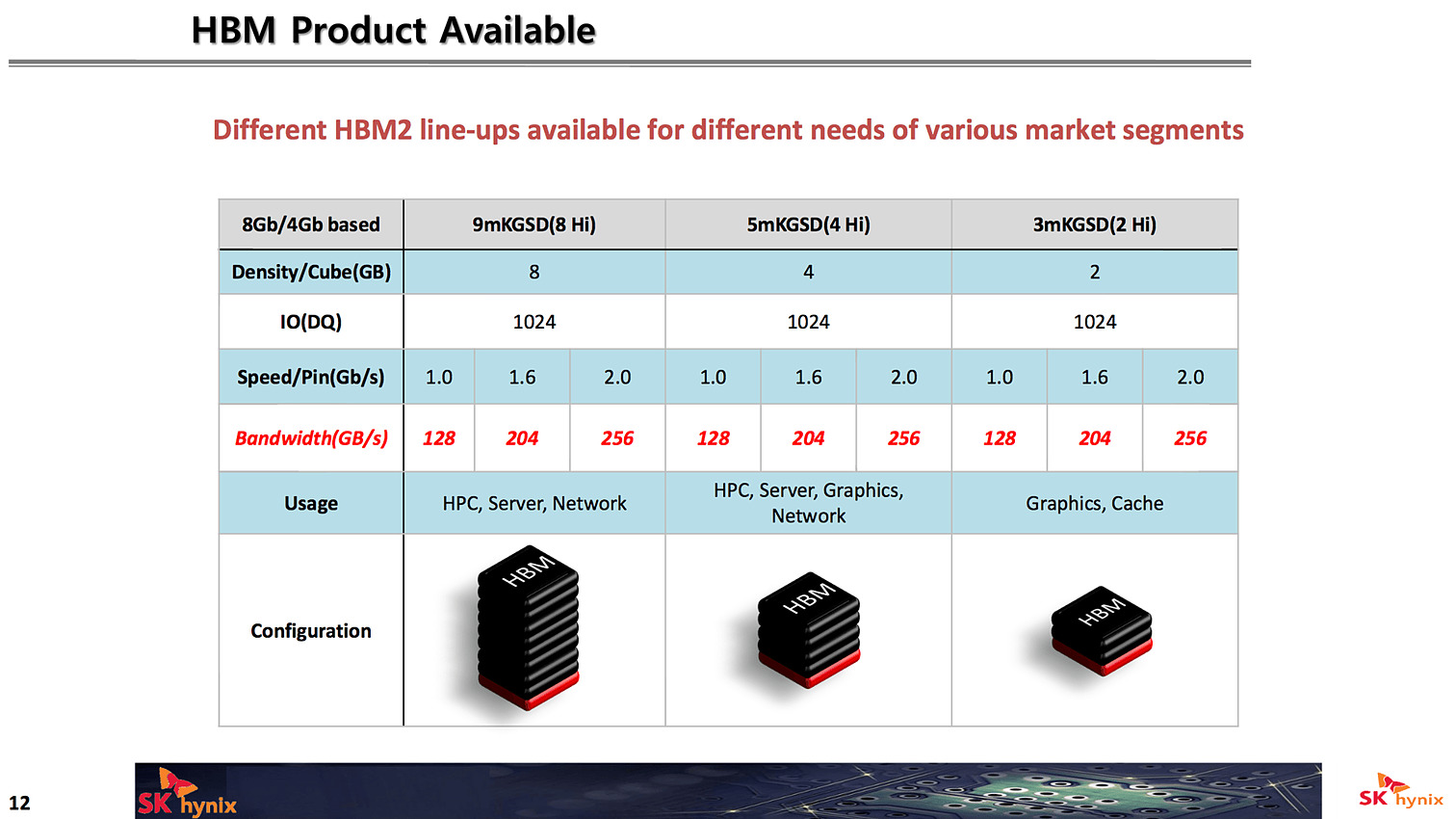

SK Hynix a confirmé ses ambitions sur la HBM2, qui pour rappel est standardisée par le JEDEC. Contrairement à la première version utilisée nottament par AMD sur les Fiji, la HBM2 utilise pour rappel des dies mémoire de 1 Go, empilés par deux, quatre ou huit. SK Hynix devrait lancer les premières puces, en version 4hi (quatre dies mémoire pour 4 Go au total) durant ce troisième trimestre.

Les versions 2Hi et 8Hi devraient suivre (soit 2 Go et 8 Go), et l'on notera qu'en plus des versions proposant 256 Go/s et 204 Go/s de bande passante, une version 128 Go/s sera également disponible au catalogue dans les différentes capacités.

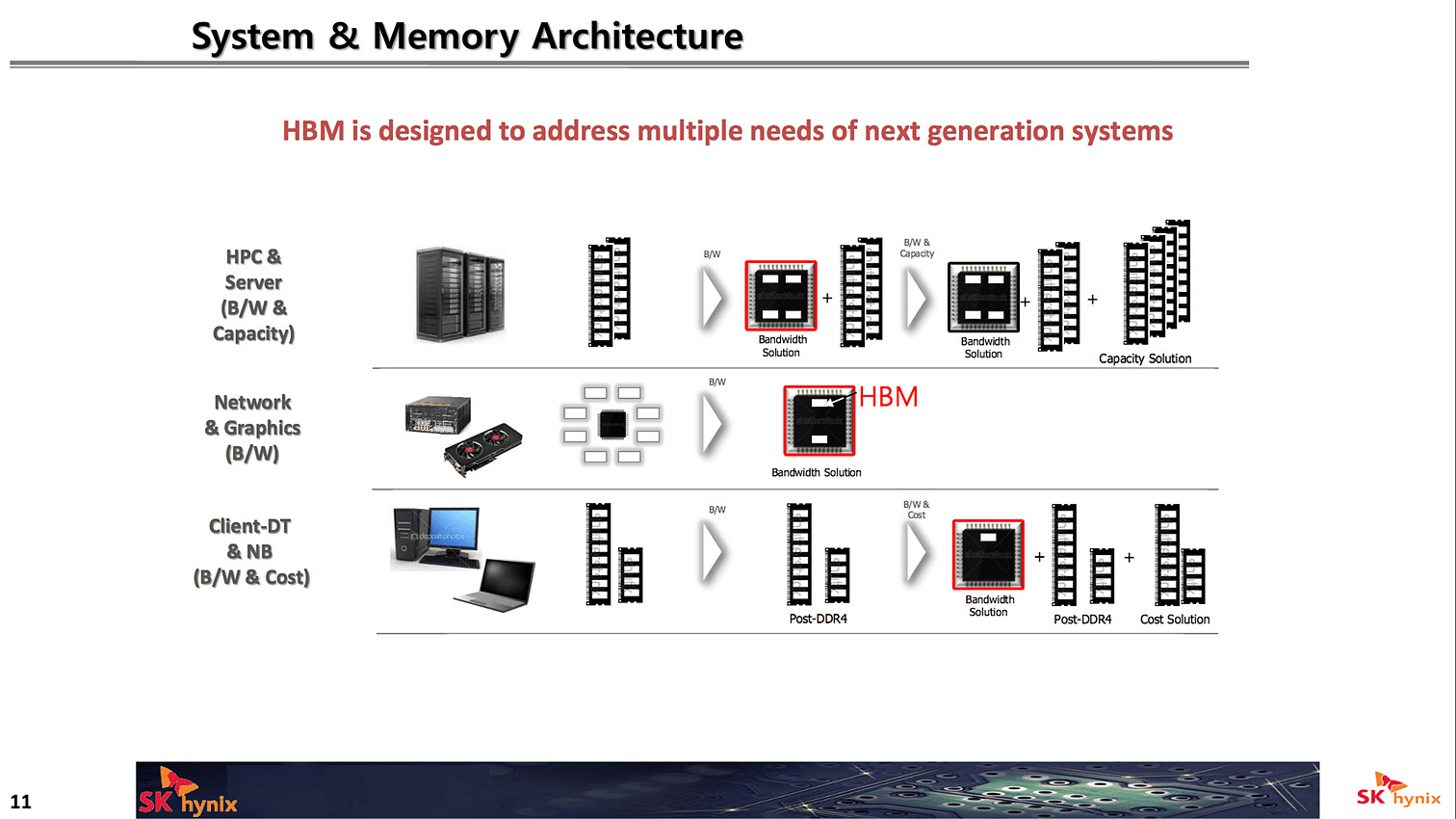

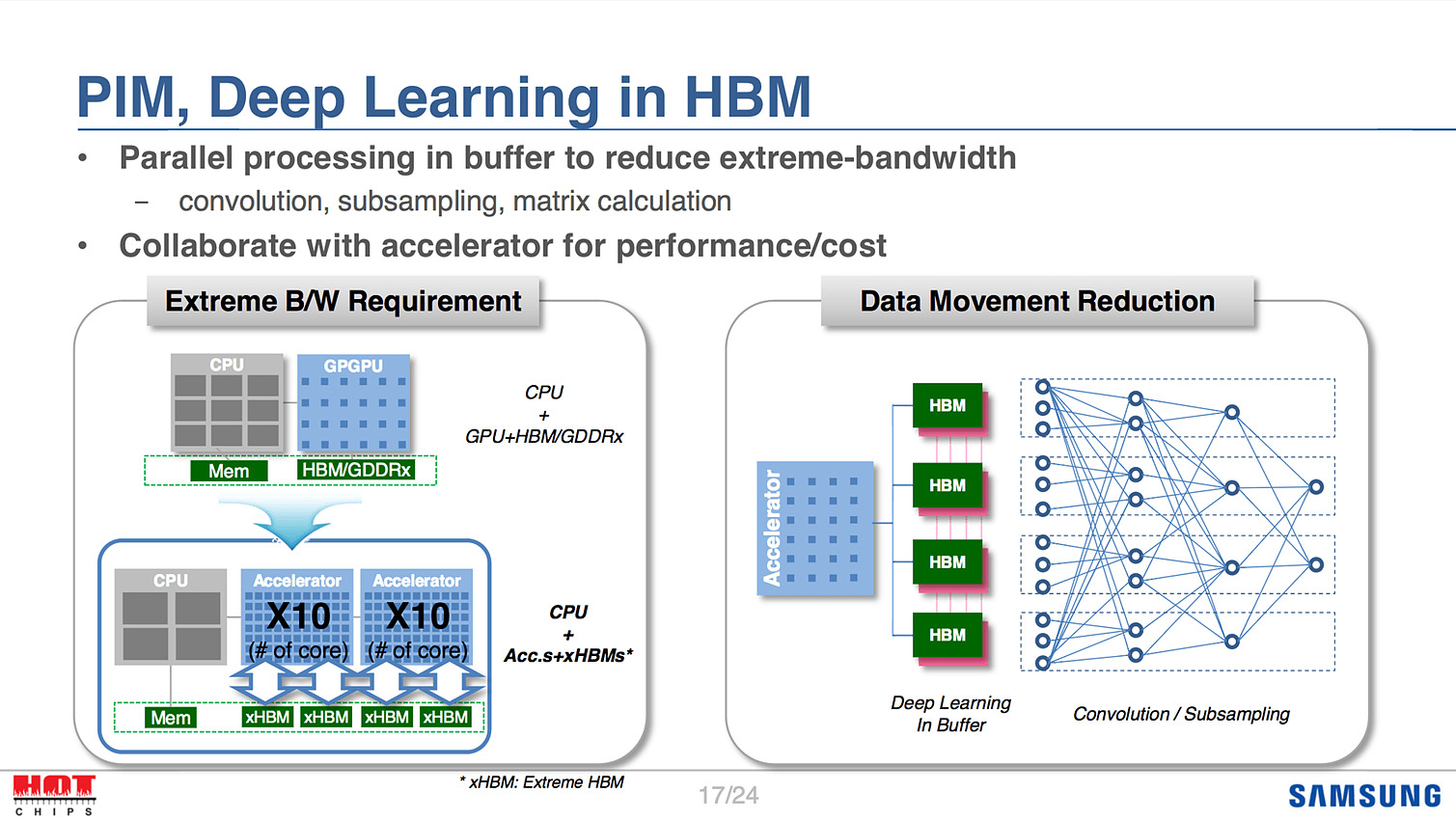

Côté utilisations, si les cartes graphiques ont été les premières à utiliser la HBM, SK Hynix envisage des utilisations dans le monde du HPC et des serveurs ou la HBM servirait de cache intermédiaire. Certaines déclinaisons de Zen pour serveurs devraient utiliser de la HBM, par exemple. SK Hynix voit également la HBM arriver en volume plus large dans les PC portables et desktop.

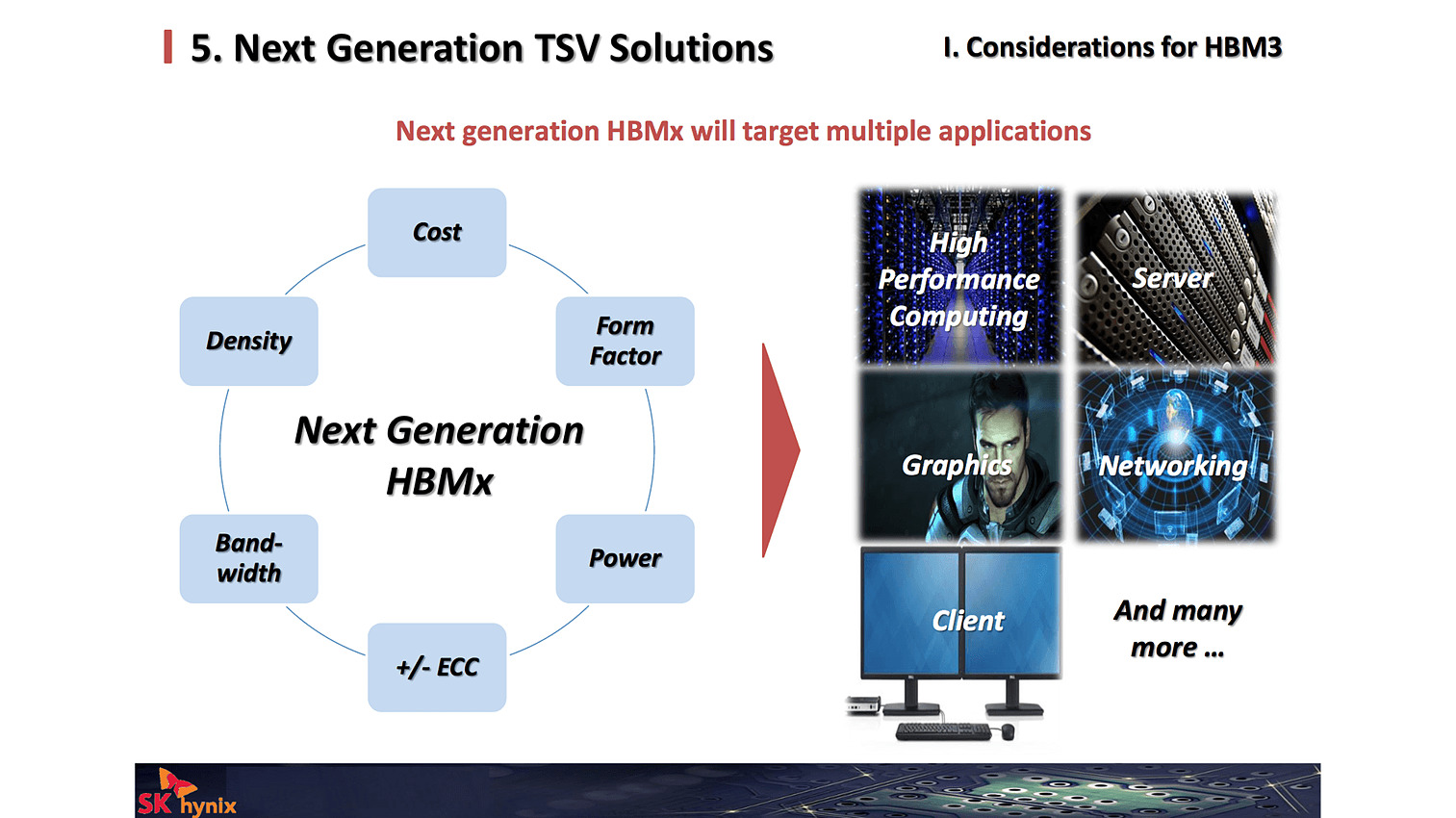

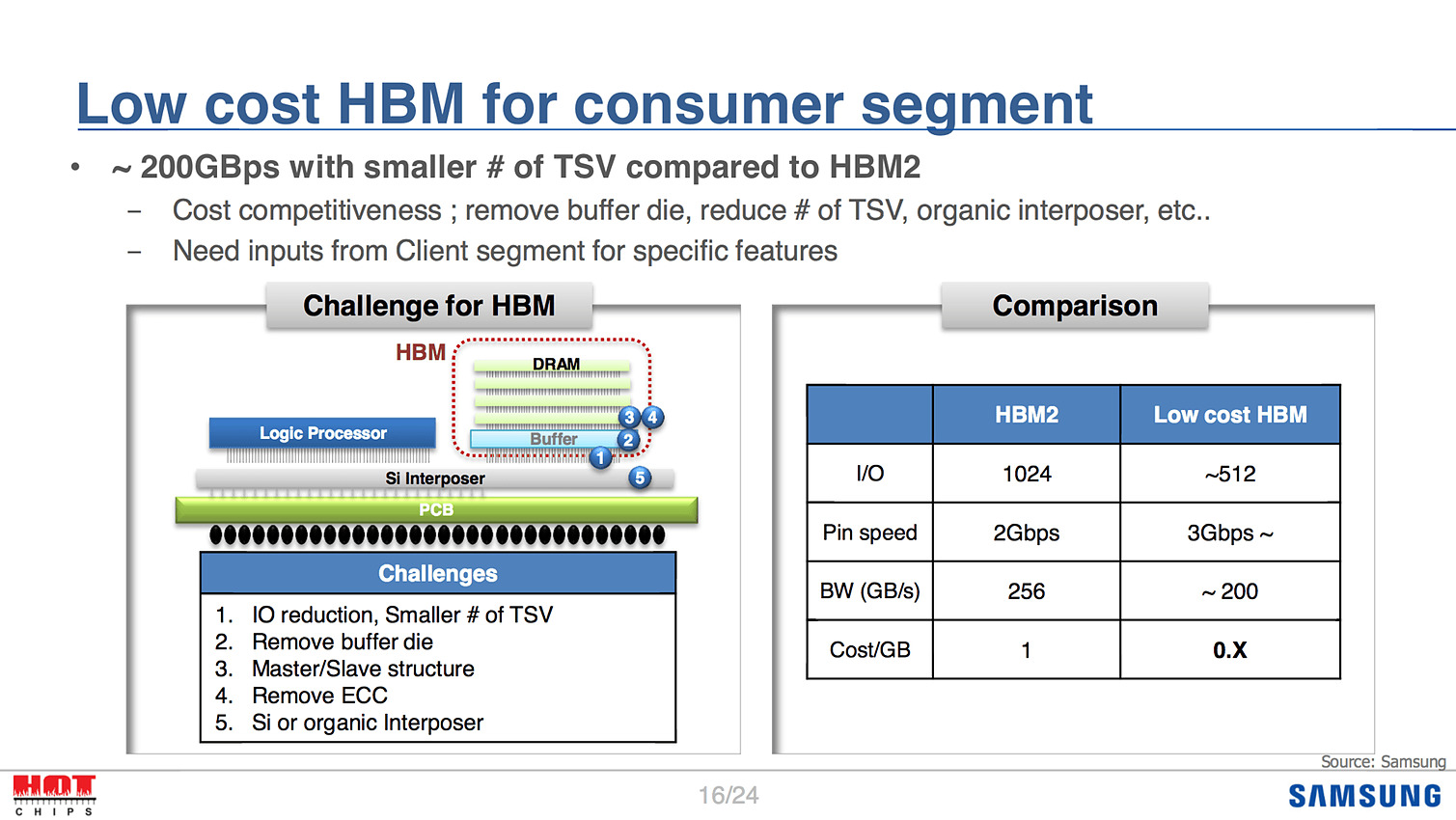

Côté Samsung, qui doit lancer aussi la HBM2 cette année, on parle surtout d'une version low cost de la HBM, qui ne serait pas de la HBM2 mais une variante plus abordable, en 512 bits (au lieu de 1024) et qui réduirait le nombre de TSV (Through Silicon Vias, les fils qui traversent les dies pour les relier les uns les autres). Le tout offrant tout de même 200 Go/s de bande passante. Un développement qui devrait s'effectuer en parallèle de celui de la HBM3 qui a pour objectif de doubler, sur le haut de gamme, la bande passante par rapport à la HBM2.

Premières cartes UFS chez Samsung

Samsung vient d'annoncer les premières cartes mémoires basées sur le standard UFS. Pour rappel, l'UFS (Universal Flash Standard) est un ensemble de standards développés par le JEDEC dans le but de proposer de la mémoire flash rapide pour les usages mobiles.

Le standard de base visait d'abord les puces mémoires à embarquer (par exemple dans les smartphones) afin de remplacer l'eMMC. Début 2015 on avait ainsi vu Samsung annoncer des puces de 128 Go en UFS 2.0. A l'époque seuls des chiffres d'IOPS étaient donnés, respectivement 19K et 14K en lecture et écriture aléatoire.

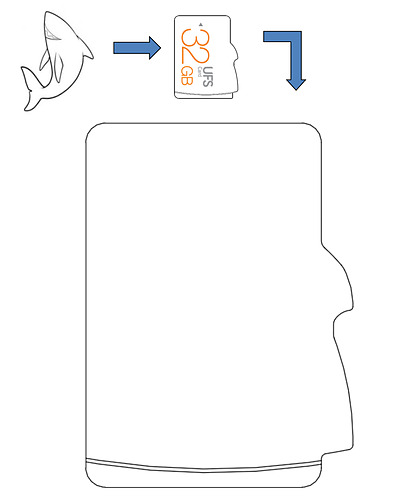

En mars dernier , en sus de la version 2.1 de l'UFS, le JEDEC avait publié une nouvelle spécification : l'UFS Card Extension Standard . Comme son nom l'indique, elle définit un nouveau standard de cartes mémoires visant à transposer l'UFS dans un format amovible. Ce dernier entre en concurrence avec les cartes SD (gérées par un consortium indépendant regroupant SanDisk, Panasonic et Toshiba) et apporte des débits largement supérieurs. On notera côté design que les cartes sont censées ressembler... à un requin :

Extrait de la spécification du JEDEC...

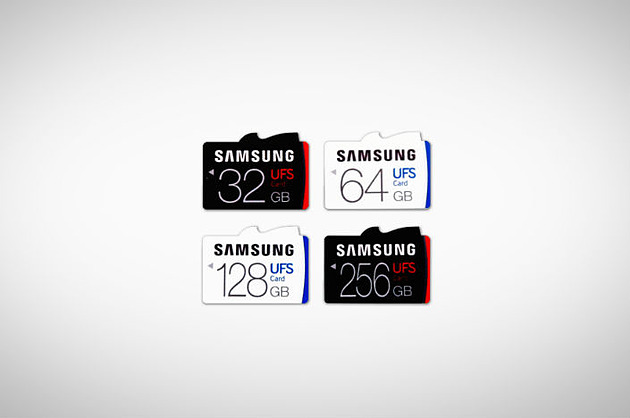

L'annonce de Samsung est donc surtout un premier pas avant de trouver éventuellement ce standard dans de futurs appareils. Quatre capacités sont annoncés, 32, 64, 128 et 256 Go. Côté performances Samsung en dit un peu plus annonçant 530 Mo/s en lecture séquentielle et 170 Mo/s en écriture séquentielle également. En aléatoire on atteint 40K IOPS en lecture et 35K IOPS en écriture, ce qui là aussi est particulièrement élevé pour des cartes mémoires.

Notez que si théoriquement l'UFS "embarqué" peut utiliser deux lignes, pour un débit maximal d'interface de 12 Gbit/s, l'UFS "carte" est limité à une seule (6 Gbit/s) en version 1.0. Le reste des protocoles, basés sur le SCSI restent identiques avec une gestion du NCQ et également la possibilité de définir une partition prioritaire pour les accès (par exemple pour s'assurer que l'enregistrement de vidéo soit toujours prioritaire sur des tâches systèmes annexes).

Samsung indique également que ses cartes sont les premières à avoir passé les tests de compatibilités de l'UFSA (Universal Flash Storage Association) qui avait été mis en place en avril dernier (l'UFSA s'assurant de l'interopérabilité des produits des différents acteurs du marché, à l'image de l'USB-IF pour l'USB).

Aucun prix n'est communiqué pour l'instant, ni vraiment de détails sur la disponibilité réelle, qui ne sert de toute façon à rien sans appareil pouvant les utiliser. Des annonces devraient suivre dans les prochains mois, possiblement pour des smartphones mais aussi des appareils photo/vidéo reflex.

Le JEDEC pose les bases de la HBM 2

Le JEDEC vient d'annoncer la publication d'une mise à jour de son standard concernant la HBM. Le document JESD235A, daté en fait de novembre 2015 remplace donc le JESD235 d'octobre 2013. Ce document pose les bases nécessaires à la HBM de seconde génération, avec des capacités par puce pouvant atteindre 8 Go via 8 dies empilés pour une bande passante de 256 Go /s via un bus 1024 bits. Pour rappel la HBM SK Hynix utilisée par AMD sur Fury est constituée de puces 1 Go à 128 Go /s.

Le standard intègre également un nouveau mode d'adressage qui permet de subdiviser les canaux 128 bits interne à la puce en sous-canaux de 64 bits ce qui permet de réduire la taille du prefetch et d'augmenter la bande passante effective. Ce mode de fonctionnement est optionnel pour les canaux de 1 à 4 Gb mais obligatoire en 8 Gb.

SK Hynix et Samsung sont sur les rails pour produire en volume de la HBM de seconde génération en 2016 afin d'offrir aux futurs GPU haut de gamme 14nm la bande passante qu'ils méritent.