Les contenus liés au tag JEDEC

Afficher sous forme de : Titre | FluxLes NVDIMM ont un standard JEDEC

L'organisme de normalisation JEDEC vient d'annoncer qu'il avait approuvé le premier standard concernant la NVDIMM (Non-Volatile DIMM). La spécificité de ces mémoires est d'intégrer de la mémoire non-volatile et non plus simplement de la DRAM.

Une barrette NVDIMM-N combine à la fois de la DRAM DDR4 et de la NAND Flash. En cas de coupure de courant inopinée, les données en DRAM sont sauvegardées en NAND, de gros condensateurs se chargeant de l'alimentation pendant l'opération. Plusieurs constructeurs tels que Viking Technology ou Micron, associé à AgigA Tech, produisent déjà ce genre de module en DDR3. Pour le moment la zone NAND n'est pas directement accessible par l'utilisateur mais il est possible que ce soit le cas sur une future NVDIMM-N2.

Pour la NVDIMM-F c'est un peu différent puisque la Flash est seule présente sur la barrette et permet d'obtenir un stockage de masse directement accessible via le bus mémoire, à l'instar de l'ULLtraDIMM de SanDisk co-développé avec Diablo Technologies. L'intérêt se trouve ici du côté de la densité mais aussi de la latence liée au bus mémoire.

Le JEDEC ratifie la LPDDR4

Le comité s'occupant de la standardisation des formats de mémoire (JEDEC) vient d'annoncer la publication de la spécification LPDDR4 (Low Power DDR4). Destinée aux plateformes mobiles, ce nouveau standard arrive seulement deux ans après la ratification de la LPDDR3. Outre l'utilisation dans les smartphones et les tablettes, Intel avait notamment commencé à proposer le support de la LPDDR3 dans ses plateformes Haswell-ULT (un support utilisé notamment par les Macbook Air).

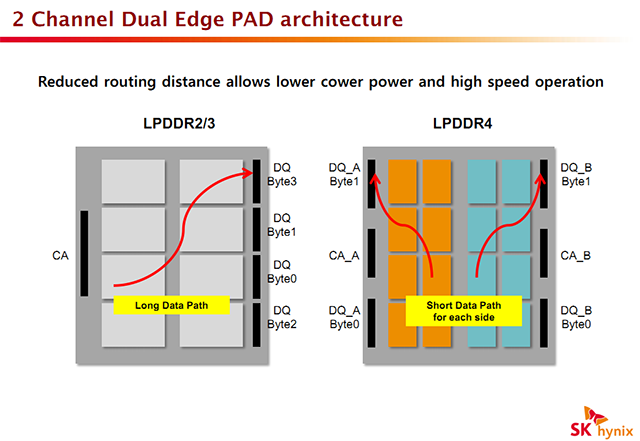

La LPDDR4 a pour objectif principal d'augmenter la bande passante disponible, annonçant entre 3200 et 4266 MT/s tout en réduisant encore plus la consommation. La tension principale passe ainsi de 1.2 à 1.1V, et diverses tensions additionnelles (terminaisons, signal, etc) ont également été revues à la baisse. Techniquement on retrouvera quelques changements communs avec la DDR4, même si les deux standards sont indépendant, comme le Data Bus Inversion qui permet d'inverser les bits à transmettre (1 en 0 et inversement) pour réduire la consommation (transmettre un 1, présence de signal, est plus couteux qu'un 0, absence de signal). On notera la présence de deux interfaces séparées pour créer deux canaux de données indépendants sur chaque puce pour réduire le routage nécessaire à l'intérieur de la puce.

La spécification est consultable directement sur le site du Jedec à cette adresse .

CES: La GDDR5M victime des déboires d'Elpida

Cet été, nous vous parlions de l'existence d'un type de mémoire qui était resté plus que discret et qui se présentait comme particulièrement bien adapté pour alimenter les APU : la GDDR5M. Il ne devrait finalement jamais voir le jour.

Pour rappel, la GDDR5M est un dérivé de la mémoire GDDR5, cette dernière étant avant tout destinée aux GPU (mais également exploitée sur la PS4). Si la base de la technologie est identique, la GDDR5M est optimisée pour autoriser un format "barrette mémoire" sans trop faire exploser les coûts, notamment à travers des puces de 4 Gbits interfacées en 16-bit, contre 32-bit pour la GDDR5 classique. De quoi permettre la mise en place de modules mémoire SO-DIMM de 2 Go et de 4 Go.

Durant la CES, nous avons eu l'opportunité de nous entretenir avec Joe Macri qui porte la double casquette de président du comité JEDEC en charge des mémoires DRAM et de Chief Technology Officer en charge des plateformes grand public chez AMD. Nous avons bien entendu voulu en profiter pour savoir ce qu'il était advenu de cette GDDR5M.

Les détails des futures APU A Series étant encore sous embargo, et l'abandon éventuel du support d'une technologie initialement prévue ayant peu de chances d'être discuté officiellement, nous n'avons bien entendu pas cherché à creuser le sujet en associant Kaveri à la GDDR5M. Nous estimons plus que probable qu'AMD avait prévu de l'utiliser pour Kaveri mais ceci reste de la spéculation de notre part.

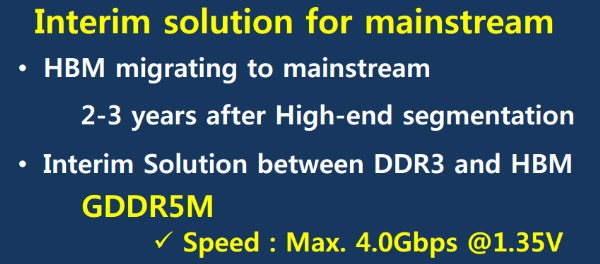

Ce qui n'est plus de la spéculation par contre c'est que la GDDR5M est bel et bien morte et enterrée. Joe Macri nous a ainsi expliqué qu'il s'agissait d'une "superbe mémoire" qui se présentait extrêmement bien au départ. Très prometteuse, elle allait permettre de gagner du temps par rapport à l'arrivée des mémoires Wide I/O2, HBM ou encore HMC, et 2 industriels avaient pris la décision de la développer et de la produire.

C'est le point central du destin de cette GDDR5M puisque dans l'industrie de la DRAM, il est nécessaire qu'au moins deux sources d'approvisionnement soient confirmées pour qu'une technologie puisse évoluer vers une existence commerciale. Sans quoi les risques sont bien trop élevés au niveau la disponibilité ou encore de la tarification. C'est ce qui a tué dans l'uf le développement de la GDDR5M.

Les deux industriels qui s'étaient penchés dessus étaient Hynix et Elpida. Or, il y a presque deux ans, Elpida a dû annoncer sa banqueroute et sa mise sous protection par les autorités de régulation financières japonaises. Celles-ci ont mis fin à tous les nouveaux projets dont la GDDR5M. Ne restait alors que Hynix, et malheureusement aucun autre fabricant de DRAM, par exemple Micron, n'a voulu prendre le relais et se lancer dans l'aventure.

Si nos spéculations sont correctes, vous imaginerez sans difficulté que cette faillite d'Elpida a ainsi pu avoir des répercussions importantes pour AMD et Kaveri.

GDDR5M 4 Gbps en SO-DIMM pour Kaveri ?

Malgré l'effervescence du net, certaines informations parviennent étrangement à passer relativement inaperçues. C'est le cas de la mémoire GDDR5M visiblement destinée à cohabiter avec la DDR4 tout en permettant de profiter d'une bande passante largement supérieure, et ainsi patienter en attendant l'arrivée des mémoires de type Wide I/O2, HBM ou encore HMC.

La GDDR5M, dont les spécifications principales ont été fixées par le JEDEC l'an passé, est une variante de la technologie GDDR5 adaptée au format "barrette mémoire" et plus précisément au SO-DIMM. Pour cela, deux modifications principales étaient nécessaires. Ainsi, par rapport à des modules soudés directement sur le PCB comme, c'est le cas sur les cartes graphiques ou sur la PS4, les contraintes sont plus importantes au niveau de l'intégrité des signaux électrique, ce qui impose de limiter la fréquence.

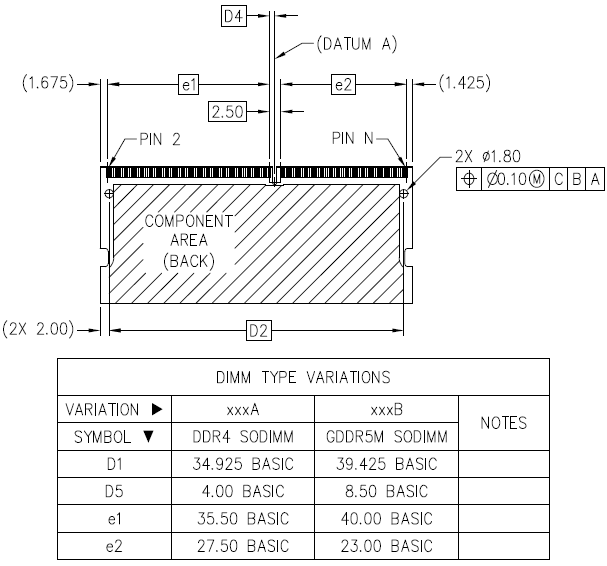

Ensuite, les modules GDDR5 sont interfacés en 32-bit avec une possibilité de les associer par paires (mode "clamshell") pour doubler la quantité de mémoire. Une interface relativement large qui limite l'espace mémoire maximal d'une barrette. Le format SO-DIMM, comme le DIMM classique, prévoit un canal de données large de 64-bit, qui peut donc accommoder au mieux 4 modules GDDR5 en mode clamshell, soit 2 Go par barrette si nous nous basons sur la densité maximale qui vient tout juste d'entrer en production (4 Gbits). Tout comme la GDDR5 la plus récente, la GDDR5M est prévue avec une densité de 4 Gbits mais cette fois interfacée en 16-bit ce qui permet au passage de réduire le nombre de pins de 170 à 96, comme c'est le cas pour la DDR3 destinée aux GPU. De quoi pouvoir monter à 4 Go par module SO-DIMM.

Hynix semble être le premier acteur, voire l'unique, sur ce type de mémoire. Le fabricant prévoit des modules cadencés à 1 GHz en 1.5V, à 900 MHz en 1.5V ou 1.35V et enfin à 800 MHz en 1.35V. De quoi représenter des débits par pin de 3.2 à 4.0 Gbps, ce qui peut sembler faible par rapport au débit de 7.0 Gbps de la GDDR5 la plus rapide (GeForce GTX 770). Il faut cependant placer la GDDR5M dans le contexte SO-DIMM et elle se montre alors sous un meilleur jour face au débit maximal de 1.6 Gbps pour la DDR3 et aux débits actuellement prévus de 1.6 à 2.4 Gbps pour la DDR4.

De quoi proposer un gain substantiel par rapport à cette dernière, d'autant plus que l'arrivée commerciale de la GDDR5M pourrait intervenir plus tôt. D'après ce document qui date du début de l'année, c'est en ce moment qu'Hynix commence à fournir les premiers échantillons de tests à ses clients, pour une production en volume qui devrait logiquement intervenir au premier semestre 2014.

Physiquement, un module SO-DIMM GDDR5M sera très proche d'un module SO-DIMM DDR4, tous deux partageant le même format 256 pins. Seule la position du détrompeur, un petit peu plus excentré pour la première, permettra de les différencier. Notez que tout semble indiquer qu'il ne sera pas possible de prévoir un connecteur compatible avec les deux types de mémoire.

Quelle utilité pour cette GDDR5M dont le support n'a à ce jour été annoncé officiellement par personne ? De toute évidence, Intel qui a l'habitude de dévoiler ses plans largement à l'avance, n'a pas prévu d'exploiter ce type de mémoire. C'est plutôt du côté d'AMD qu'il faut chercher, d'autant plus que le président du comité JEDEC en charge des mémoires DRAM n'est autre que Joe Macri, Chief Technology Officer en charge des plateformes grand public chez AMD. Par ailleurs, en produisant un APU ou SoC équipé d'un contrôleur mémoire GDDR5 pour la PS4 de Sony, AMD a déjà fait un pas vers l'utilisation de ce type de mémoire.

Prévu pour début 2014, l'APU Kaveri a tout du suspect parfait et pourrait ainsi supporter la GDDR5M de manière à offrir plus de bande passante à son GPU. Une manière en quelque sorte de répondre à l'eDRAM embarquée par Intel sur les CPU Haswell équipés de la variante GT3e du GPU intégré (Iris Pro 5200).

Le fait que seul un module SO-DIMM ait été prévu à l'heure actuelle laisse penser que cette mémoire est avant tout destinée aux portables, ce qui est logique. Ils sont en effet les plus à mêmes de trouver de la valeur dans un GPU intégré aux performances en hausse à travers l'utilisation d'une mémoire qui sera bien entendu plus chère. Ceci dit, si Kaveri s'avérait bel et bien compatible avec cette mémoire GDDR5M, rien n'empêcherait le design d'une carte-mère desktop équipée de slots SO-DIMM 256 pins.

Le JEDEC publie (enfin !) la spec. DDR4

Attendue dans un premier temps fin 2011, puis pour la mi 2012, c'est finalement mardi dernier que le JEDEC - le consortium des différents acteurs de l'industrie informatique qui détermine les standards mémoires - a publié la spécification de ce qui sera le prochain standard mémoire de nos machines : la DDR4. Comme nous l'indiquions précédemment, là ou l'écart entre la publication de la DDR, DDR2 et DDR3 avait été entre chaque de quatre années, il aura fallu plus de sept ans entre la publication de la spécification de la DDR3 et celle de la DDR4.

Une longévité fortement accrue et qui s'est traduite par l'arrivée de barrettes qui dépassent très largement les objectifs d'origines de la DDR3 : on voit des modèles annoncés au-delà de la DDR3-2600 quand la spécification de la DDR3 ne validait officiellement les modules ne montant que jusqu'à 1600 (à l'origine, la spécification ayant été modifiée pour aller jusque 2133). Le JEDEC, qui n'aimait en général pas particulièrement ces dépassements (qui avaient existés auparavant, on se souvient par exemple de la DDR2-1066 là ou 800 était le maximum autorisé) à d'ailleurs fermé les yeux sur ces barrettes même si le communiqué reconnait que la DDR3 à "dépassé ses objectifs originaux de performances" et qu'il est probable que la DDR4 fasse de même.

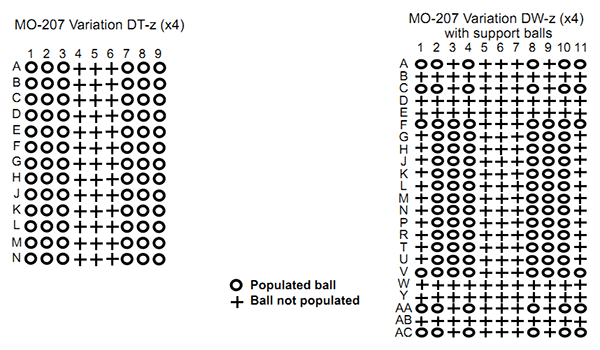

Nous avions déjà évoqué dans une actualité précédente quelques unes des grandes lignes techniques qui devaient être utilisées pour la DDR4, à savoir l'utilisation de transferts de largeurs variables (32, 64 ou 128 bits effectifs par transfert au lieu de 64 uniquement pour la DDR3) ou l'implémentation du concept DBI (Data Bit Inversion) qui permet de simplifier certains transferts en inversant les bits dans le but de limiter la consommation.

Version x4/x8 classique à gauche et version x16

L'organisation de l'adressage évolue avec l'apparition de groupes de banques indépendants les un des autres au sein puces. On trouve ainsi 2 groupes de 4 banques sur les puces x16 et 2 groupes de 4 banques sur les puces x16,, une nouveauté qui est à la base de l'amélioration des débits.

D'autres petits détails sont présents comme l'adaptation à la température de la puce qui doit pouvoir au minimum supporter 85°, un mode additionnel de fonctionnement jusqu'à 95° est également présent, dans ce cas les puces mémoires forceront un rafraichissement des données plus régulier pour éviter toute perte d'information (et plantage). Un mode de rafraichissement plus lent (période plus longue entre deux opérations) est également prévu pour un fonctionnement sous les 45°.

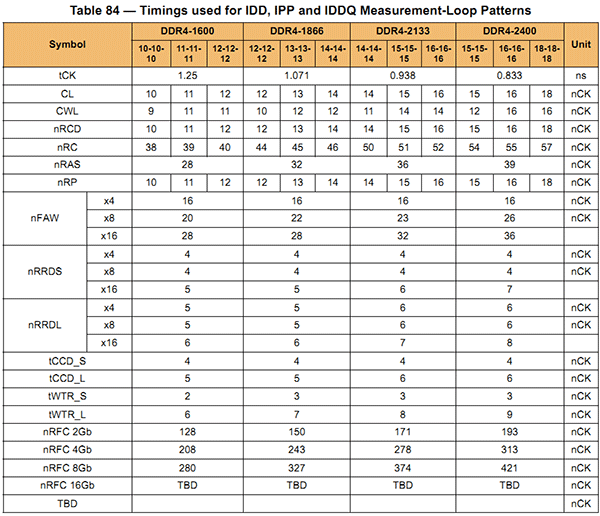

Du côté des débits, la DDR4 démarrera officiellement avec la DDR4-1600 (1600 MT/s) avec pour objectif d'atteindre 3200 MT/s d'ici à la fin de vie du standard. Les latences, exprimées en cycles paraitront forcément élevées même si l'on notera qu'elles sont assez proches de celles de la DDR3 actuelle (CAS 10 à 12 pour la DDR4-1600 au lieu de CAS9 couramment aujourd'hui pour la DDR3-1600). Ramenées en nanosecondes, ces latences restent très faibles et les multiples changements au niveau du fonctionnement interne font qu'il serait particulièrement faux de juger la DDR4 sur ces simples chiffres de latences.

Côté tensions, comme nous l'indiquions on passera de 1.5V à 1.2V pour la tension d'alimentation, sachant que des modules basse consommation (1.05V) sont également prévus (à l'image des barrettes DDR3 1.35V) sur le long terme. Une seconde tension de support à 2.5V (VPP) est également présente même si elle ne jouera qu'un rôle additionnel.

Nous nous devons enfin de noter que la spécification reste encore par endroit incomplète. Ainsi, si de manière normale certains timings ne sont pas encore définis au delà de 2400 MT/s, une (grande) partie de la spécification des timings électriques n'est pas du tout définie et ce pour toutes les fréquences de fonctionnement. Bien entendu cette première version de la spécification est amenée à évoluer d'ici à ce que les produits soient disponibles. La DDR4 est attendu pour rappel par Intel côté serveur pour 2014, et côté desktop pour 2015 au mieux comme nous l'indiquions ici .