Quelques détails sur les LPDDR4, DDR4 et Wide I/O

Publié le 10/04/2013 à 18:19 par Guillaume Louel

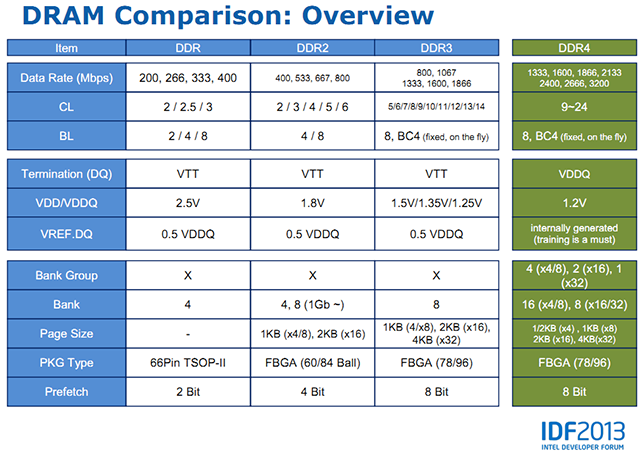

L'IDF de Pékin était aussi l'occasion pour Intel et ses partenaires d'évoquer les futurs standards mémoires DDR4 et LPDDR4. D'abord côté Intel ou l'on pouvait trouver ce slide qui compare les différentes versions de DDR :

Par rapport à la présentation que nous avions faite précédemment, on peut noter quelques petits changements. Notamment la mention des modes 3200 MT/s qui n'étaient que très peu évoquées dans la spécification originelle de la DDR4. Intel évoque ainsi des latences qui pourront atteindre 24 cycles. Pour le reste il s'agit des informations dont nous disposions déjà, pour rappel un des intérêts techniques principaux de la DDR4 tient dans l'organisation de l'adressage mémoire sous forme de groupes capables d'exécuter des instructions de manière indépendante.

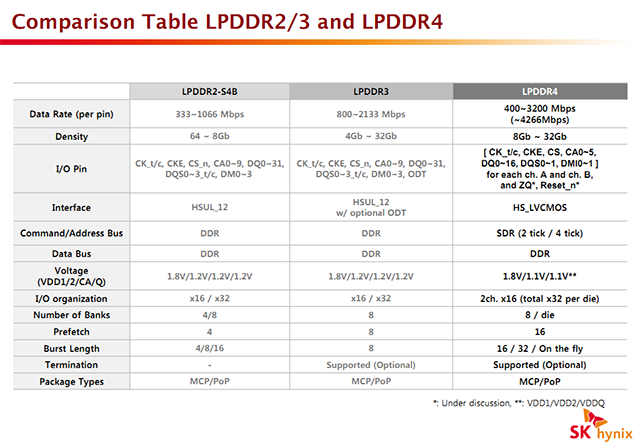

La LPDDR4 est également évoquée dans une présentation donnée par la société Hynix. Encore au rang de pré-standard pour le JEDEC, Hynix indique que la version finale devrait être ratifiée d'ici à la fin de l'année. Notez que si les noms se ressemblent, les standards LP ne sont pas identiques aux standards DDR classiques, à l'image de ce que l'on connait bien avec la GDDR par exemple. Les choix techniques effectués peuvent différer, l'objectif des standards LP étant de minimiser au maximum la consommation.

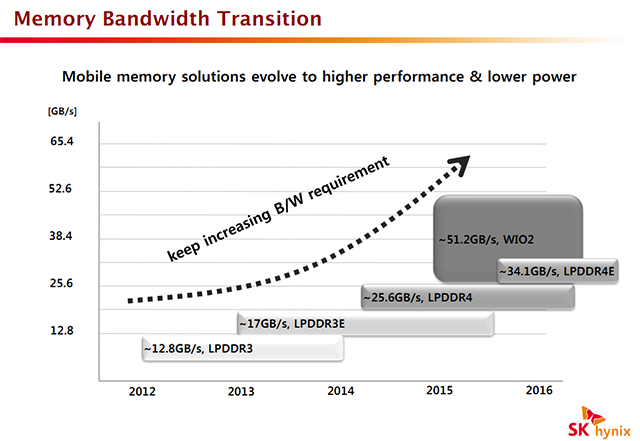

Comme toujours augmenter la bande passante est l'objectif, elle est doublée par rapport à la LPDDR3. On notera d'ailleurs sur ce graphique l'arrivée attendue d'un autre standard, Wide I/O 2. Un premier standard Wide I/O avait en effet été publié par le JEDEC fin 2011, il vise a standardiser la pratique dite du die stacking de mémoire, à savoir superposer des dies de mémoires par-dessus un SoC, le tout étant relié par le biais de TSV. La première version de Wide I/O avait avant tout pour but de régler les problèmes techniques autour de la solution et est relativement conservatrice en termes de débits, pouvant atteindre 17 Go/s (via une généreuse interface 512 bits !). La seconde version, attendue pour 2015 (le standard est encore loin d'être finalisé), visera des débits significativement plus élevés, pouvant atteindre 51 Go/s.

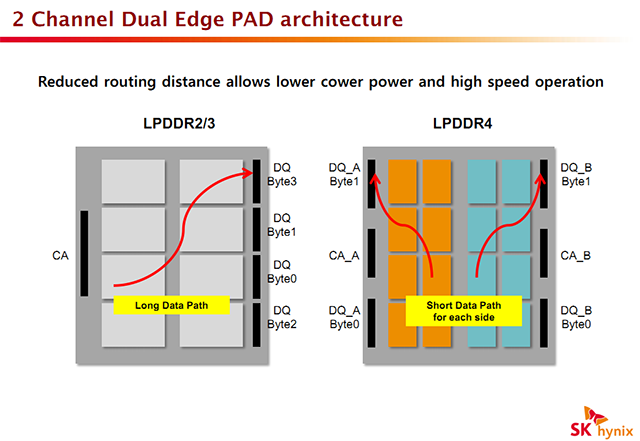

En ce qui concerne la LPDDR4, on notera au niveau des détails que la tension de base baisse de 1.2 à 1.1V par rapport à la LPDDR3, et une tension de terminaison qui est divisée par 3 (de 1.2V à 0.4V). Une réduction du routage fait également partie des objectifs attendus, ce qui devrait avoir pour conséquence un changement assez drastique dans le packaging.

Pour le reste, Hynix nous parait particulièrement optimiste en indiquant que la LPDDR4 sera disponible pour la mi-2014. Il faudra voir si cet enthousiasme sera partagé par le reste de l'industrie !

Vos réactions

Contenus relatifs

- [+] 22/12: Samsung grave de la DRAM en ''1ynm'...

- [+] 04/10: La DDR4 toujours en hausse, pénurie...

- [+] 14/09: Les prix de la DDR4 ont doublé en u...

- [+] 10/08: AMD Threadripper 1950X et 1920X en ...

- [+] 06/07: Arrêt d'une usine DRAM Micron, rume...

- [+] 29/06: Intel Core i9-7900X et Core i7-7740...

- [+] 20/06: Micron cède à la mode du RGB pour l...

- [+] 20/06: G.Skill monte à 4800 MHz sur KBX, 3...

- [+] 29/05: AMD évoque la prochaine version de ...

- [+] 02/04: Influence de la DDR4 sur Ryzen 7 18...