Les contenus liés aux tags TSMC et Process

Afficher sous forme de : Titre | FluxTSMC et InFo PoP pour l'A10 de l'iPhone 7

7nm fin 2018 pour GlobalFoundries ?

Nouvel accord WSA entre AMD/GlobalFoundries

Intel Custom Foundry prend une licence ARM !

L'ITRS prépare l'après loi de Moore

Des détails sur le 7nm à l'ISSCC 2017

La conférence ISSCC (International Solid-State Circuits Conference) se tiendra pour son édition 2017 du 5 au 9 février à San Francisco, et nos confrères d'EEtimes ont eu accès à l'avant programme.

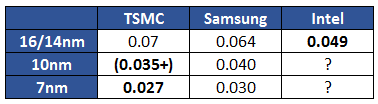

Comme tous les ans les acteurs du milieu des semi conducteurs y présenterons leurs nouveautés, et l'on notera que TSMC et Samsung présenterons leurs cellules SRAM (utilisées notamment pour la mémoire cache dans les puces). L'année dernière, Samsung avait proposé deux versions distinctes pour son process 10nm, optimisées pour la densité ou les performances, de 0.040 µm² et 0.049 µm².

D'après nos confrères, TSMC présentera une cellule SRAM 7nm de seulement 0.027µm², tandis que Samsung présentera une cellule SRAM 7nm de 0.030µm², mais fabriquée en EUV. D'après Samsung, l'EUV permettrait de diminuer la tension minimale nécessaire de 39.9mV (TSMC indique aussi des optimisations basse tension, on attendra la conférence pour comparer l'impact ou non de l'EUV).

La SRAM est un composant fondamental des puces et sa taille permet en général de se donner une bonne idée des process. Cependant il faut être assez méfiant, les constructeurs annonçant parfois des "records" de densité qu'ils n'utilisent pas forcément en production. Nous avons rapporté dans le tableau ci dessous les chiffres les plus bas (correspondant aux bibliothèques "hautes densité") pour TSMC, Samsung et Intel :

Par rapport au tableau, on notera qu'Intel n'utilise pas cette SRAM haute densité dans ses processeurs, mais de la SRAM 0.059 µm². Même en prenant cela en compte, Intel garde la meilleure densité à 16/14nm pour la SRAM. Le constructeur ne fournit pas encore d'infos sur ses futurs process.

TSMC n'a pas donné non plus de chiffre exact pour son 10nm, estimant simplement 50% de réduction par rapport à son 16nm sur la SRAM, ce qui nous vaut un chiffre entre parenthèses. Selon toutes vraisemblances, et conformément aux autres annonces sur la densité (2.1x d'après le constructeur), on estimera que TSMC devrait avoir une SRAM d'une taille légèrement inférieure à celle de Samsung.

Intel ne devrait pas effectuer d'annonce sur ce sujet lors de l'ISSCC, ce qui est assez dommage. Le constructeur devrait présenter les FPGA Altera Stratix 10 (14nm) tandis qu'AMD proposera une présentation plus en détails de Zen.

On notera aussi que Western Digital/Toshiba, ainsi que Samsung, présenterons des puces 3D NAND 512 Gbit TLC 64 couches. Dans le cas de Samsung, cette puce avait été annoncée cet été, plus de détails techniques devraient être disponibles. Pour Western Digital/Toshiba, cette puce avait été évoquée cet été comme objectif.

On notera que nos confrères pointent à raison un grand absent : une fois de plus, ni Intel, ni Micron, n'effectueront de présentation technique de leur mémoire 3D Xpoint !

Samsung annonce de futurs process 14 et 10nm

Samsung vient d'indiquer par un communiqué de presse qu'il proposera une quatrième version de son process 14nm. Baptisée 14PLU, elle fait suite au 14LPE (Low Power Early, la première version dispo lorsque les yields étaient faibles), 14LPP (Low Power Plus, version un peu plus optimisée lorsque les yields étaient stabilisés), 14LPC (possiblement Low Power Compact, la version réduit les couts et fait écho au 16FFC de TSMC, tout en ajoutant la possibilité de pouvoir fabriquer des radios, indispensable pour la fabrication de modems par exemple).

Samsung vient d'indiquer par un communiqué de presse qu'il proposera une quatrième version de son process 14nm. Baptisée 14PLU, elle fait suite au 14LPE (Low Power Early, la première version dispo lorsque les yields étaient faibles), 14LPP (Low Power Plus, version un peu plus optimisée lorsque les yields étaient stabilisés), 14LPC (possiblement Low Power Compact, la version réduit les couts et fait écho au 16FFC de TSMC, tout en ajoutant la possibilité de pouvoir fabriquer des radios, indispensable pour la fabrication de modems par exemple).

Comme souvent, ces "variantes" de process sont des itérations autour d'une même technologie. Elles sont l'occasion d'annoncer des gains obtenus par l'optimisation de l'exploitation des process. Dans le cas de la version U, Samsung annonce des performances "plus élevées" à consommation égale, avec des règles de design identiques à son process 14LPC. Pour Samsung, le 14LPU est adapté aux utilisations "hautes performances" qui requièrent "beaucoup de calculs".

Un appel du pied à peine voilé aux fabricants de GPU et de SoC haut de gamme. Si Samsung a réussi a obtenir la fabrication de quelques GPU Nvidia (notamment les GP107 des GTX 1050), il s'agit de puces plus petites avec des niveaux de performances moindres par rapport au haut de gamme, qui reste toujours fabriqué chez TSMC. De la même manière, si AMD a fabriqué Polaris chez GlobalFoundries (sur un process techniquement identique à celui utilisé par Samsung, GlobalFoundries utilisant le process de Samsung sous licence), il ne s'agit pas non plus du haut de gamme (les raisons d'AMD étant beaucoup plus complexes).

La compétition avec TSMC est excessivement rude pour Samsung, qui tente avec cette quatrième version de s'attirer de nouveaux marchés. Le dernier "gros coup" du fondeur avait été la co-fabrication des SoC A9 d'Apple, un marché obtenu grâce au retard annoncé de TSMC. Un retard comblé en dernière minute par le fondeur Taiwanais. Les comparaisons directes sont toujours à double tranchant, et si Samsung avait bel et bien un avantage de densité sur son concurrent, sur le plan des performances TSMC restait, malgré la précipitation, en tête.

Cette version 14LPU tentera de combler ce déficit d'image même si selon toutes vraisemblances, TSMC gardera une main mise sur le haut de gamme sur ce node.

En parallèle, Samsung annonce également un 10LPU, qui sera cette fois la troisième version du 10nm de Samsung. Contrairement au 14LPU, le 10LPU augmentera la densité par rapport aux 10LPE/LPP, et Samsung le présente comme le 10nm proposant le cout le plus faible "de l'industrie". Le nom de 10LPC aurait probablement été plus adapté pour décrire ce process mais peu importe !

Dans les deux cas, il s'agit d'annonces puisque les kits de développement (PDK) pour le 14LPU et le 10LPU ne seront disponibles qu'au second trimestre 2017 ! On ne s'attendra donc pas a voir des produits les exploiter rapidement, le 10LPP entrera en production en volume pour rappel mi-2017.

On notera enfin que Samsung confirme une fois de plus sa volonté d'utiliser la lithographie EUV à 7nm, pour au moins une partie des couches de la puce. On rappellera que le 7nm de Samsung devrait arriver plus tard que le celui de son concurrent, la société ayant sous entendu à plusieurs reprises ces dernières semaines que le 10nm aurait une durée de vie plus longue qu'annoncée par certains.

TSMC tente en effet de lancer la production 7nm volume avec un an de décalage par rapport au 10nm (soit respectivement Q4 2016 pour le 10nm, et Q4 2017 pour le 7nm). Un rythme infernal qui ne sera suivi par personne d'autre (et largement financé, faut-il le rappeler, par Apple), mais sur lequel TSMC semble extrêmement confiant.

Le 10nm LPE en production chez Samsung

Samsung vient d'indiquer par le biais d'un communiqué de presse avoir commencé la production en volume de son process de fabrication 10nm.

Samsung vient d'indiquer par le biais d'un communiqué de presse avoir commencé la production en volume de son process de fabrication 10nm.

Plus précisément, Samsung annonce avoir commencé la production en volume d'un SoC 10nm, une première pour l'industrie d'après eux. On se rappelle que TSMC doit de son côté lancer la production en volume de son propre 10nm ce trimestre.

La définition précise de la production en volume est toujours l'occasion d'interprétations diverses chez les fondeurs, on notera que Samsung indique que les premières puces seront disponibles dans des produits finis début 2017, et plus généralement en volume au courant de l'année. Un planning qui l'aligne dans les annonces avec son concurrent principal.

Si techniquement Samsung avait été plus agressif que TSMC côté densité sur le node 14/16, tout laisse penser que l'inverse va se produire. Les chiffres annoncés vont dans ce sens puisque le 10nm apporte selon Samsung un gain de densité de 30%. Selon les estimations du blog Semiwiki , si TSMC reprend un avantage de densité sur Samsung sur ce node, l'écart sera en pratique bien moindre que celui constaté à 14/16. On notera au passage que le fondeur indique utiliser du triple-patterning sur ce node.

La densité ne fait bien évidemment pas tout et Samsung évoque au choix 27% de performances en plus, ou 40% de consommation en moins. Des chiffres qui sont donnés pour les deux versions de son process sans plus de précisions. A l'image de ce qu'il avait fait pour le 14nm, Samsung proposera d'abord un 10LPE (early) et un 10LPP. C'est le 10LPE qui est entré en production volume aujourd'hui, le 10LPP étant prévu pour la seconde moitié de l'année 2017.

La société ne mentionne pas de clients ou de nombre de produits qui seraient qualifiés en 2017 mais rappelle que ses kits de développements sont disponibles.

Si Samsung produit pour ses propres besoins, la société dispose aussi d'une activité de fondeur pour clients tiers qu'ils tentent de développer petit à petit. Leur part de marché était de 5.3% en 2015, à titre de comparaison TSMC tenait 54.3% du marché cette même année.

Proposer du 10nm en même temps que le leader est une bonne chose, même si l'on sait que de nombreux clients ont annoncé passer directement au 7nm, en grande partie parce que ce dernier aura une durée de vie excessivement courte (un an chez TSMC). Chez Samsung, la durée de vie de ce node devrait être un peu plus longue, le 7nm étant prévu pour 2018.

10/7nm en avance pour TSMC, EUV pour le 5nm

TSMC vient de publier ses résultats financiers pour le troisième trimestre. Le fondeur taiwannais enregistre une hausse séquentielle de 17% (+22% par rapport à la même période sur 2015), au dessus de ses prévisions. Des bons chiffres qui s'expliquent selon TSMC par une forte demande sur le marché des smartphones.

Ramenés par process, le 16/20nm représente 31% des revenus de la société (contre 23% le trimestre précédent). Le 28nm voit sa part baisser à 24% des revenus, mais TSMC confirme que ses usines restent "pleinement utilisées".

En ce qui concerne les prochains nodes, TSMC a confirmé les informations publiées un peu plus tôt, à savoir l'avance prise par les process 10 et 7nm.

Le 10nm entre en production ce trimestre et les premiers produits finaux seront livrés au premier trimestre 2017. Ce node ne sera pour rappel utilisé que par les très gros clients de TSMC, à savoir Apple et possiblement Qualcomm. Les autres clients attendront le 7nm. La montée des yields est décrite comme "similaire" à celle du 16nm même si "techniquement plus difficile".

Le 7nm entrera en production "risque" au premier trimestre 2017 et TSMC s'empresse d'indiquer qu'il sera utilisé non seulement pour les smartphones, mais aussi pour des GPU, des puces serveurs, et des "PC et tablettes". TSMC décrit des tapeout aggressifs qui commenceront au début du second trimestre. 15 produits devraient être qualifiés en 2017.

La fondeur a également évoqué le 5nm, qui a quitté le stade de la recherche pure pour entrer dans une phase de développement. Et TSMC confirme qu'ils utiliseront de manière "extensive" la lithographie EUV. Cette dernière aurait fait des progrès sur tous les plans, que ce soit en fiabilité, ou sur les problèmes techniques complexes (masques, photo resist, etc). La production "risque" reste prévue pour la première moitié de 2019 (la production volume suit en général de 3 à 4 trimestres).

Lors de la présentation des résultats aux analystes financiers, le CEO de TSMC, Mark Liu, a réitéré une fois de plus voir "l'informatique haute performance" comme un marché sur lequel TSMC espère voir une progression de ses ventes. Les serveurs et les PC clients sont mis en avant, et on a du mal a ne pas y voir un lien avec les annonces d'AMD sur sa renégociation du contrat WSA qui les lie à GlobalFoundries.

Dans la séance de questions/réponses posées, on notera qu'a la question de savoir si la prise de licence ARM par Intel est un risque, Mark Liu estime surtout que cela renforce le rôle d'ARM, tout en ne négligeant pas le rôle qu'Intel pourrait jouer. Reste que sur ce trimestre, la part de marché de TSMC chez les fondeurs (hors activité propre comme Intel pour ses propres puces donc) était de 55%.

10 et 7nm en avance chez TSMC ?

Un des auteurs du blog SemiWiki a assisté à l'OIP Ecosystem Forum de TSMC et rapporte plusieurs informations intéressantes ayant été données par le fondeur taiwannais concernant ses process à venir.

Pour ce qui est du 10nm, TSMC serait en avance avec une production en volume (HVM) avancée d'un trimestre : au lieu de démarrer en Q1 2017, elle démarrera au dernier trimestre de cette année.

Le développement du 7nm, lié à celui du 10nm (voir notre article précédent) serait lui aussi en avance d'un trimestre. La production "risque" démarrera au premier trimestre 2017, et la production en volume au quatrième trimestre 2017.

La roadmap 10/7nm de TSMC, déjà excessivement agressive par rapport à la concurrence, le devient encore plus. TSMC utilisera pour rappel le même matériel pour la fabrication des deux nodes (avec une densité qui augmente largement, 1.63x annoncé entre 10 et 7nm) ce qui explique la manière dont les deux nodes avancent en simultanée.

On rappellera toutefois que si le 10nm sera disponible rapidement en volume, il ne devrait être utilisé que par les gros clients "mobiles" de TSMC (Apple et possiblement Qualcomm). La majorité des clients de TSMC (fabricants de GPU inclus) devrait passer directement au 7nm qui sera le vrai node "pour tous" (à l'image de ce que l'on a pu voir avec le 20nm et le 16nm).