Les contenus liés au tag 3D XPoint

Afficher sous forme de : Titre | FluxHMC, DDR5 et 3D XPoint pour Micron

V-NAND Gen4 et Z-NAND pour Samsung

PRAM 3D XPoint QuantX pour Micron

Roadmap SSD Intel : 3D NAND et 3D Xpoint

La 3D NAND arrive chez Micron, MX300 en vue ?

Optane : la série 100 suffit sur portables

Pour rappel, Intel a réservé aux nouveaux chipsets de la série 200 le support de la technologie Optane. Ces SSD de petite taille, 16 ou 32 Go, utilisent de la mémoire 3D Xpoint ultra rapide et sont utilisés pour faire office d'intermédiaire entre le support de stockage et la mémoire.

Mais sur la page dédiée à Optane du site d'Intel, on peut lire noir sur blanc que Optane est compatible avec les chipsets portables HM175 et QM175, qui appartiennent bel et bien à la série 100. Sortis à l'occasion de l'arrivée de Kaby Lake, ils ne constituent en réalité qu'une évolution très ténue des HM170 et QM170, seule la révision du firmware étant modifiée selon Ark .

On peut dès lors se poser une question simple : Intel bride-t-il Optane sur les chipsets de la série 100 (qui disposent de la compatibilité NVMe et d'un port M.2) via ses pilotes RST afin de mettre en avant sa série 200 ? Même si on s'en doutait déjà, cela ne fait que renforcer cette supposition.

Heureusement ce bridage, contrairement à d'autres, n'est pas très problématique vu l'intérêt limité d'Optane : Intel lui-même met en avant une réactivité comparable à un SSD en couplant HDD et Optane autant utiliser un SSD directement alors ? Voilà qui nous rappelle les SSD lorsqu'ils étaient utilisés comme accélérateur via la technologie Intel Smart Response, ce qui ne nous avait pas non plus convaincu à l'époque.

A lire également : Les premiers portables avec Optane présentés au CES

Les premiers portables avec Optane au CES

Lenovo a présenté un peu en avance sur son blog les prochains modèles de PC portables qu'ils introduiront au CES.

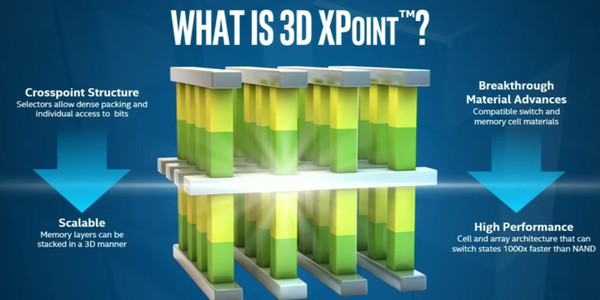

Ce qui retient notre attention est la présence du support de la technologie Optane d'Intel. Pour rappel, Intel avait présenté un nouveau type de mémoire sous le nom 3D Xpoint, s'intercalant entre la mémoire RAM (peu dense mais très rapide) et la NAND (très dense, moins rapide).

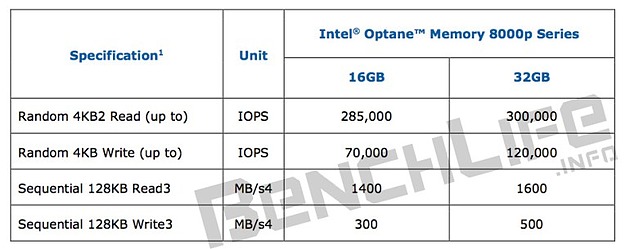

Le premier produit qui utilisera cette nouvelle mémoire est un accélérateur connu sous le nom de code Stony Beach et qui sera commercialisé comme Optane 8000p. Ces accélérateurs système se présentent sous la forme de cartes au format M.2 et Intel devrait lancer deux versions, en 16 et 32 Go. Lenovo indique qu'il proposera le modèle 16 Go sur certains de ses portables haut de gamme, en M.2 2241 (4.1 cm de long).

La manière exacte dont "l'accélération" sera effectuée reste assez floue aujourd'hui, une piste probable étant le mode SRT (Smart Response Technology) des pilotes disques RST d'Intel. Dans ce cas l'accélérateur servira de cache pour les disques systèmes. Si Intel avait mis au point ce système de cache pour les disques durs SATA traditionnels à plateaux, on notera que les dernières versions supportent également les SSD NVMe.

Si Optane a un avantage de latence net par rapport à la NAND, les chiffres d'IOPS annoncés pour les modèles 16 Go ne changent pas dramatiquement la donne par rapport aux derniers SSD haut de gamme

Intel devrait dévoiler un peu plus de détails sur le fonctionnement exact de la technologie dans quelques jours lors du CES, ainsi qu'effectuer des démonstrations.

Il sera intéressant de voir en pratique ce que cela apporte, car si proposer un cache en amont d'un disque dur à plateaux sera forcément bénéfique, l'impact pratique d'Optane accolé à un SSD rapide utilisant ses propres stratégies de cache (RAM + utilisation de MLC/TLC comme SLC en écriture) risque d'être plus difficilement perceptible sur une utilisation grand public, au delà de quelques benchs savamment choisis !

Des détails sur le 7nm à l'ISSCC 2017

La conférence ISSCC (International Solid-State Circuits Conference) se tiendra pour son édition 2017 du 5 au 9 février à San Francisco, et nos confrères d'EEtimes ont eu accès à l'avant programme.

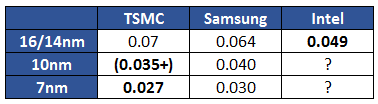

Comme tous les ans les acteurs du milieu des semi conducteurs y présenterons leurs nouveautés, et l'on notera que TSMC et Samsung présenterons leurs cellules SRAM (utilisées notamment pour la mémoire cache dans les puces). L'année dernière, Samsung avait proposé deux versions distinctes pour son process 10nm, optimisées pour la densité ou les performances, de 0.040 µm² et 0.049 µm².

D'après nos confrères, TSMC présentera une cellule SRAM 7nm de seulement 0.027µm², tandis que Samsung présentera une cellule SRAM 7nm de 0.030µm², mais fabriquée en EUV. D'après Samsung, l'EUV permettrait de diminuer la tension minimale nécessaire de 39.9mV (TSMC indique aussi des optimisations basse tension, on attendra la conférence pour comparer l'impact ou non de l'EUV).

La SRAM est un composant fondamental des puces et sa taille permet en général de se donner une bonne idée des process. Cependant il faut être assez méfiant, les constructeurs annonçant parfois des "records" de densité qu'ils n'utilisent pas forcément en production. Nous avons rapporté dans le tableau ci dessous les chiffres les plus bas (correspondant aux bibliothèques "hautes densité") pour TSMC, Samsung et Intel :

Par rapport au tableau, on notera qu'Intel n'utilise pas cette SRAM haute densité dans ses processeurs, mais de la SRAM 0.059 µm². Même en prenant cela en compte, Intel garde la meilleure densité à 16/14nm pour la SRAM. Le constructeur ne fournit pas encore d'infos sur ses futurs process.

TSMC n'a pas donné non plus de chiffre exact pour son 10nm, estimant simplement 50% de réduction par rapport à son 16nm sur la SRAM, ce qui nous vaut un chiffre entre parenthèses. Selon toutes vraisemblances, et conformément aux autres annonces sur la densité (2.1x d'après le constructeur), on estimera que TSMC devrait avoir une SRAM d'une taille légèrement inférieure à celle de Samsung.

Intel ne devrait pas effectuer d'annonce sur ce sujet lors de l'ISSCC, ce qui est assez dommage. Le constructeur devrait présenter les FPGA Altera Stratix 10 (14nm) tandis qu'AMD proposera une présentation plus en détails de Zen.

On notera aussi que Western Digital/Toshiba, ainsi que Samsung, présenterons des puces 3D NAND 512 Gbit TLC 64 couches. Dans le cas de Samsung, cette puce avait été annoncée cet été, plus de détails techniques devraient être disponibles. Pour Western Digital/Toshiba, cette puce avait été évoquée cet été comme objectif.

On notera que nos confrères pointent à raison un grand absent : une fois de plus, ni Intel, ni Micron, n'effectueront de présentation technique de leur mémoire 3D Xpoint !

16 et 32 Go pour les premiers Intel Optane ?

Nos confrères de Benchlife ont publié une actualité concernant l'arrivée de ce qui serait le premier produit Intel Optane grand public. Pour rappel, Optane est le nom commercial donné à la mémoire PRAM 3D Xpoint d'Intel, une mémoire non volatile à mi chemin entre la RAM et la NAND.

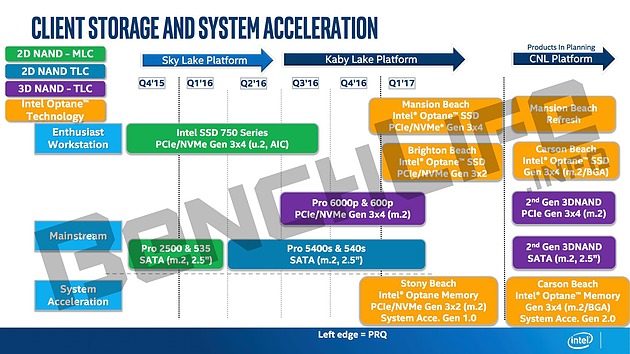

En juin dernier, ces mêmes confrères avaient publié un extrait de la roadmap d'Intel ou l'on pouvait voir les trois produits Optane qui seraient proposés. Le premier devant arriver sur le marché utilisant le nom de code Stony Beach. Il est décrit comme un "accélérateur système".

C'est sur ce dernier que nos confrères ont publié de nouvelles informations, ce Stony Beach prendra le nom d'Intel Optane 8000p. On les retrouvera au format M.2 dans des déclinaisons 2241 et 2280 (4.1 et 8cm de long).

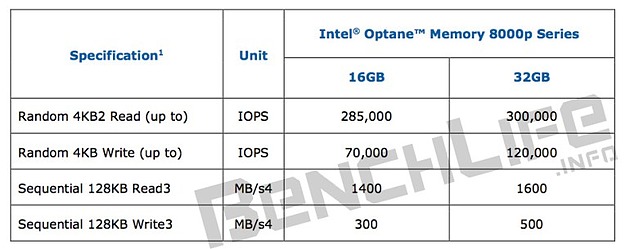

Deux capacités sont annoncées, et c'est la première surprise : seulement 16 et 32 Go. Des chiffres particulièrement contenus, sachant qu'un des avantages mis en avant pour la technologie est sa densité 10x supérieure à celle de la mémoire DRAM traditionnelle.

L'autre surprise concerne les performances annoncées. Côté débits là aussi les chiffres annoncés pour ces accélérateurs ne sont pas révolutionnaires :

Les chiffres d'IOPS bruts sont même en dessous de ceux annoncés par les tous derniers SSD en M.2 comme le 960 Pro de Samsung par exemple.

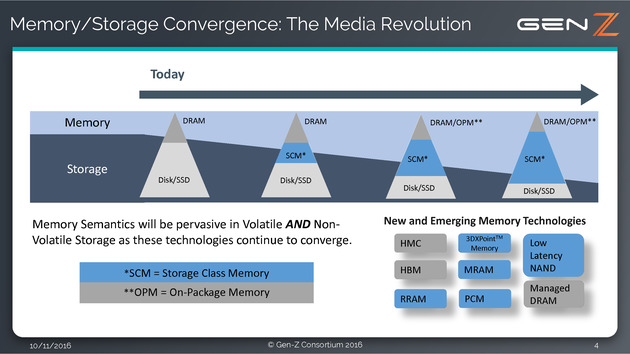

La différence devrait se faire sur la latence, plus faible, mais on peut se demander comment ce tiers de mémoire supplémentaire s'intercalera dans les systèmes d'exploitations. L'hypothèse la plus probable est que ces modules seront vus comme des disques de stockage qui fonctionneront sous Windows via la technologie ReadyBoost (qui peut utiliser un périphérique USB comme cache disque). Un scénario d'utilisation qui ne profiterait pas forcément énormément de l'avantage de latence, surtout sur un système qui disposerait déjà d'un SSD. On se souviendra il y a quelques jours de l'annonce du consortium Gen-Z pour tenter de répondre, entre autre, à cette problématique.

On attendra de voir comment Intel mettra en avant ces produits, et s'il s'accompagnera d'une annonce d'un mode de support alternatif sous Windows. La question du prix sera également d'importance. Leur lancement est attendu avant la fin de l'année avec un support exclusif (on imagine pour des raisons marketing) de la plateforme Kaby Lake.

Alliance autour d'un nouveau bus mémoire

Plusieurs acteurs majeurs de l'industrie viennent d'annoncer une alliance dans le but de développer une nouvelle interface mémoire. Ils se sont regroupés au sein d'un consortium baptisé Gen-Z.

La page de description du consortium insiste sur un mode de fonctionnement transparent et ouvert. Le consortium en lui même est une organisation à but non lucratif (pour les puristes, une entreprise américaine de type "not for profit"). Le mode de développement sera transparent, et le standard final sera publié, disponible et utilisable gratuitement.

Techniquement il s'agit de proposer une nouvelle manière d'interconnecter la mémoire, ou plutôt les multiples types de mémoires qui pourront coexister à l'avenir.

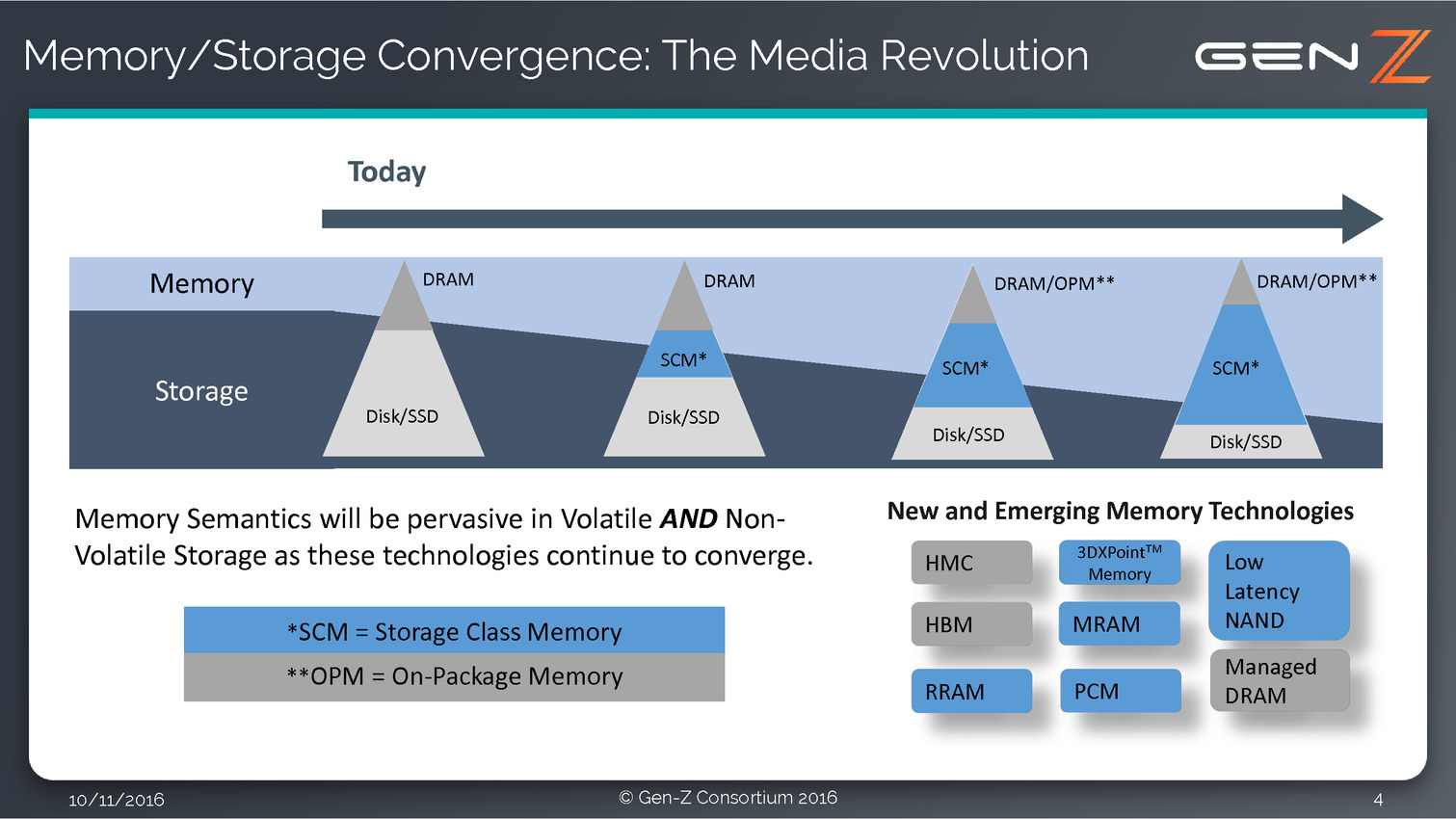

Le consortium prend l'exemple des nouveaux "types" de mémoires, appelés SCM (Storage Class Memory) comme peuvent l'être les RRAM, MRAM, ou les implémentations commerciales annoncées comme 3D XPoint chez Intel/Micron ou la Z-NAND de Samsung. Ces nouveaux types de mémoires viennent s'ajouter à la mémoire traditionnelle (DRAM) qui voit aussi arriver de nouvelles variantes (HBM ou HMC).

L'idée de base du consortium est de proposer une interface avec des commandes très simples, proches de celles utilisées pour la DRAM, mais qui puissent être utilisées aussi bien au sein d'un package, sur la carte mère, ou au delà (communication entre serveurs dans un data center). Le tout se doit de rester compatible avec l'existant, y compris les systèmes d'exploitations qui pourront exploiter ces nouvelles mémoires de manière transparente. Un but assez noble tant la question de comment adresser ce nouveau tiers de mémoire avait été évitée jusqu'ici.

Le consortium annonce qu'il utilisera entre autre le protocole IEEE 802.3 (Ethernet) comme protocole de communication interne (on pourra aussi utiliser Ethernet pour la couche physique de transport). En plus des protocoles, un nouveau connecteur devrait être annoncé pour tenter de standardiser ces futurs types de mémoire, il supportera jusque 112 GT/s.

Les objectifs fixés sont particulièrement audacieux, et on ne pourra que se féliciter de voir tant d'acteurs majeurs de l'industrie s'associer pour tenter de proposer un nouveau standard :

L'absent le plus notable est Intel, et il est difficile de ne pas voir cette alliance comme formée contre la firme de Santa Clara qui a tendance à développer ses bus de manière propriétaires, particulièrement pour tout ce qui touche au monde serveur.

Il est tout de même intéressant de voir que Micron, partenaire d'Intel sur 3D Xpoint est présent dans le consortium (3D Xpoint est même mentionné dans les slides de présentation). Il sera intéressant de suivre l'évolution de ce standard qui pourrait apporter des solutions concrètes aux problématiques d'interconnexions.

Vous pouvez retrouver la présentation du consortium ci dessous :