Les contenus liés au tag 10nm

Afficher sous forme de : Titre | FluxL'ITRS prépare l'après loi de Moore

Samsung présente sa SRAM 10nm

3 architectures 10nm pour Intel ?

TSMC vise 2020 pour le 5nm via l'EUV

Résultats TSMC, 16 FinFET+ dans l'iPhone 6s

1er tape-out 10nm ARM chez TSMC

ARM vient d'annoncer qu'il avait effectué le tape-out d'un puce de test en 10nm chez TSMC. Cette puce intègre 4 coeurs Artemis, le successeur du Cortex-A72, utilisant l'architecture ARMv8-A mais un iGPU simplifié avec un seul coeur graphique. Le communiqué précise que le tape-out, c'est-à-dire l'envoi des informations chez TSMC pour graver la puce, a eu lieu au quatrième trimestre 2015.

ARM a précisé à AnandTech que le tape-out avait en fait eu lieu en décembre, mais que si la validation de la puce de test est un succès il est question d'un retour de la puce chez ARM dans les semaines à venir, soit un délai tout de même assez long.

[ 1 ] [ 2 ]

Du coup les chiffres annoncées, qui font état selon les cas de 11-12% de performances en plus pour une même consommation que le 16nm ou d'une consommation réduite de 30% pour les mêmes performances, sont en fait des simulations. Dans le même temps la densité du 10nm TSMC devrait être jusqu'à 2.1x plus importante que celle du 16nm.

Cette annonce fait suite à un partenariat datant d'octobre 2014 sur le 10nm. Pour rappel le début de la production en volume pour le 10nm chez TSMC est prévu pour 2017, mais à l'instar du 20nm une partie des clients attendront le node suivant (7nm) en 2018.

Quelques nouvelles du 10 et 7nm chez TSMC

TSMC tenait la semaine dernière à San José son symposium, une conférence au cours de laquelle le fondeur taiwanais a partagé des détails inédits sur ses prochains process de fabrication de puces. Des détails rapportés par nos confrères d'EETimes et de Semiwiki (partie 1 et partie 2 ).

16FF+ et 16FFC

Pour le 16nm, si Apple l'utilise depuis de longs mois, les autres clients semblent peiner à lancer leur production, probablement à cause des coûts importants engendrés par la nouvelle technologie et aussi de quelques limites de capacité. TSMC s'est contenté de confirmer que son 16FF+ est en production "volume" (c'est à dire dédiée à des produits finis) depuis le troisième trimestre 2015 et qu'il s'attend à ce que son volume de wafers 16nm augmente significativement entre juin et octobre avec pour but d'atteindre 300 000 wafers par trimestre d'ici à la fin de l'année. Plusieurs produits 16FF+ sont déjà en production, comme les FPGA de Xilinx.

En parallèle TSMC propose également une version "compacte" (16FFC) de son process qui tente de réduire les coûts en diminuant par exemple le nombre de masques nécessaires. Cette version FFC sera celle qui sera privilégiée pour les usages non haut de gamme, même si elle propose plusieurs avantages intéressants, par exemple pour les usages très basse consommation (tension d'alimentation de 0.5V), mais aussi pour une version spécifique aux usages automobiles (une variante qui attendra mi 2017). TSMC avait annoncé cette variante publiquement en janvier, mais la production en volume sera entamée dès le mois d'avril. 70 tapeout 16FFC sont attendus cette année (à titre de comparaison, il y a déjà eu 70 tapeout 16FF+ en 2016), il sera intéressant de voir quels produits l'utiliseront !

10nm

TSMC est confiant sur l'arrivée du 10nm, même s'il s'agira vraisemblablement d'un node qui ne sera pas utilisé par tout le monde. La production en volume prendra place dans la Fab 15, dans deux nouvelles tranches construites pour l'occasion (les autres tranches produisent en 28nm). Le constructeur s'attend à produire 200 000 wafers par trimestres d'ici la fin de l'année 2017. Un premier tapeout 10nm pour un produit d'un de ses clients aurait été réalisé et la qualification est attendue au troisième trimestre cette année.

Malgré tout le 10nm reste un node qui sera limité côté clients, Xilinx ayant par exemple indiqué publiquement qu'ils attendraient le 7nm. Étant donné les délais suspicieusement courts entre le 10 et le 7nm, on peut les comprendre (productions en volume respectives annoncées pour 2017 et 2018) !

7nm

L'attente autour du 7nm est importante, et TSMC a commencé a donner quelques réponses à nos interrogations. D'abord, le fondeur proposera dès le début deux versions distinctes de son process 7nm, une version dédiée au mobile, et une autre aux produits hautes performances (+10 à 15% de performances en plus, avec pour but d'atteindre 4 GHz).

Les deux variantes devraient entrer en qualification en simultané au premier trimestre 2017. Pour expliquer le délai court entre le 10 et le 7nm, nous avions spéculé que le constructeur utiliserait une stratégie identique à celle utilisée entre le 20 et le 16nm, à savoir utiliser un BEOL (la partie basse de la puce qui contient les couches métalliques d'interconnexion) commun ce qui limiterait les gains de densité.

Après avoir évité a plusieurs reprises de répondre à la question dans ses conférences aux investisseurs, TSMC a confirmé que ce ne sera pas le cas : la variante mobile du 7nm apportera une densité 1.63x supérieure à celle de son 10nm ! C'est certes moins que le passage 28 à 20nm (1.9x) mais largement au dessus de la transition 20 à 16nm (1.15x, obtenu principalement par des optimisations des règles de design). Par rapport au 10nm, le 7nm devrait apporter 15 à 20% de performances en plus, ou 35 à 40% de consommation en moins selon les usages.

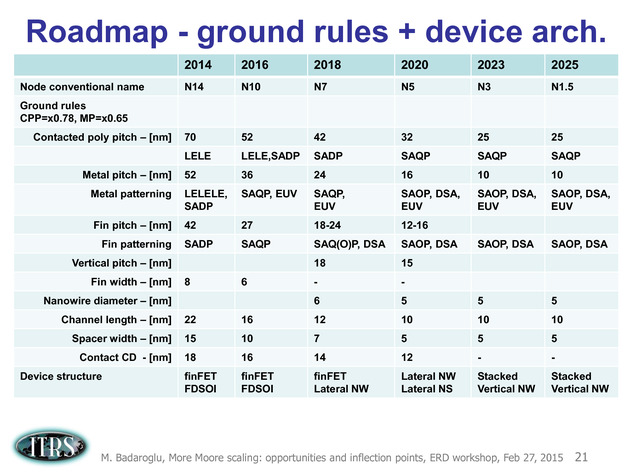

TSMC utilisera un matériel commun à 95% entre le 10 et le 7, facilitant la transition. La différence tiendra sur l'utilisation plus massive à 7nm du quadruple patterning (on ne sait pas encore exactement ou il sera utilisé, il semblait entendu sur les dernières roadmaps ITRS que le quadruple patterning - SAQP - serait utilisé pour les couches métal à 10 et 7 par exemple).

Le développement du 7nm avance puisque TSMC a indiqué avoir déjà produit des modules de SRAM de 128 Mbit, atteignant déjà des yields de 30% pour des dies pleinement fonctionnels. Il est toujours difficile de comparer ces chiffres tant les constructeurs les gardent secrets. En février 2010, soit une vingtaine de mois avant le lancement des premiers GPU 28HP (les Radeon 7970), TSMC annonçait cependant des yields sur sa SRAM de 26% . Atteindre 30% sur des puces pleinement fonctionnelles semble donc particulièrement encourageant à ce stade.

Si l'on considère les difficultés attendues par tous à 10 et à 7nm, la roadmap de TSMC semble particulièrement agressive et il faudra voir si le fondeur arrive a l'exécuter. On comprendra en tout cas qu'il ne faudra pas s'attendre à voir de 10nm ailleurs que chez Apple, ou possiblement Qualcomm étant donné les délais.

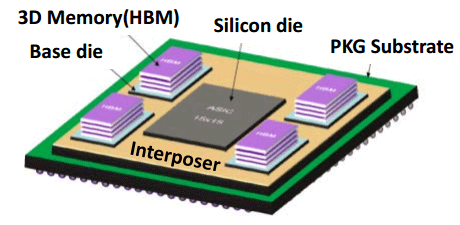

On conclura sur quelques informations données côté packaging, TSMC pense que c'est de ce côté que l'on réalisera des gains "faciles" et importants. D'abord pour la version haute performance CoWoS (Chip on Wafer on Substrate) qui consiste à utiliser un interposer en silicium pour relier des puces, le fondeur indique que l'on pourra atteindre des tailles plus importantes à 7nm dépassant les 1200mm2 (l'interposer utilisé par AMD sur les Fury X mesure un peu plus de 1000mm2) ce qui devrait donner un peu plus de marge. TSMC a également indiqué avoir réalisé le tapeout le mois dernier d'un "CPU" accompagné de deux piles de mémoire HBM2.

Côté mobile, c'est l'InFO WLP (Integrated FanOut Wafer Level Packaging) qui devrait apporter des gains intéressants. Par rapport au CoWoS, il s'agit d'une version beaucoup plus fine qui réduit voir élimine le substrat en "moulant" un ou plusieurs dies pour reconstituer un package très fin. TSMC annonce 20% de performances en plus pour une consommation 10% inférieure.

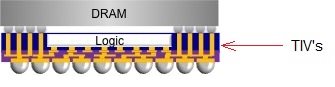

Exemple d'InFO POP

TSMC a rajouté une variante POP qui ajoute la possibilité de superposer un autre package (par exemple mémoire) par dessus un package InFO. TSMC utilise des fils dans les parties neutres du die pour relier la puce du dessus (des TIV, un concept identique aux TSV - through silicon Vias - si ce n'est que les fils traversent cette fois ci le package InFO et non un interposer). La production des InFO POP devrait débuter au second trimestre, ce qui coïncide côté timing avec le début de production attendu du prochain SoC d'Apple qui devrait utiliser ces technologies de packaging.

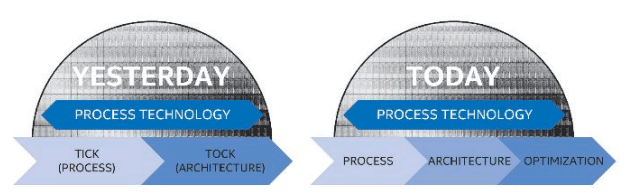

De Tick Tock à Process Architecture Optimization

Intel avait confirmé l'abandon de sa stratégie "Tick-Tock" lors de la présentation de ses résultats financiers en juillet dernier, indiquant alors que le 14nm allait être utilisé par 3 générations de produits : Broadwell (le Tick), Skylake (le Tock) et Kaby Lake. Plutôt que de parler de Tack pour Kaby Lake, le rapport annuel d'Intel met en avant une nouvelle dénomination pour cette stratégie : Process, Architecture, Optimization.

Kaby Lake sera donc la version "Optimization", alors que Cannon Lake prévu pour le second semestre 2017 sera le produit "Process" inaugurant le 10nm. Intel précise à cette occasion qu'il allongera également le temps d'utilisation de son 10nm, ce qui vient confirmer la rumeur de janvier dernier indiquant qu'il lancera Icelake en 2018 puis Tigerlake en 2019, tous en 10nm. Pourquoi ne pas avoir garder le Tick-Tock mais en séparant les deux de 18 mois ? Tout simplement pour conserver le lancement de produit annuel nécessaire à la bonne tenue de ses ventes, quitte à ce que les améliorations soient ténues.

Étonnamment Intel continue malgré tout de citer la loi de Moore dans la partie R&D de ce même document alors même que l'utilisation pendant 3 ans d'un même process confirme qu'il faut désormais s'en détacher. Les vieilles habitudes ont la vie dure !

L'EUV possiblement pour le 7nm ?

Le site SemiWiki nous rapporte quelques informations sur l'état de la fabrication EUV, en provenance de la conférence SPIE Advanced Lithography qui se tient actuellement à San José.

Lors de la même conférence l'année dernière, les nouvelles étaient pour rappel plutôt bonnes (voir le lien pour un rappel complet sur la fabrication des processeurs et l'importance capitale de l'EUV !) et l'on espérait une introduction en cours de process pour le 10nm, et une introduction complète à 7nm. Malheureusement, on le rappelait en janvier, TSMC avait calmé les ardeurs en indiquant qu'il faudrait attendre le 5nm pour une éventuelle introduction de cette technologie.

SemiWiki confirme certains chiffres donnés lors de la dernière conférence aux investisseurs de TSMC, à savoir que la machine avait atteint sur une période de quatre semaines une production de 518 wafers/jour, un niveau encore largement insuffisant. Intel a partagé également quelques chiffres, un peu inférieurs à ceux de TSMC, à savoir entre 2000 et 3000 wafers par semaine (285-428 par jour).

On notera quand même que le taux de disponibilité des scanners de la société ASML a augmenté, passant de 55 à 70% chez TSMC (Intel rapportant une disponibilité identique) ! On notera que s'il est question d'une introduction en début de node à 5nm, TSMC laisse la porte ouverte pour le 7nm si jamais des progrès étaient effectués. Intel de son côté n'a pas donné d'information. Samsung envisagerait l'introduction à 7nm selon les présentations, sans plus de précisions.

Si la question de la disponibilité est importante, celle de la puissance de la source lumineuse l'est encore plus. Après avoir été limité à 40 watts l'année dernière, les machines actuellement en évaluation chez TSMC disposent désormais de sources 80 watts. C'est mieux, mais cela reste loin des 250 watts promis par ASML pour fin 2015. Les dernières prédictions sont désormais de 250 watts en 2016-2017, et au delà en 2018-2019, des plages particulièrement larges.

Atteindre les 250 watts de puissance permettrait d'augmenter significativement la cadence de production, atteignant 170 wafers/heure en théorie. ASML a effectué des démonstrations que TSMC et Intel semblent juger prometteuses de 185 et 200 watts. Reste à les voir en production, bien évidemment. Les challenges de cette technologie restent complexes et ne se limitent pas à ces deux points cruciaux, la question des défauts dans les masques est elle aussi importante même si là aussi TSMC et Intel ont visiblement noté quelques progrès. Vous pouvez retrouver plus de détails sur ces points dans l'article de SemiWiki .

Accélération SHA pour Cannonlake

Quelques petites informations et confirmations sont apparues ce week-end à propos de Cannonlake, la future architecture processeur d'Intel prévue pour la seconde moitié de 2017, et qui sera la première du constructeur à être produite dans un procédé de fabrication 10nm.

Quelques petites informations et confirmations sont apparues ce week-end à propos de Cannonlake, la future architecture processeur d'Intel prévue pour la seconde moitié de 2017, et qui sera la première du constructeur à être produite dans un procédé de fabrication 10nm.

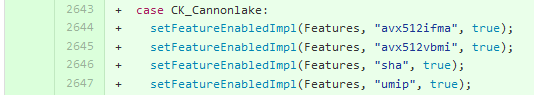

C'est par la publication d'un patch pour Clang, le compilateur C/C++/Obj-C de LLVM que l'on aura obtenu d'abord quelques confirmations sur le support d'AVX-512. Le patch en question que vous pouvez retrouver ici concerne l'énumération des fonctionnalités des familles de processeur. L'intérêt de ce code est de permettre aux développeurs, indépendamment de la machine qu'ils utilisent, de compiler des versions optimisées de leurs programmes pour une architecture donnée (par exemple, optimisée pour Skylake en ajoutant -march=skylake, plus de détails sur le sujet dans cet article).

Le patch, en développement depuis début février , indique le support spécifique de certains jeux d'instructions en fonction des familles. On retrouve ainsi les deux déclinaisons de Skylake, la version "client" (celle disponible pour les PC portables et de bureau) et la version "serveur" pour les Xeon. Cette dernière se différencie pour rappel par son support d'une partie du jeu d'instruction AVX-512.

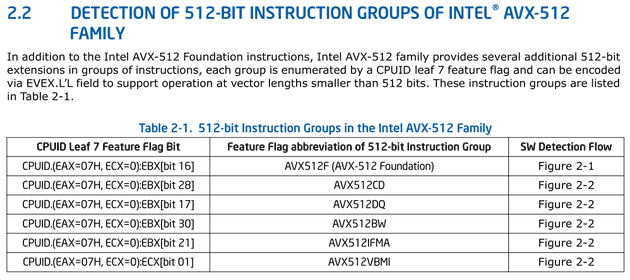

Pour ce patch, Intel ne spécifie qu'une seule version de Cannonlake et l'on retrouve, comme promis, le support des instructions AVX-512. De manière plus précise, en plus des instructions déjà supportées par la version Xeon de Skylake, deux autres extensions sont présentes, avx512ifma et avx512vbmi (une information que nous avions notée l'année dernière). L'extension avx512ifma concerne les instructions dites fused multiply add (par exemple A x B + C), appliquées cette fois ci à des nombres entiers (sur une précision de 52 bits). avx512vbmi rajoute des instructions de manipulation/permutations vectorielles d'octets (Vector Byte Manipulation Instructions).

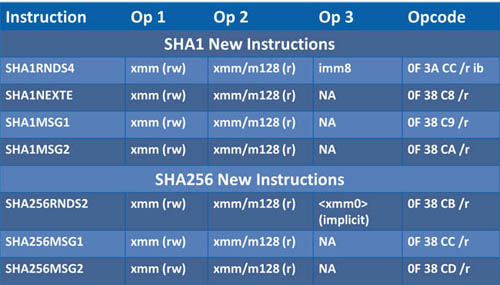

L'autre information est la confirmation de l'arrivée d'instructions dédiées aux calculs de hash cryptographiques. Les instructions sha font, sans trop de doute, référence à ces instructions présentées en 2013 par Intel , capables d'accélérer le calcul de hash aux formats SHA-1 et SHA-256 . Elles devraient être donc introduites pour la première fois sur Cannonlake.

On notera également dans le patch la mention d'une autre extension, umip pour laquelle nous n'avons pas encore trouvé de référence dans la documentation d'Intel !