La GDDR5X standardisée par le JEDEC

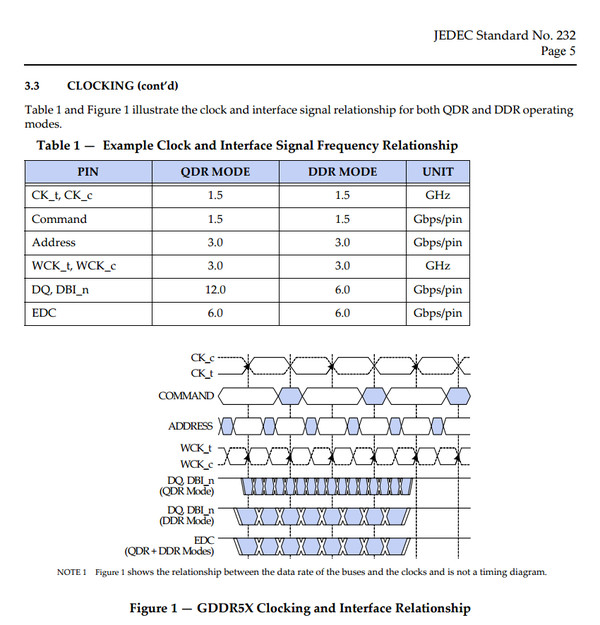

Le JEDEC vient d'annoncer la publication des spécifications de la GDDR5. Le standard JESD232, daté de novembre 2015, définit la GDDR5X telle qu'elle a déjà été présentée par Micron. La GDDR5X supporte deux modes pour les données, un DDR similaire à celui de la GDDR5 fonctionnant avec un prefetch de 8n et des accès de 256 bits, et un QDR permettant de doubler à fréquence égale le débit avec en contrepartie un prefetch de 16n et des accès de 512 bits. Côté capacité le standard intègre des versions 12 et 16 Gbits là ou la GDDR5 se limitait à 8 Gb.

Le JEDEC indique que la GDDR5X cible des débits allant de 10 à 14 Gbps, soit 320 à 448 Go /s en bus 256 bits, mais Micron avait déjà évoqué la possibilité à terme d'atteindre 16 Gbps soit 512 Go /s. Ce dernier débit sera atteint avec seulement 2 puces de HBM2, une consommation moindre et probablement une meilleure bande passante effective du fait d'accès plus petits de 256 bits (voir 128 bits en mode Pseudo Channel), mais la GDDR5X devrait avoir l'avantage en terme de coût d'autant qu'elle évite de passer par un interposer.

Pour l'instant seul Micron, qui ne s'est pas positionné sur la HBM2 a contrario de SK Hynix et de Samsung, a annoncé qu'il allait produire de la GDDR5X mais rien n'empêche d'autres fabricants membre du JEDEC de se lancer.

Contenus relatifs

- [+] 18/07: Samsung augmente la production de H...

- [+] 13/10: Alliance autour d'un nouveau bus mé...

- [+] 29/08: Hot Chips : M1, SVE, Parker, InFo e...

- [+] 22/08: Samsung évoque la GDDR6

- [+] 22/08: HMC, DDR5 et 3D XPoint pour Micron

- [+] 22/08: SK Hynix et Samsung parlent de HBM

- [+] 15/07: La HBM2 Hynix dispo ce troisième tr...

- [+] 05/04: GTC: Nvidia Tesla P100: 10 Tflops, ...

- [+] 11/03: La HBM 2 SK Hynix en retard

- [+] 22/01: La GDDR5X standardisée par le JEDEC