IDF - Printemps 2005

Publié le 09/03/2005 par Damien Triolet

Lors de cet IDF, Intel a mis un point dhonneur à rassurer sur les possibilités technologiques futures. Il a souvent été question de limitations à moyen terme de la technologie CMOS, au niveau des performances des transistors et de leur fabrication mais Intel affirme ici clairement quil y a encore de la marge et lexprime principalement via 3 technologies sur lesquelles leur département R&D travaille.

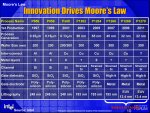

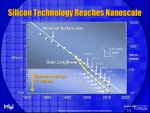

Lors de cet IDF, Intel a mis un point dhonneur à rassurer sur les possibilités technologiques futures. Il a souvent été question de limitations à moyen terme de la technologie CMOS, au niveau des performances des transistors et de leur fabrication mais Intel affirme ici clairement quil y a encore de la marge et lexprime principalement via 3 technologies sur lesquelles leur département R&D travaille.Evolution des process de fabricationIl sagit là du moyen le plus simple de faire évoluer les transistors, étant donné que faire évoluer le process permet de disposer de transistors plus performants (fréquence accrue) et plus petits (il devient alors possible den placer plus sur un CPU à coût identique). Le succès dIntel est dû en grande partie à ses process de fabrication et à ses nombreuses usines qui lui permettent de fabriquer des processeurs avec un volume et un yield qui font rêver beaucoup dacteurs de cette industrie.

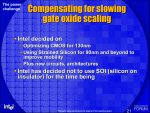

Fin de cette année ou début 2006, Intel devrait commercialiser les premiers processeurs fabriqués en 65 nm. Ce process utilisera globalement les mêmes technologies que le 90 nm actuel. Il reprendra donc le Strained Silicon qui permet daugmenter la vitesse de déplacement des électrons dans le transistor et donc de faciliter la montée en fréquence et/ou de réduire la consommation. En 65 nm le Strained Silicon en sera à sa seconde génération et permet selon Intel daugmenter de 30% les performances des transistors.

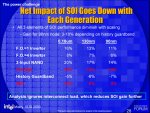

Tout en faisant lapologie de cette technologie, Intel nhésite pas à démonter celle de son concurrent, le SOI. Il permet de réduire les courants de fuite (et donc qui ne servent à rien dautre quà faire chauffer le processeur) et donc la consommation du processeur. AMD semble en être très satisfait, et la faible dissipation thermique des Athlon 64 va dans ce sens, mais selon Intel le SOI tel quutilisé par AMD ("partially depleted") na aucun intérêt puisquil ne réduit quun des nombreux types de courant de fuite, augmente significativement le coût de fabrication et voit son utilité réduite avec lévolution des process. Intel nenvisagera le SOI quen version "fully depleted", cest-à-dire avec une couche extra-fine, mais ce nest pas pour tout de suite et la décision sera prise sur base de la balance coûts/gains de cette solution dans quelques années.

En 2007, avec le process 45 nm, devrait arriver un changement important avec lutilisation dun isolant de grille de type High K et délectrodes métalliques en lieu et place de loxyde de silicium et du poly-silicon utilisés actuellement. Ce changement important réduira la capacitance de la grille (ce qui permet daugmenter la vitesse des transistors) et réduira les courants de fuite dun facteur supérieur à 100, réduisant ainsi drastiquement la consommation. De quoi fabriquer des processeurs quadri-cores à haute fréquence et qui ne consommeront pas plus de 100 Watts ?

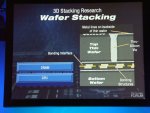

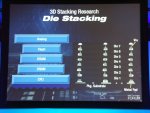

Die StackingIl ne sagit pas réellement dune nouvelle technologie étant donné quelle est utilisée depuis longtemps dans les mémoires. Le Die Stacking consiste à empiler les dies les uns sur les autres et à les connecter entre eux et/ou directement sur le socket. Il y a bien entendu des limitations physiques, tant au niveau de la réalisation de ces connexions mais également au niveau de la dissipation thermique. Empiler 4 Prescott pourrait en effet être dangereux.

Empiler des cores qui chauffent moins est envisageable, mais dans "limmédiat" il est plutôt question de dies totalement différents : par exemple un CPU, un northbridge, un contrôleur réseau et de la RAM très rapides empilés. Le gain en place serait conséquent et les coûts réduits. Si lon a du mal à envisager ce genre de chose avec les CPU desktop actuels, il en est tout autrement avec les Pentium M LV et ULV avec lesquels cette technologie prendrait tout son sens.

Reste bien entendu à mettre au point des systèmes de packaging efficaces et fiables (par exemple pour éviter décraser les dies lors du montage dun système de refroidissement), la connectique et de résoudre la problème du dégagement thermique. Intel indique pour ce dernier point que de nombreuses solutions existent et quil ne remettra pas en cause le Die Stacking.

Le CPU photoniqueUn problème de plus en plus important dans les CPU est le délai de propagation du signal dans les interconnexions. Il y a quelques générations il était considéré comme négligeable mais aujourdhui ce nest plus le cas. La vitesse des transistors a augmenté dans des proportions très importantes alors que le délai de propagation est resté plus ou moins constant ce qui est logique étant donné que avec la miniaturisation, bien quil ait une distance plus réduite à parcourir, le signal passe par des interconnexions plus fines qui ont donc une résistance plus élevée réduisant ainsi la vitesse du signal. Lun dans lautre le délai de propagation ne se réduit pas.

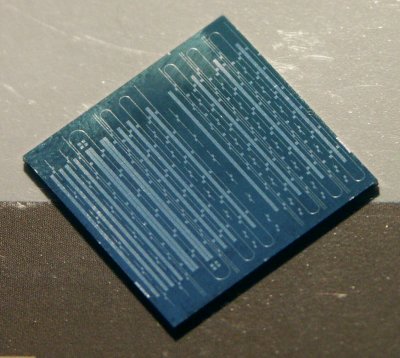

Ce die distribué par Intel contient pas moins de 8 lasers

Si un signal doit se déplacer dun bloc à un autre du CPU, il ne peut plus le faire en un cycle. Il faut placer des répétiteurs qui augmentent la consommation et la latence du signal. Il y a bien entendu des solutions via lamélioration du process de fabrication, mais ça ne devrait pas être suffisant à long terme.

La solution pourrait bien être lutilisation de la photonique sur silicium qui revient à utiliser des photons (lumière) au lieu délectrons pour la transmission des signaux. Les gains sont énormes puisque le signal peut se déplacer plus rapidement et se dégrader beaucoup moins. On pourrait ainsi imaginer à terme une connexion photonique vers le cache L2 voir même des connexions photoniques externes au CPU pour connecter 2 die entre eux et un tas dautres utilisations dans des domaines très variés.

Il sagit cependant dun défi difficile à réaliser étant donné quidéalement les éléments photoniques devraient être fabriquées de la même manière que les transistors. Mais manque de chance, la photonique a besoin dune source émettrice de lumière : le laser. Or, ce lui-ci, pour fonctionner doit disposer dun matériau qui émet facilement et en masse des photons, ce qui nest absolument pas le cas du silicium.

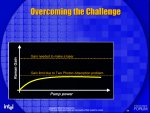

Sans issue ? Pas pour Intel qui annonce avoir fabriqué le premier laser continu sur silicium grâce à leffet Raman, effet quantique qui permet notamment damplifier les signaux optiques. Une pompe amène un flux de photons et lamplificateur Raman se charge damplifier le signal dune manière très efficace, leffet Raman étant 10.000 fois plus fort dans le silicium que dans le fibre optique. Ca fonctionne alors ? Pas encore car un autre problème subsiste et empêche le laser dêtre réellement utilisable. En temps normal, le silicium est transparent pour la lumière infrarouge mais pendant lamplification le nombre de photons augmente suffisamment pour que 2 dentre eux heurtent régulièrement un atome de silicium en même temps, dégageant un électron qui va alors absorber de nombreux photons et ainsi réduire a néant leffet Raman. Intel indique cependant quil sagit dun premier pas et que les différents problèmes qui subsistent devraient être résolus dans les années à venir.

Le CMOS est toujours bien vivantAvec les futurs process de fabrication CMOS, le Die Stacking et la photonique sur silicium Intel a de quoi voir venir. Il y a là en effet tout ce qui est nécessaire pour continuer à fabriquer des CPU toujours plus évolués et performants pendant au moins 2 décennies !

Intel nhésite dailleurs pas à brosser un rapide portrait du CPU de 2015 : il sera fortement optimisé pour le multi-threading, intégrera plusieurs cores et de plus en plus dunités spécialisées un peu comme commencera à le faire IBM lannée prochaine avec le Cell.

Sommaire

Vos réactions

Contenus relatifs

- [+] 09/12: Guide : Les PC HardWare.fr !

- [+] 14/11: Qualcomm dit non à Broadcom

- [+] 13/11: Thermaltake lance une chaise venti...

- [+] 11/09: Microsoft confirme des problèmes de...

- [+] 30/08: PCI Express 5.0 pour 2019, débit do...

- [+] 01/08: Les taux de retour des composants (...

- [+] 11/07: Le minage consommerait plus que Par...

- [+] 04/07: ASUS XG-C100C, le 10GBASE-T à 120

- [+] 26/06: Computex et le PC : changement et c...

- [+] 24/03: Corsair lance ses PC One avec deux ...