AMD 760MP & Athlon MP

Publié le 18/07/2001 par Marc Prieur et Samuel Aurensan

L´Athlon MP

Si les Athlon actuels fonctionnent parfaitement en bi processeur, AMD sest tout de même donné la peine de sortir de nouveaux Athlon dédiés au bi processeur, les Athlon MP. En fait, ces processeurs sont tout simplement basés sur le nouveau core Athlon, le Palomino. Les innovations par rapport à lactuel Thunderbird sont multiples.

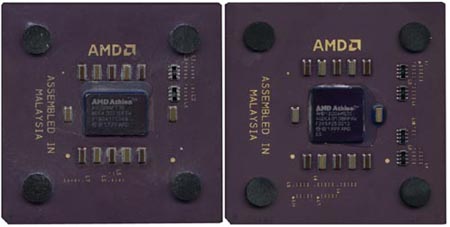

Si les Athlon actuels fonctionnent parfaitement en bi processeur, AMD sest tout de même donné la peine de sortir de nouveaux Athlon dédiés au bi processeur, les Athlon MP. En fait, ces processeurs sont tout simplement basés sur le nouveau core Athlon, le Palomino. Les innovations par rapport à lactuel Thunderbird sont multiples.Première chose, son design a été optimisé afin quil soit moins gourmand électriquement. Ainsi, à fréquence égale un Athlon Palomino sera 20% moins gourmand quun Ahtlon Thunderbird, ce qui se ressentira bien entendu sur la chaleur dégagée par le CPU. Du fait de ses optimisations, le design du core à changé, doù cette rotation à 90 degrés que vous pouvez observer sur les photos. En fait, la taille du core tout comme le nombre de transistors reste a peu près équivalent : 120 mm² et 37 Millions de transistors pour le Thunderbird, contre 128mm² et 37.5 Millions de transistors pour le Palomino. Au passage, sachez que les Palomino intègrent désormais une sonde de température, sonde qui nest malheureusement pas encore reconnue par les cartes mères que lon trouve actuellement sur le marché.

Dautres innovations sont censées influencer les performances mêmes de lAthlon MP. Cest notamment le cas du SSE, qui est désormais complètement supporté par ce processeur via le jeu dinstruction 3DNow! Professional. Jusqualors, les Athlon disposaient, en sus du MMX et du 3DNow !, des 19 instructions SSE qui venaient compléter le MMX. LAthlon MP supporte désormais les 52 instructions SIMD FP du SSE. Au passage, sachez que le SSE2, introduit par Intel avec le Pentium 4, devrait être supporté par AMD en 2002 avec les processeurs de la famille Hammer (ex-K8).

L´Athlon ´Thunderbird´ à gauche, l´AthlonMP Palomino à droite

- Passage de 32 à 40 entrées pour le L1 DTLB

- Architecture exclusive (pas de doublon) pour les L2 ITLB et L2 DTLB

- Possibilité décrire dans les TLB avant la fin de linstruction

Si la mémoire cache ne change pas à proprement parler (128 Ko de cache et L1 et 256 Ko de cache L2 gérés de manière exclusive), sa gestion est améliorée. En effet, le Palomino dispose dun dispositif de pré-chargement des données automatique en cache L2. Pour faire simple, il analyse les accès mémoire afin dessayer de deviner les données dont aura prochainement besoin le processeur afin de les charger en avance. Du coup, on gagne quelques précieux cycles dhorloges lorsque ça fonctionne.

Sommaire

Vos réactions

Contenus relatifs

- [+] 15/01: NZXT lance une carte mère ! (MAJ)

- [+] 20/11: Intel 100% UEFI 0% BIOS d'ici 2020

- [+] 26/10: La norme PCI Express 4.0 finalisée

- [+] 18/10: Le Z270 aurait pu supporter Coffee ...

- [+] 09/10: Coffee Lake : avalanche de cartes m...

- [+] 04/10: ASUS se lance dans le mini-ITX AM4

- [+] 04/10: Le RAID NVMe disponible sur X399 en...

- [+] 02/10: La spécification de l'USB 3.2 a été...

- [+] 19/09: Z370 incompatible avec les Core de ...

- [+] 23/08: 19 slots PCIe sur une carte ASUS !