Les contenus liés au tag HMC

Afficher sous forme de : Titre | FluxUn consortium pour l'Hybrid Memory Cube

IDF: Objectif 2W pour 100 Gflops en 2018

Micron en charge de la mémoire des Knights Landing

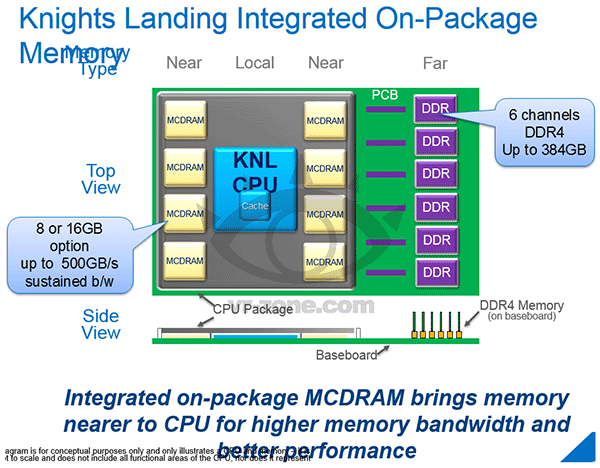

Nous vous en parlions en novembre dernier, la prochaine génération de Xeon Phi (Knights Landing) prévue pour la mi-2015 intégrera jusqu'à 16 Go de mémoire embarquée ultra-rapide délivrant une bande passante de l'ordre de 500 Go /s.

On apprend aujourd'hui que cette mémoire sera produite par Micron, qui l'a développée en collaboration avec Intel en prenant pour base l'Hybrid Memory Cube dont on parle depuis quelques années déjà. Les puces se trouveront sur le même packaging que les Xeon Phi, et seront reliées à ce dernier par une interface à très haute vitesse.

Dans son communiqué Micron indique que cette mémoire a une bande passante 5x supérieure à la DDR4 tout en prenant 50% de place en moins et avec un ratio bande passante/consommation multiplié par 3.

Pour rappel ces nouveaux Xeon Phi gravés en 14nm devraient gérer l'AVX-512, la DDR4, le PCIe Gen3 et seront disponibles en version Socket comme en carte fille PCIe. Un Xeon Phi pourra intégrer jusqu'à 72 curs de type Silvermont associés par paire, gérant chacun deux grosses unités vectorielles prenant en charge le traitement des instructions AVX-512 et partageant un cache L2 de 1 Mo. En sus de la mémoire embarquée, ils géreront six canaux de DDR4 permettant d'adresser 384 Go de mémoire supplémentaire.

Hybrid Memory Cube Gen2 en développement

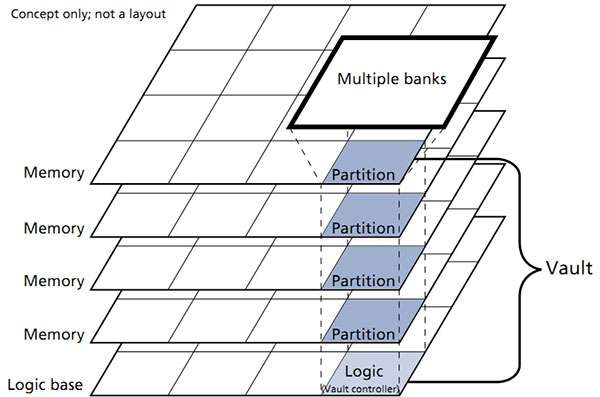

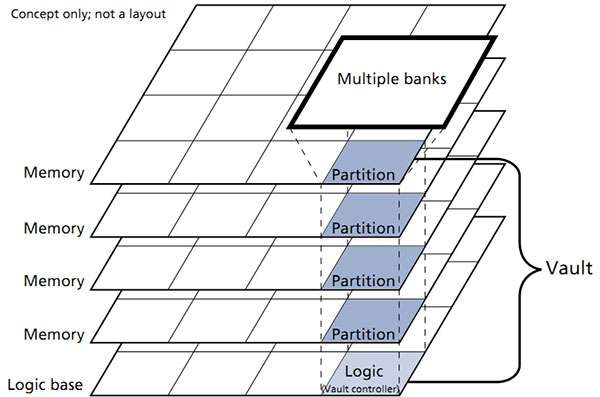

L'Hybrid Memory Cube Consortium (fondé par Micron et Samsung en 2011, rejoint ensuite par Hynix et 120 sociétés donc ARM, IBM, Microsoft et Xilinx) vient de publier un communiqué indiquant le développement d'une seconde génération de cette mémoire. Pour rappel, le concept de l'HMC est de superposer plusieurs dies de mémoire DRAM par-dessus une die de logique, le tout étant relié par des TSV (Through Silicon Vias, des fils qui traversent les dies).

Nous avions parlé un peu plus en détail de la première version de cette spécification en septembre dernier, nous vous renvoyons vers cet article si vous souhaitez plus de détails.

La nouvelle spécification est encore au statut de « draft » (en préversion) et n'a été pour l'instant partagé qu'avec les membres du consortium dans le but d'être finalisé en mai 2014. La nouvelle version de la spec évoque des augmentations de bande passante, en doublant à 480 Go/s la bande passante totale des puces pour le modèle 4 liens, et 480 Go/s également pour le modèle huit liens (contre 320 dans la spec version 1.0).

Si Samsung et Hynix sont impliqués dans le développement du standard, Micron reste pour l'instant le seul constructeur à avoir produit des échantillons commerciaux.

1ers échantillons d'Hybrid Memory Cube !

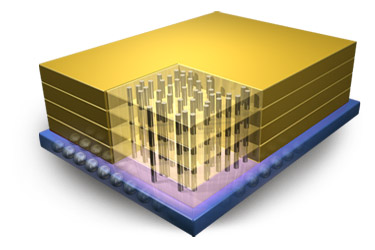

Micron vient d'annoncer par un communiqué de presse la disponibilité de ses tous premiers échantillons de test d'Hybrid Memory Cube. Pour rappel, l'Hybrid Memory Cube est un concept relativement simple qui superpose plusieurs dies de mémoire DRAM qui sont reliés les uns aux autres par des TSV (des fils qui passent au travers des différents dies), et reliés en dessous à une couche logique qui contient les contrôleurs.

Un consortium qui regroupe Micron et d'autres sociétés (notamment ARM, HP, Hynix, IBM et Samsung, mais bizarrement pas Intel qui pourtant avait effectué des démonstrations de la technologie) a publié une spécification pour ce nouveau type de mémoire en avril, annonçant des débits très élevés allant de 160 à 240 Go/s (et même 320 Go/s pour des modèles plus complexes). Vous pouvez retrouver plus de détails sur le fonctionnement de l'HMC dans cette actualité.

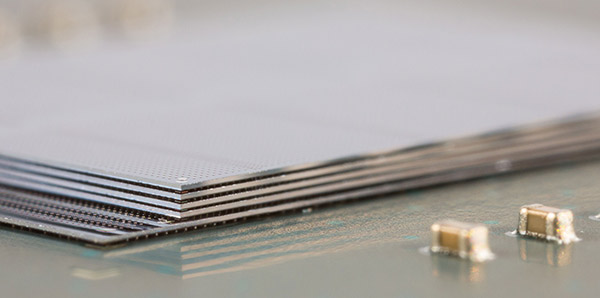

Micron fournit pour l'occasion cette magnifique photo ou l'on voit clairement le concept

Micron avait annoncé il y a peu son intention de lancer la production en 2014 et de livrer avant la fin de l'année ses premiers échantillons. C'est donc chose faite et l'on a droit en prime à quelques détails techniques. Ce premier échantillon est un modèle 2 Go composé de quatre dies de mémoire DRAM de 4 Gb. Avec quatre liens, cette puce offre 160 Go/s de bande passante mémoire comme attendu. Ces premiers échantillons permettront avant tout le développement pour les partenaires, l'HMC déportant une grande partie de la logique des contrôleurs mémoires directement dans sa couche logique. Micron annonce qu'il proposera début 2014 des échantillons 4 Go et que les deux modèles seront bel et bien en production en 2014, sans s'avancer plus précisément. Les curieux pourront retrouver ces modèles, annoncés en packaging BGA et FBGA sur cette page du site de la société.

L'Hybrid Memory Cube en production en 2014

Nous vous avions parlé en 2011 du concept de l'Hybrid Memory Cube. Sur le papier il s'agit d'un concept simple, superposer une couche logique de contrôleurs mémoires avec de multiples dies de mémoire DRAM reliés les uns aux autres par des TSV (Through Silicon Vias, littéralement des fils qui passent au travers des différents dies, à l'opposée de la solution "classique" ou l'on fait passer les fils par le côté).

Chaque colonne sur le schéma représente un "vault" qui dispose en bas dans la couche logique de son propre contrôleur mémoire indépendant. L'avantage du système est d'être capable d'atteindre des bandes passantes très élevées, on parlait déjà en 2011 de 128 Go/s sur une seule puce !

Sur cet autre schéma, on peut voir le principe un peu plus en détail avec une puce qui superpose neuf dies (8 mémoires, un logique). On retrouve ici 16 vaults, chaque contrôleur est relié à un switch puis à quatre liens point à point vers l'extérieur de la puce. Ces nombres étant bien entendu modulables. Notez également que les cubes sont chainables entre eux.

Micron et d'autres sociétés (notamment ARM, HP, Hynix, IBM et Samsung) se sont alliés pour mettre en place un consortium dans le but de développer un standard commun. On notera avec un étonnement certain l'absence d'Intel dans ce consortium, alors que la société avait pourtant effectué les démonstrations lors de l'IDF 2011. La spécification (PDF) a été publiée en avril avec des débits très prometteurs allant de 160 à 240 Go/s pour les modèles à quatre liens (en fonction de la vitesse individuelle des liens), et 320 Go/s pour le modèle huit liens.

Micron avait indiqué en 2011 que c'est IBM qui produirait dans son process 32nm HKMG. Aujourd'hui, dans un communiqué qui parle de l'intérêt de l'intégration avec des FPGA, Micron s'engage un peu plus sur les dates en annonçant la livraison d'échantillons avant la fin de l'année, et surtout une production en volume pour 2014. On ne sait pas s'il s'agira toujours d'un process 32 HKMG. En déportant les contrôleurs mémoires directement dans les puces mémoires, l'Hybrid Memory Cube propose en plus d'un bond net de bande passante la possibilité de repenser les sous systèmes mémoires des processeurs. Reste à voir dans quel cadre elle pourra être utilisée. Le consortium indique viser très clairement les CPU et les GPU. Auprès de ces puces, l'HMC jouerait alors un rôle hybride à mi chemin entre ce que propose l'eDRAM et la mémoire traditionnelle.

IBM va produire l'Hybrid Memory Cube

Micron vient d'annoncer qu'il allait faire fabriquer par IBM sa mémoire Hybrid Memory Cube. La gravure se fera dans l'usine IBM de East Fishkill située dans l'état de New-York avec un process 32nm HKGM. L'Hybrid Memory Cube est composée d'une couche logique qui est interconnectée à empilement de plusieurs die mémoire via le TSV (Through Silicon Via).

Cette technologie permet de relier plusieurs die entre eux via des connexions verticales qui passent donc au travers même des die. Cette verticalité permet de réduire drastiquement la longueur des connexions, ce qui permet entre autre d'améliorer la vitesse, d'abaisser la consommation et de réduire la taille du packaging.

Les débits atteints par une mémoire HMC sont très élevés puisqu'une puce de 512 Mo atteindrait les 128 Go /s soit 10 fois la bande passante de la DDR3-1600. Avec 8 watts la consommation rapportée à la bande passante est également en baisse, mais elle est en hausse si on la rapporte à la capacité.

Pour le moment la HMC devrait être assez chère et réservée à des applications industrielles. A terme on peut penser que ce type de mémoire pourrait être utilisé dans des produits plus grand public, afin par exemple de servir de mémoire locale pour un APU.