Les derniers contenus liés aux tags IDF et HMC

IDF: Roadmap mémoire Micron

Publié le 21/08/2015 à 04:51 par Guillaume Louel

Le partenaire d'Intel sur la mémoire 3D XPoint était présent sur l'IDF avec un stand ou l'on pouvait apercevoir un wafer de NAND 16nm, ainsi qu'un module 3D NAND de 256 Gbits.

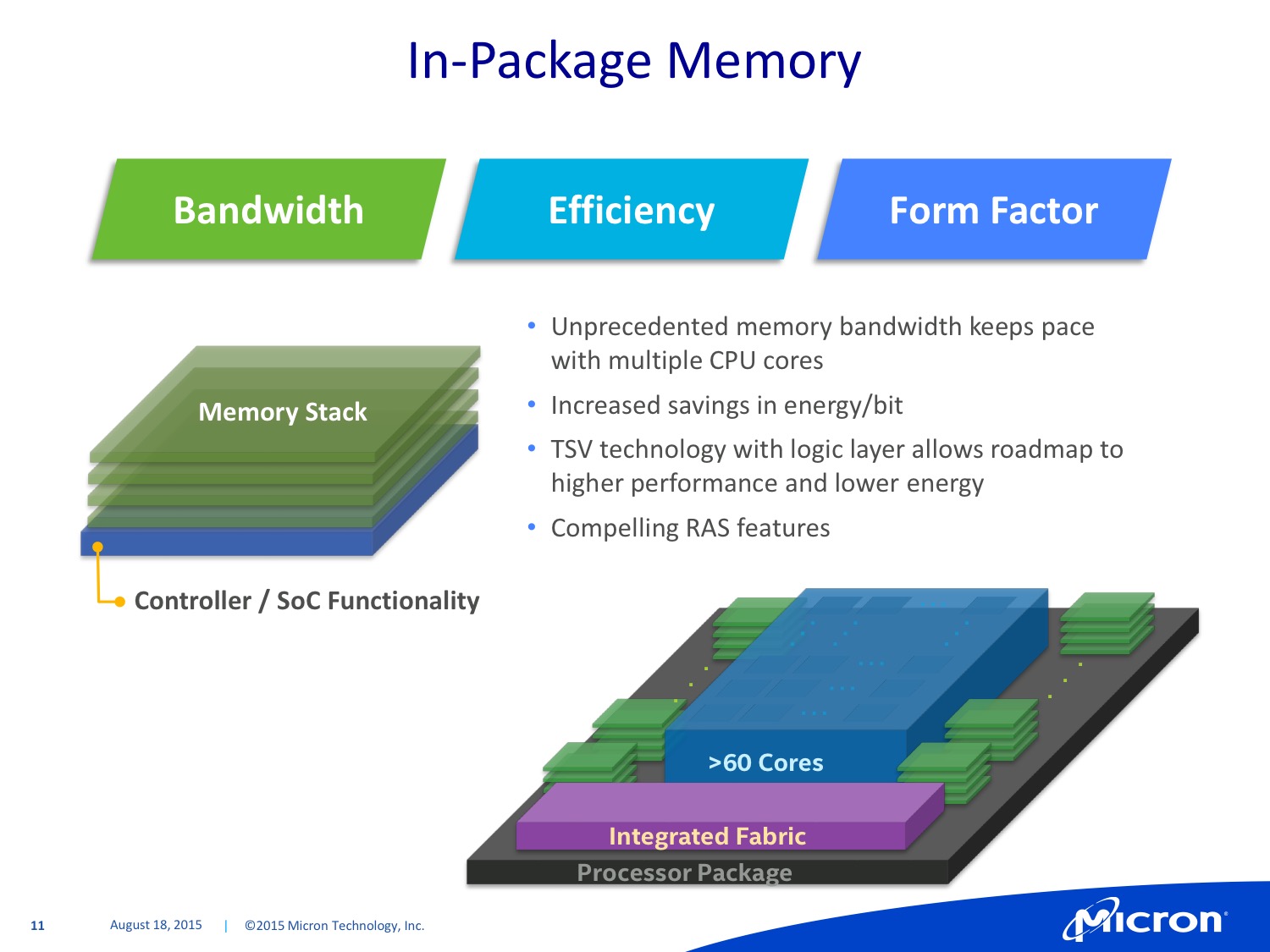

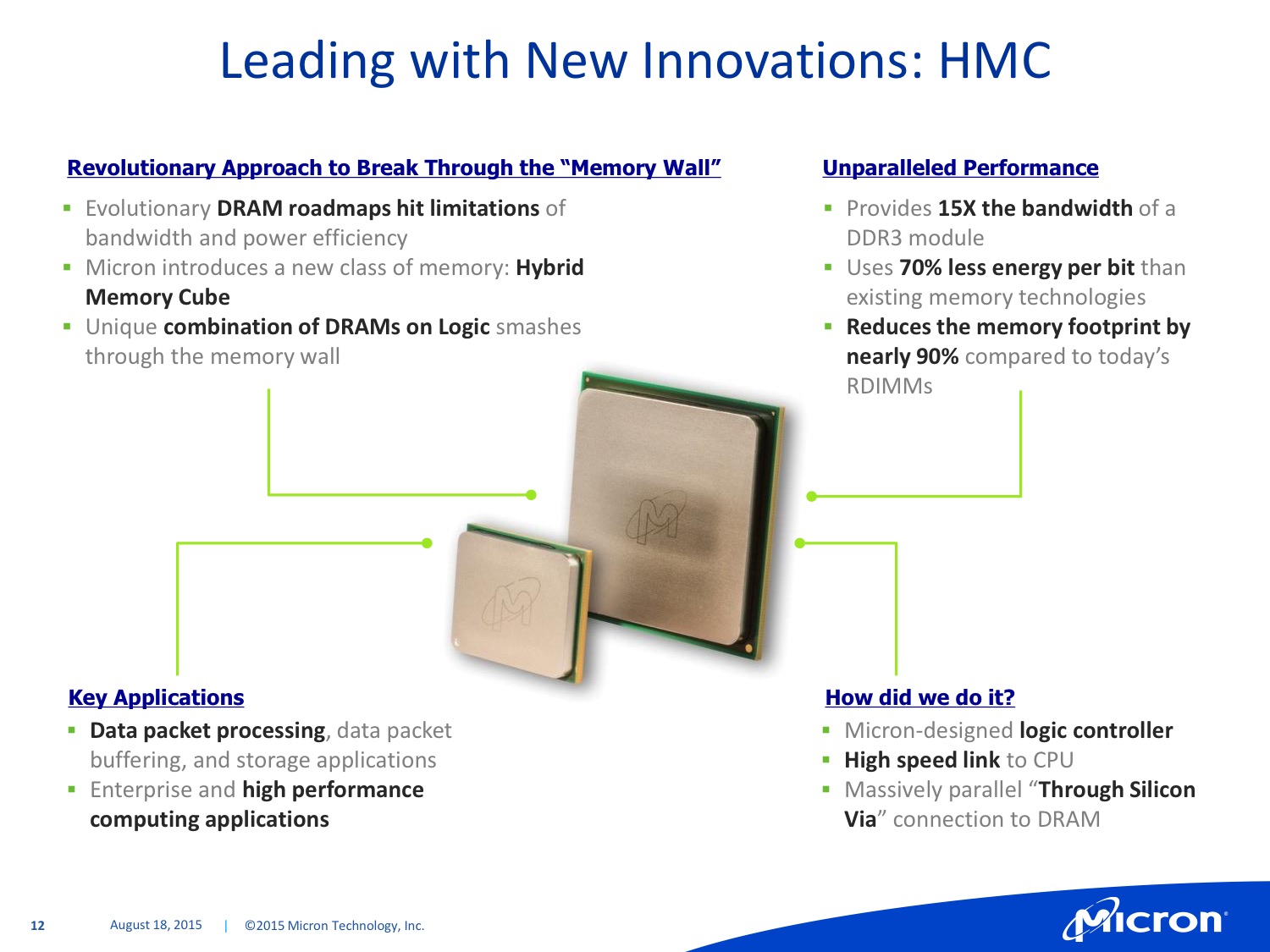

La société a également effectué une présentation ou elle a évoqué ses technologies mémoires. Le constructeur continue de travailler sur l'Hybrid Memory Cube (HMC), une technologie qui supperpose des dies de mémoires avec une couche de contrôleurs logiques. La troisième génération est en cours de développement même si l'on ne sait pas encore ce qu'elle apportera.

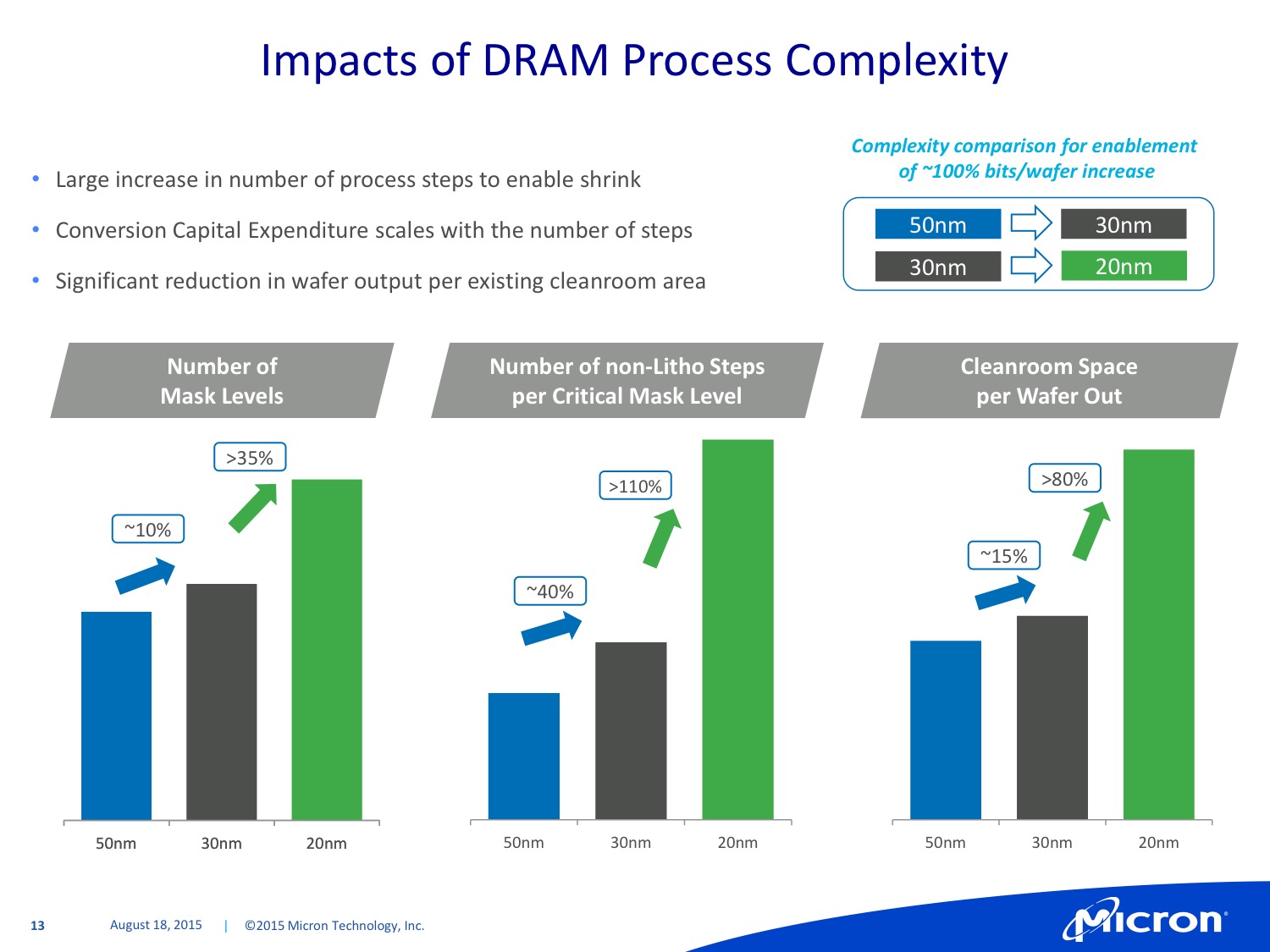

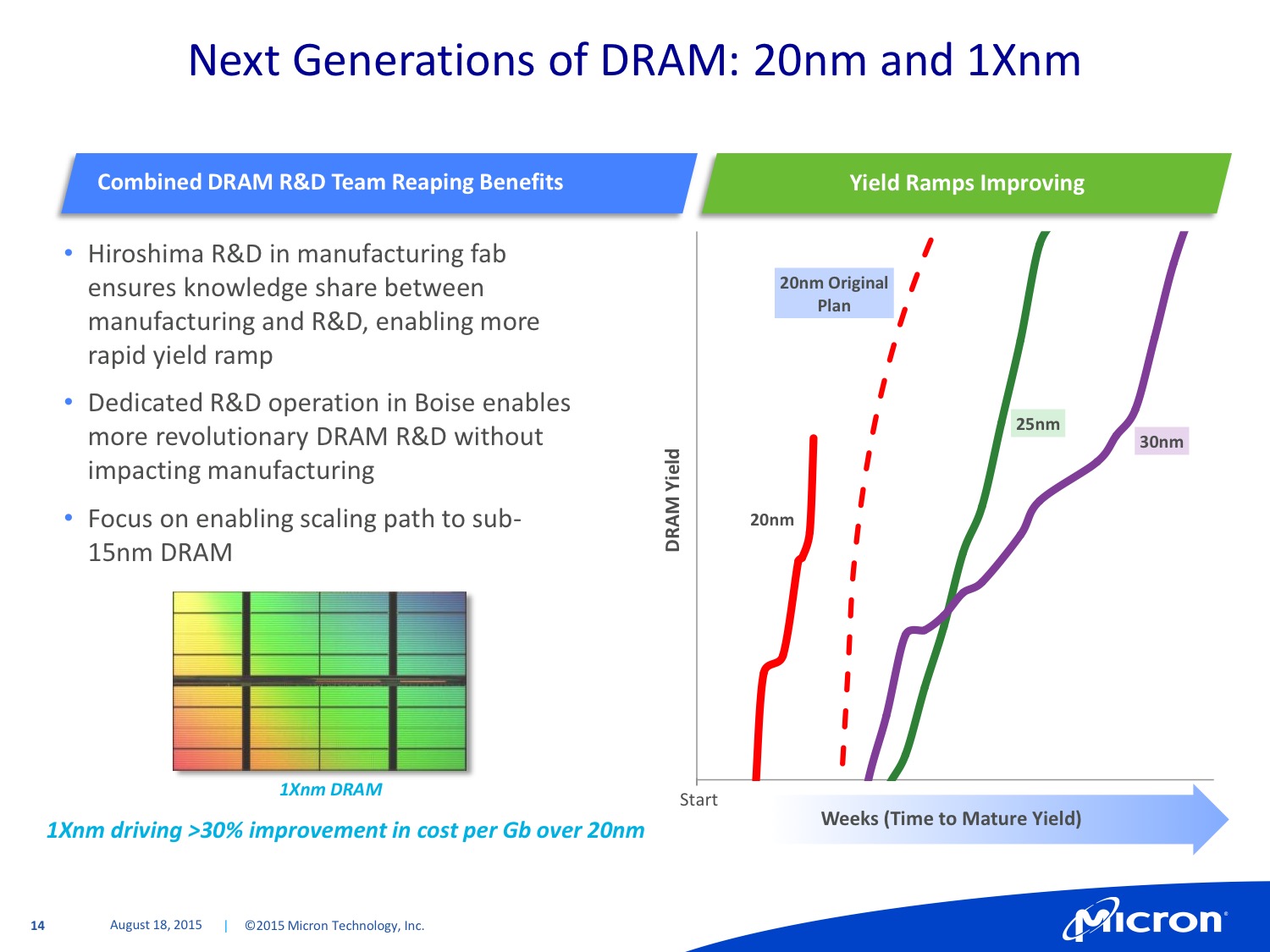

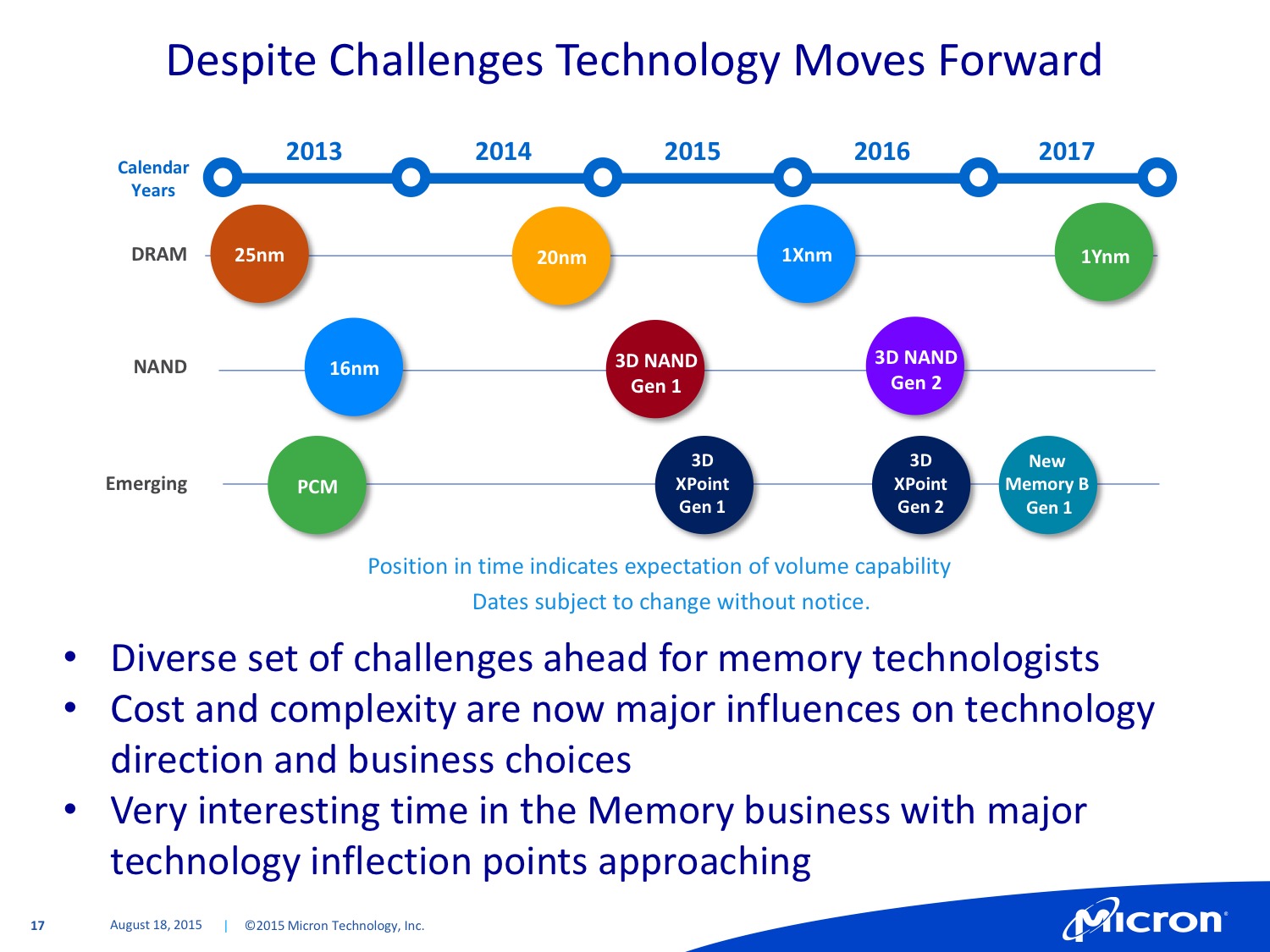

Micron est également revenu sur la complexité de la fabrication de la mémoire DRAM a 20nm et au dela. L'augmentation des coûts via les masques et les opérations rend de plus en plus difficile chaque passage à un nouveau node. Malgré tout le fabricant s'est felicité de ses yields atteint en 20nm et a indiqué travailler sur le 15nm et au delà.

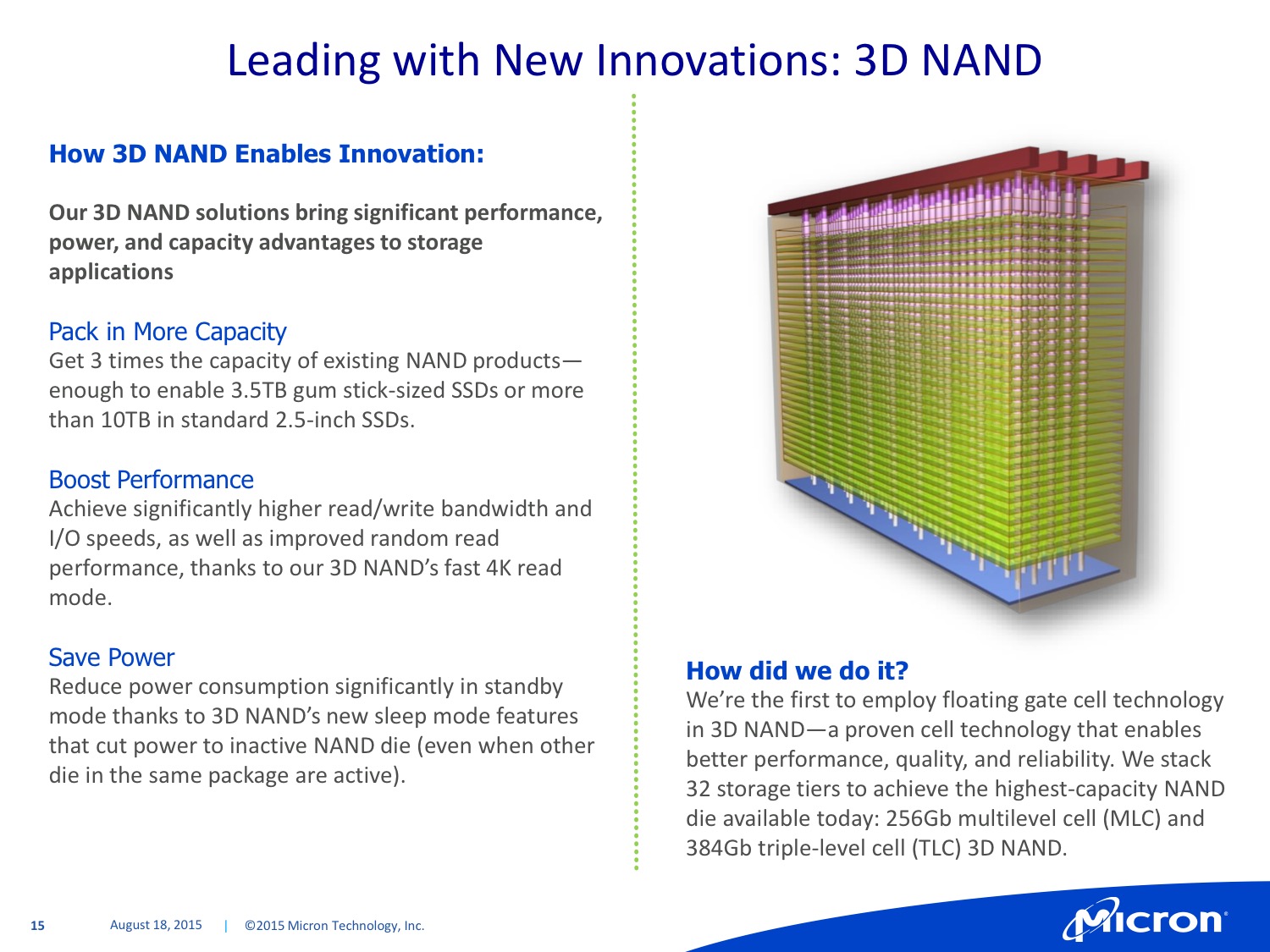

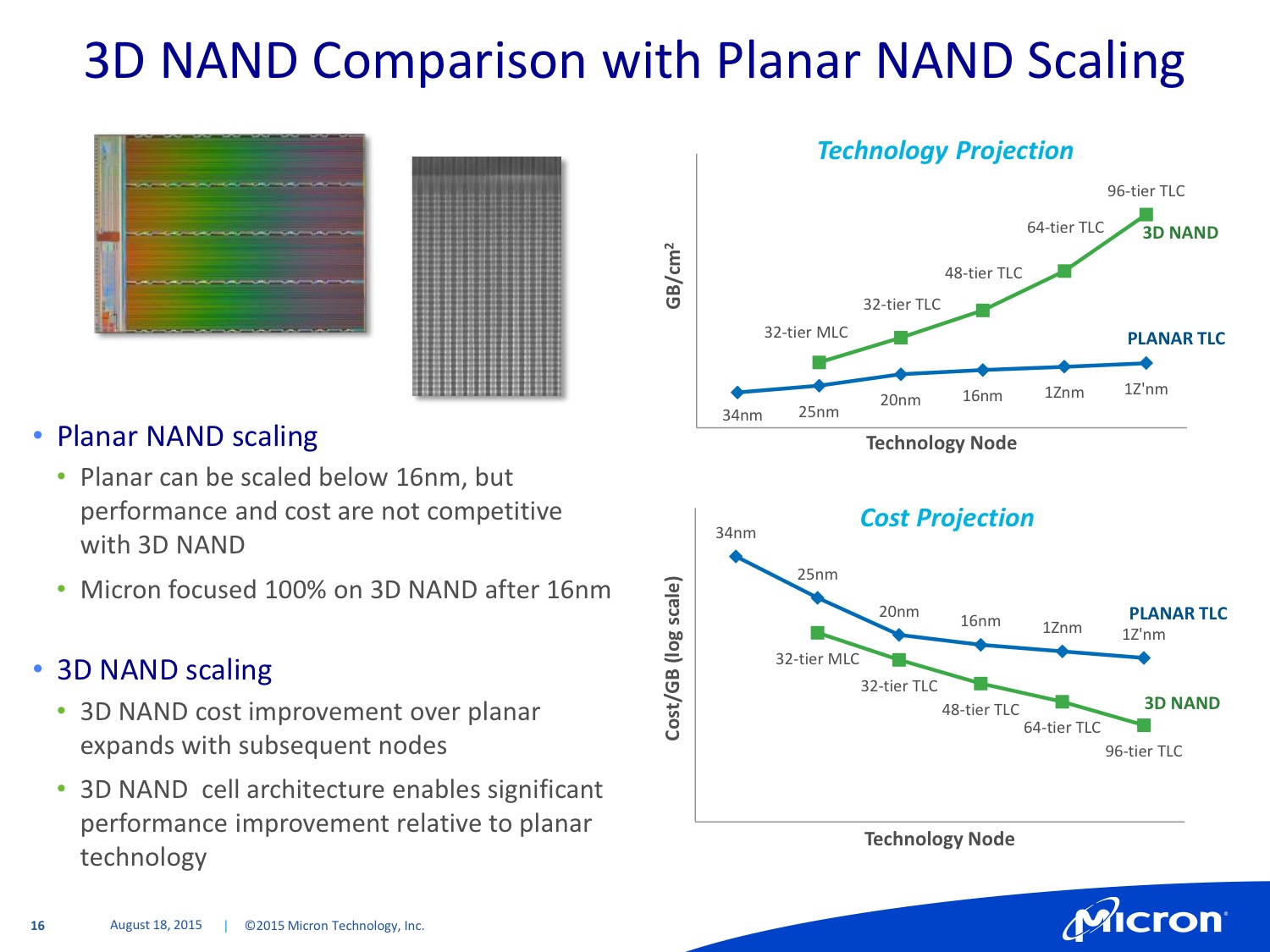

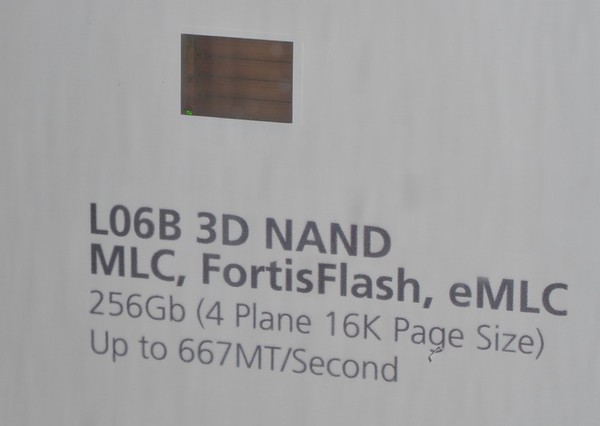

Côté NAND, Micron a confirmé que le 16nm serait son dernier node « traditionnel » et qu'il passait au delà à une gamme 100% 3D NAND. Cette variante de la NAND permet pour rappel de construire les cellules verticalement pour les empiler en augmentant la densité. Un avantage important qui permet d'utiliser des process plus anciens, et mieux maitrisés, autour de 50nm pour la première génération de Micron. La seconde génération de 3D NAND apparaitra en 2016.

3D XPoint a été peu évoqué, si ce n'est sur le fait qu'il y aura une seconde génération de cette mémoire en 2016. On notera que Micron parle toujours sur ses roadmaps d'une seconde nouvelle mémoire qui arriverait en 2017. Une variante de STTRAM (Spin Transfer Torque RAM) semble être l'une des possibilités, il faudra attendre un peu avant d'en savoir plus !

IDF: Objectif 2W pour 100 Gflops en 2018

Publié le 15/09/2011 à 22:08 par Damien Triolet

Bien que très énergisé par le béret de Mooly Eden, c'est bien d'une réduction drastique de la consommation dont nous a parlé Justin Rattner, Chief Technology Officer chez Intel, lors de la keynote de clôture de l'IDF, traditionnellement tournée vers le futur.

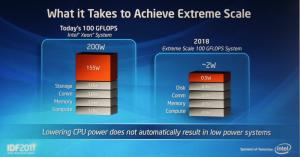

Pour pouvoir assurer l'évolution de ses performances et de ses produits, Intel s'est ainsi fixé plusieurs objectifs à long terme : pouvoir proposer des systèmes d'une puissance de 100 Gflops dans une enveloppe thermique de 2W d'ici à 2018, contre 200W pour un système Xeon équivalent actuel, et des supercalculateurs capables d'atteindre l'exaflops sans dépasser les 20 megawatts.

Pour atteindre ces objectifs, l'évolution des procédés de fabrication restera bien entendu primordiale, tout comme celle de l'architecture des CPUs. Intel indique cependant qu'il faudra s'attaquer au problème de la consommation sur de nombreux fronts : protocoles de communication, stockage, mémoire

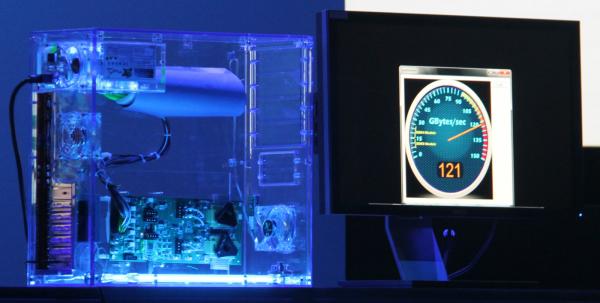

Intel a ainsi présenté un prototype de l'Hybrid Memory Cube développé en collaboration avec Micron et qui consiste à profiter du die stacking pour augmenter la densité de la mémoire mais également son débit. Une concentration qui permet d'améliorer le rendement énergétique d'un facteur 7 selon Intel.

Le prototype présenté consiste en une première couche qui contient la logique (un CPU simplifié probablement) sur laquelle sont empilées 4 couches de DRAM de 1 Gbits, soit 512 Mo au total. Un ensemble qui peut fournir une bande passante record de 128 Go/s, largement supérieure à ce dont sont capables les modules mémoire actuels. A terme, le but sera bien entendu d'empiler ainsi la mémoire sur les CPUs manycores pour profiter d'un accès plus rapide, mais également nettement moins consommateur d'énergie.

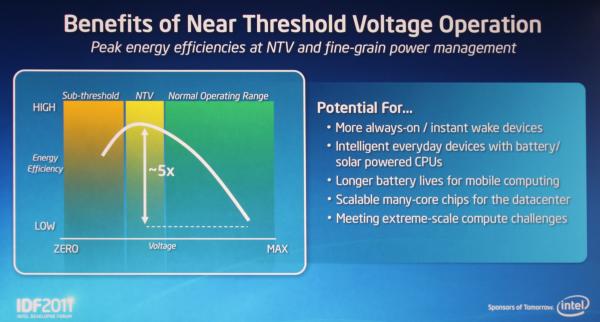

Un autre point sur lequel Intel travaille consiste à pouvoir abaisser la tension du CPU jusqu'au seuil du transistor. Habituellement, la tension est nettement plus importante, dans le but d'obtenir des performances élevées tant au niveau des transistors que de la transmission du signal. Si cette nouvelle approche pourrait permettre de laisser éveillés en permanence certains processeurs grâce à une plage de fonctionnement étendue, pouvoir se rapprocher des limites inverses du transistor pourrait paradoxalement favoriser la mise en place de systèmes très performants.

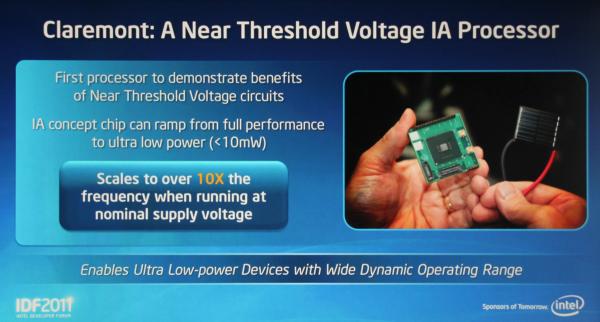

Pour travailler sur ce projet, Intel a mis au point un prototype de CPU, nom de code Claremont, basé sur un core Pentium qui peut abaisser sa consommation jusqu'à moins de 10 mW, de quoi pouvoir être alimenté par une petite cellule photovoltaïque. Certes dans ce mode la fréquence et donc les performances du CPU sont fortement réduites, mais le tout reste suffisant pour qu'un système Windows reste fonctionnel.

Ce CPU était en démonstration lors de différentes keynotes durant l'IDF, accompagné d'une ancienne carte-mère Pentium qui était par contre alimentée d'une manière classique. Pour faire passer la totalité de la plateforme à un niveau de consommation énergétique aussi faible, il y a encore du travail pour les ingénieurs d'Intel !