Les derniers contenus liés aux tags HMC et Knights Landing

HMC, DDR5 et 3D XPoint pour Micron

Micron en charge de la mémoire des Knights Landing

HMC, DDR5 et 3D XPoint pour Micron

Micron a également pris la parole pendant la première matinée de Hot Chips, comme nous le rapportent une fois de plus nos confrères de ComputerBase . Ces derniers qualifient d'une honnêteté rafraîchissante la présentation de Micron, ne cherchant pas forcément à annoncer des chiffres extravagants. La société aurait même regretté, si l'on en croit nos confrères, que son partenaire Intel ait annoncé beaucoup trop tôt la mémoire 3D XPoint !

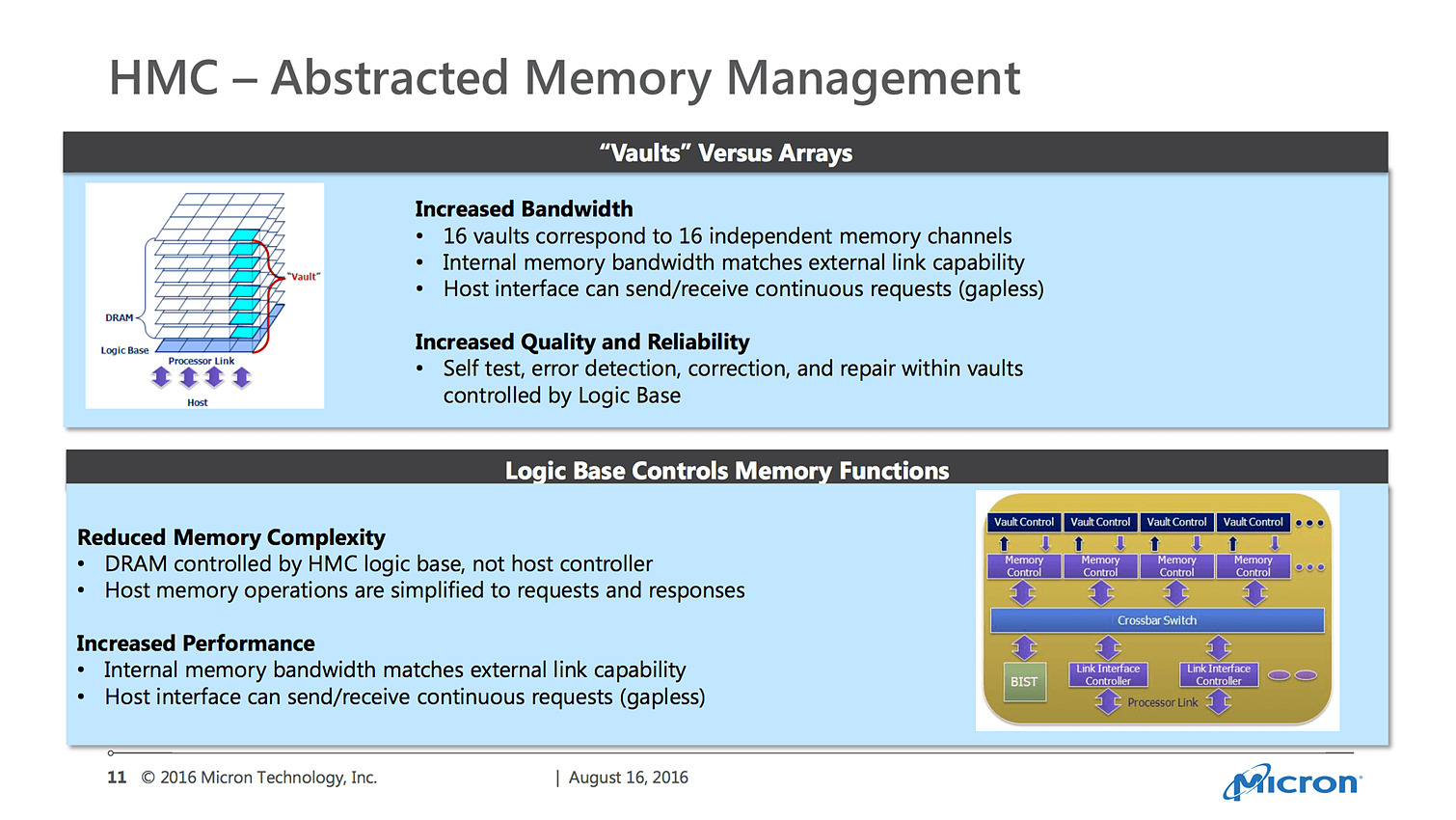

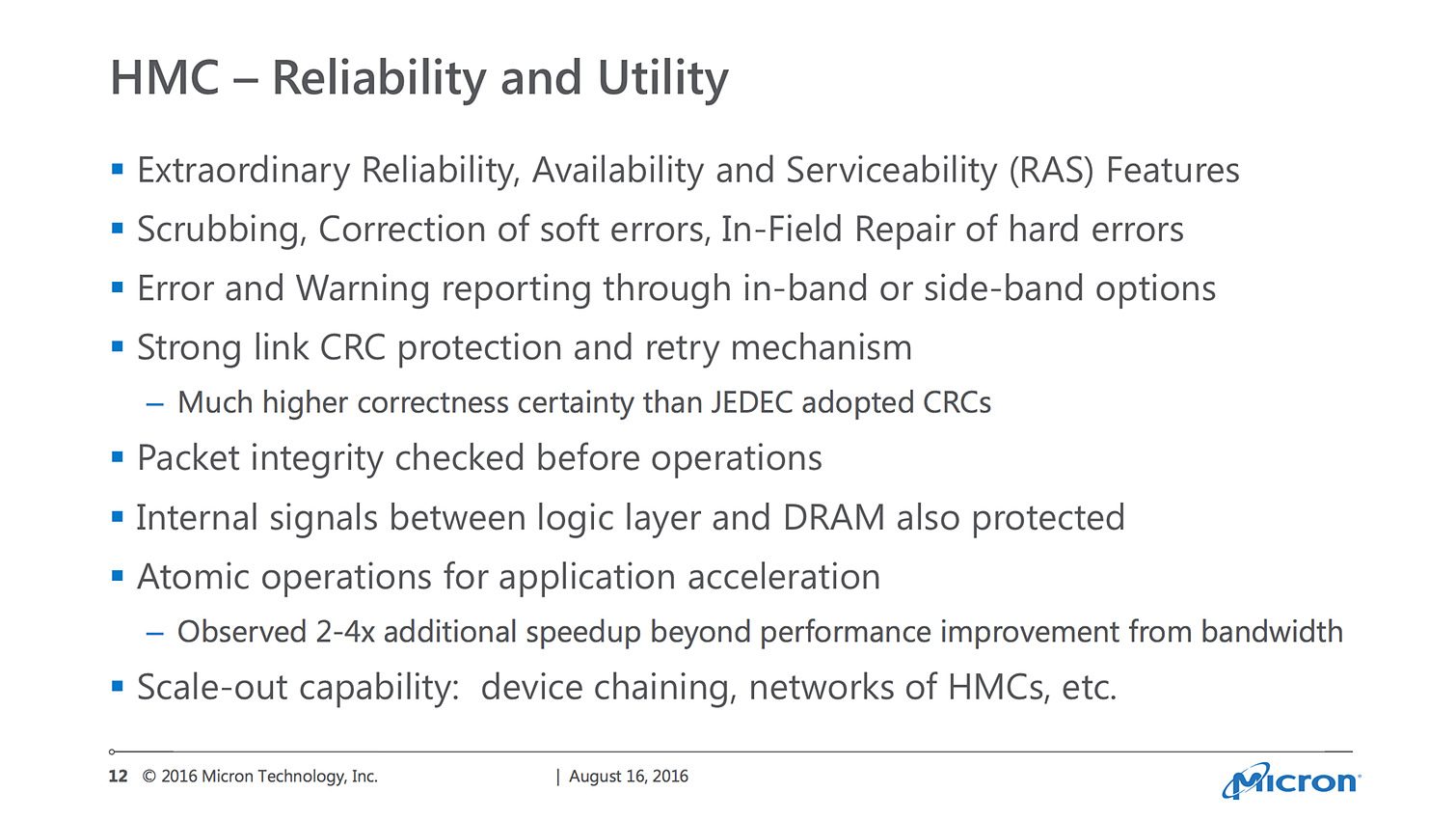

Dans le détail, Micron n'aura pas pu s'empêcher tout de même de qualifier la HBM de "mauvaise copie" de sa propre technologie Hybrid Memory Cube, plus complexe, coûteuse, et surtout assez peu disponible (elle devrait être présente sur le prochain Xeon Phi d'Intel, Knights Landing). Micron estime que la HMC dispose de nombreux avantages pour le marché du HPC, avec par exemple un meilleur algorithme de CRC que celui utilisé par le JEDEC pour la HBM.

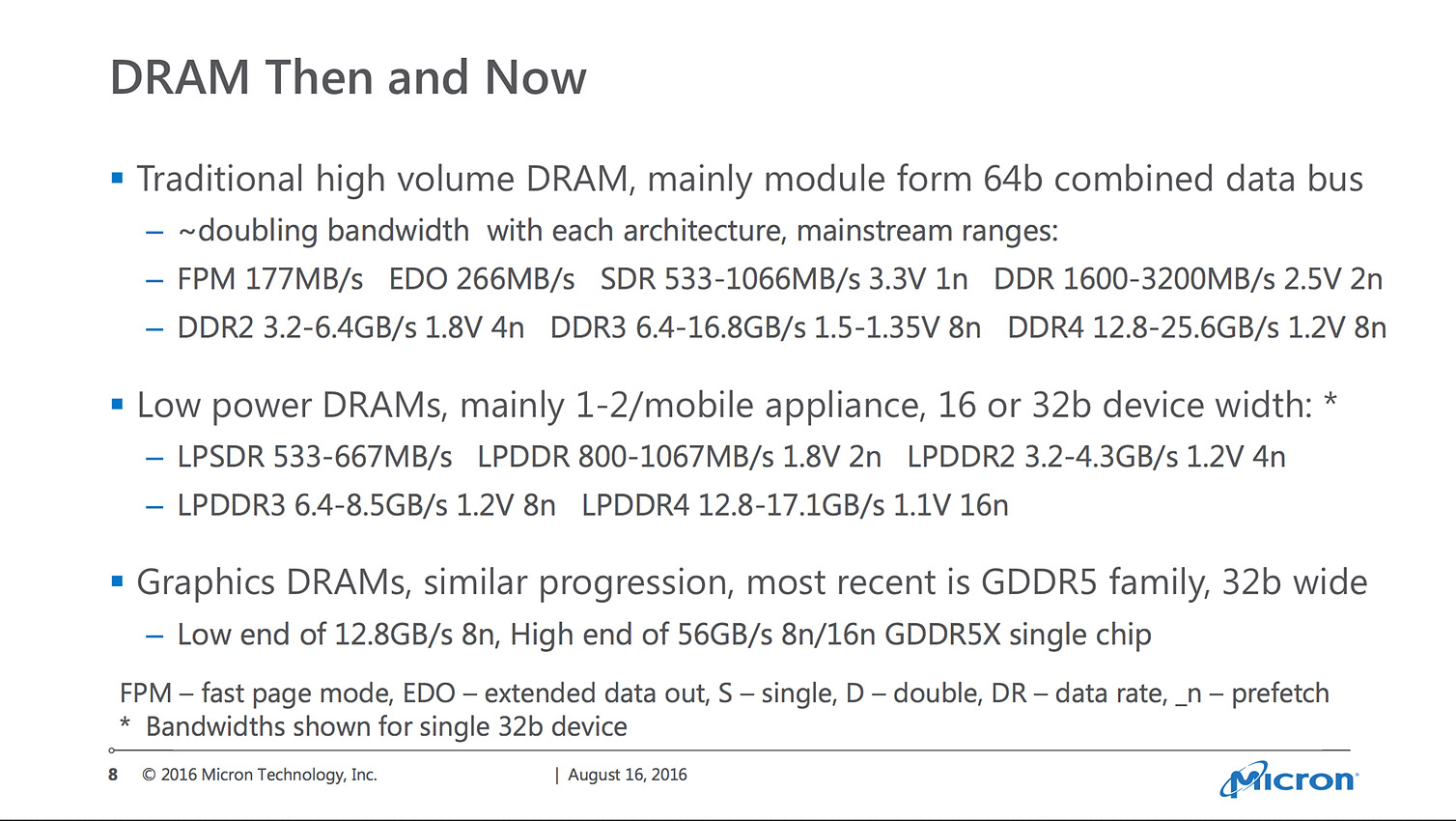

Micron aura également évoqué la DDR5 qui aura pour objectif de doubler la bande passante par rapport à la DDR4. Micron estime produire ses premiers échantillons courant 2018, avec une production en volume possiblement en 2019, mais plus probablement pour 2020.

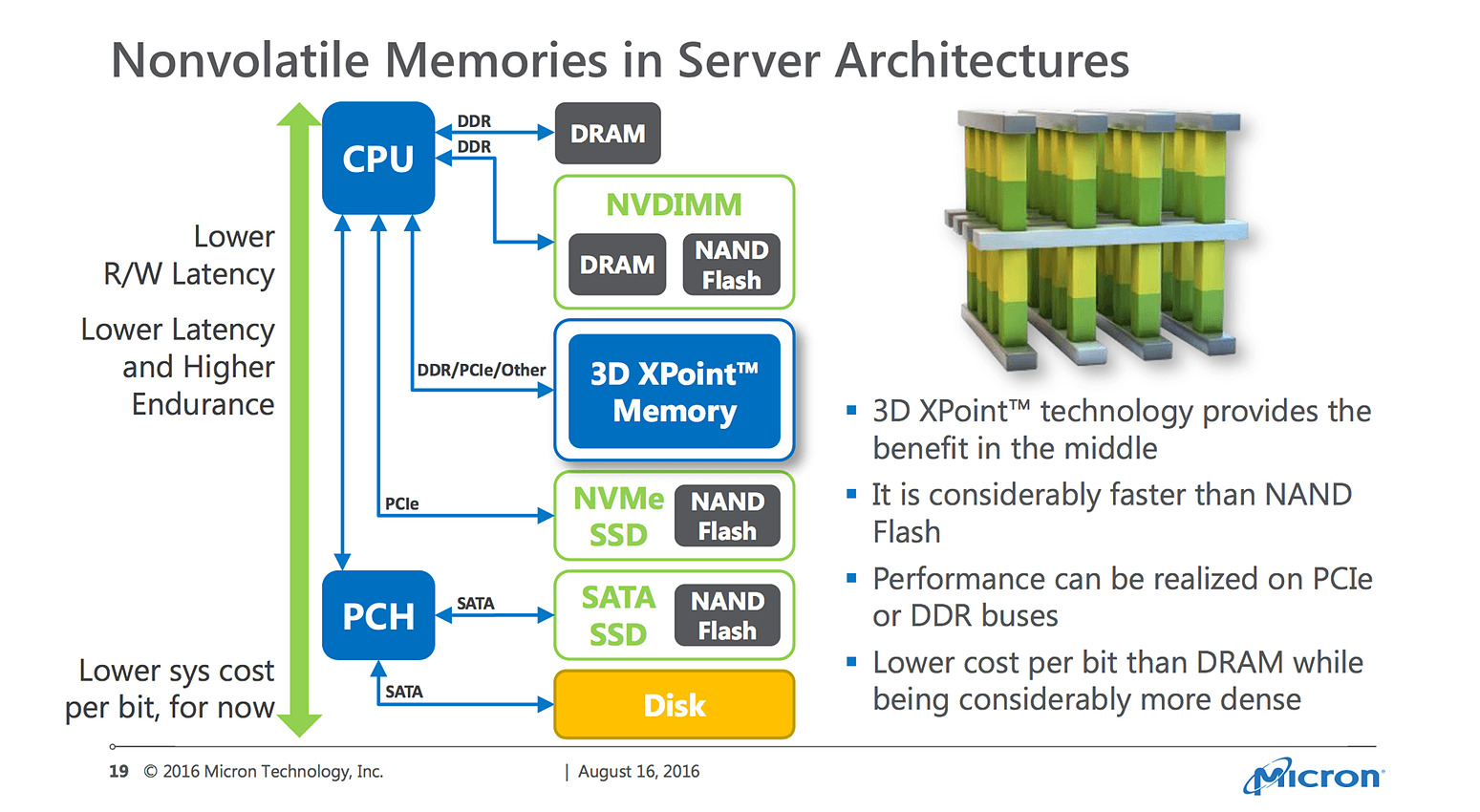

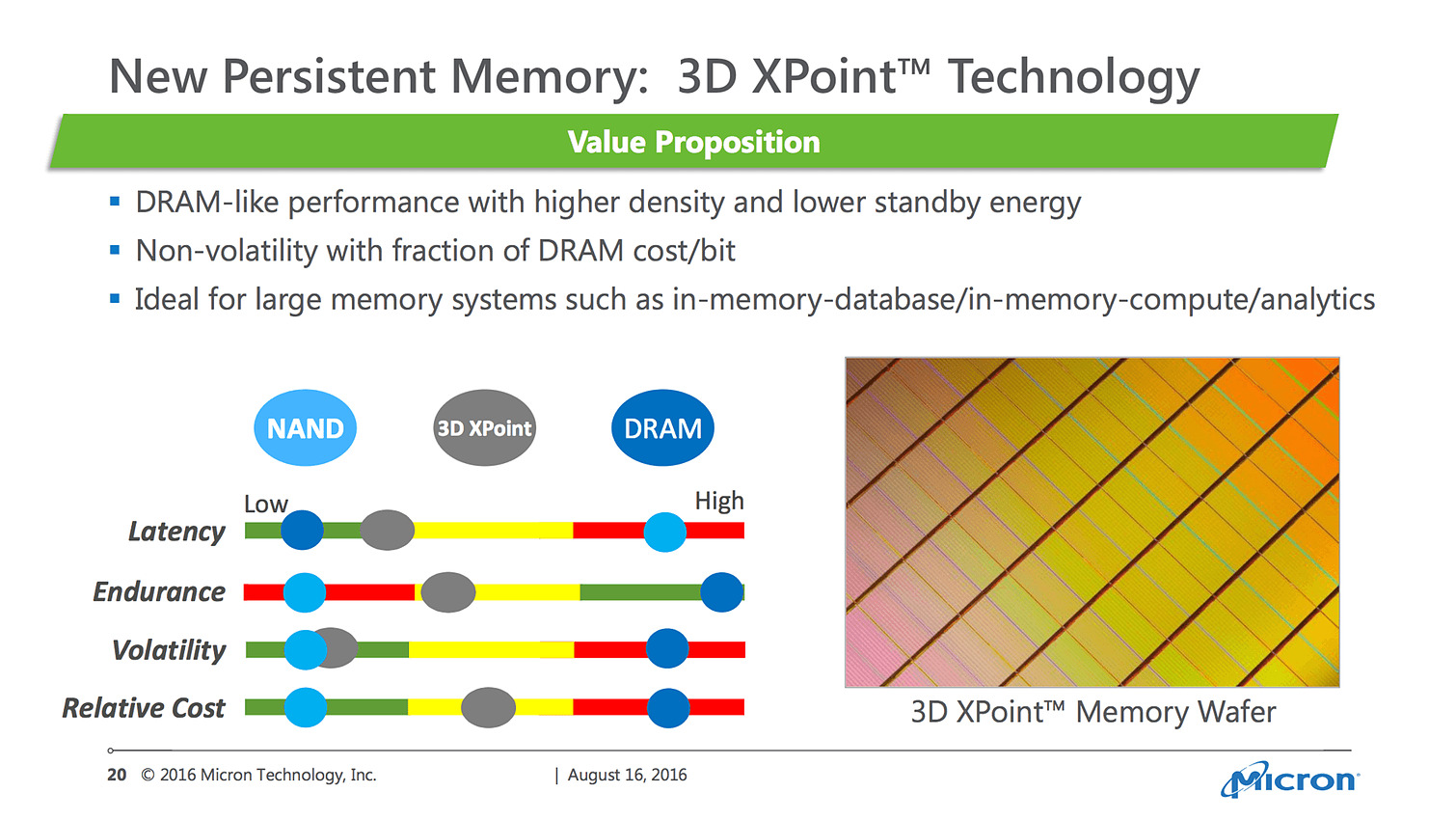

Outre le tacle envers son partenaire Intel sur la mémoire 3D XPoint, on ne retiendra pas beaucoup d'informations, si ce n'est que Micron confirme que ce nouveau type de mémoire sera en production avant la fin de l'année.

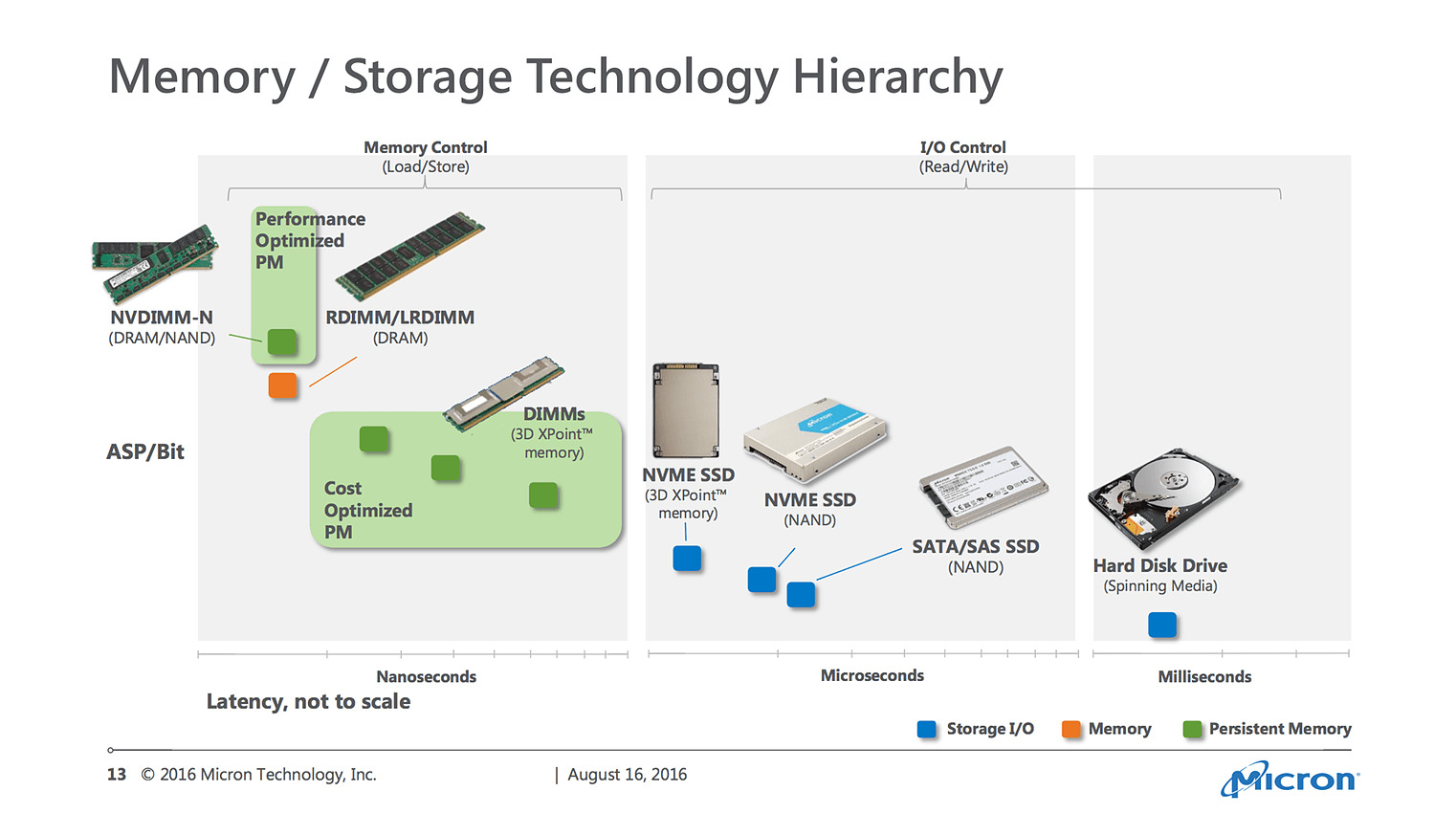

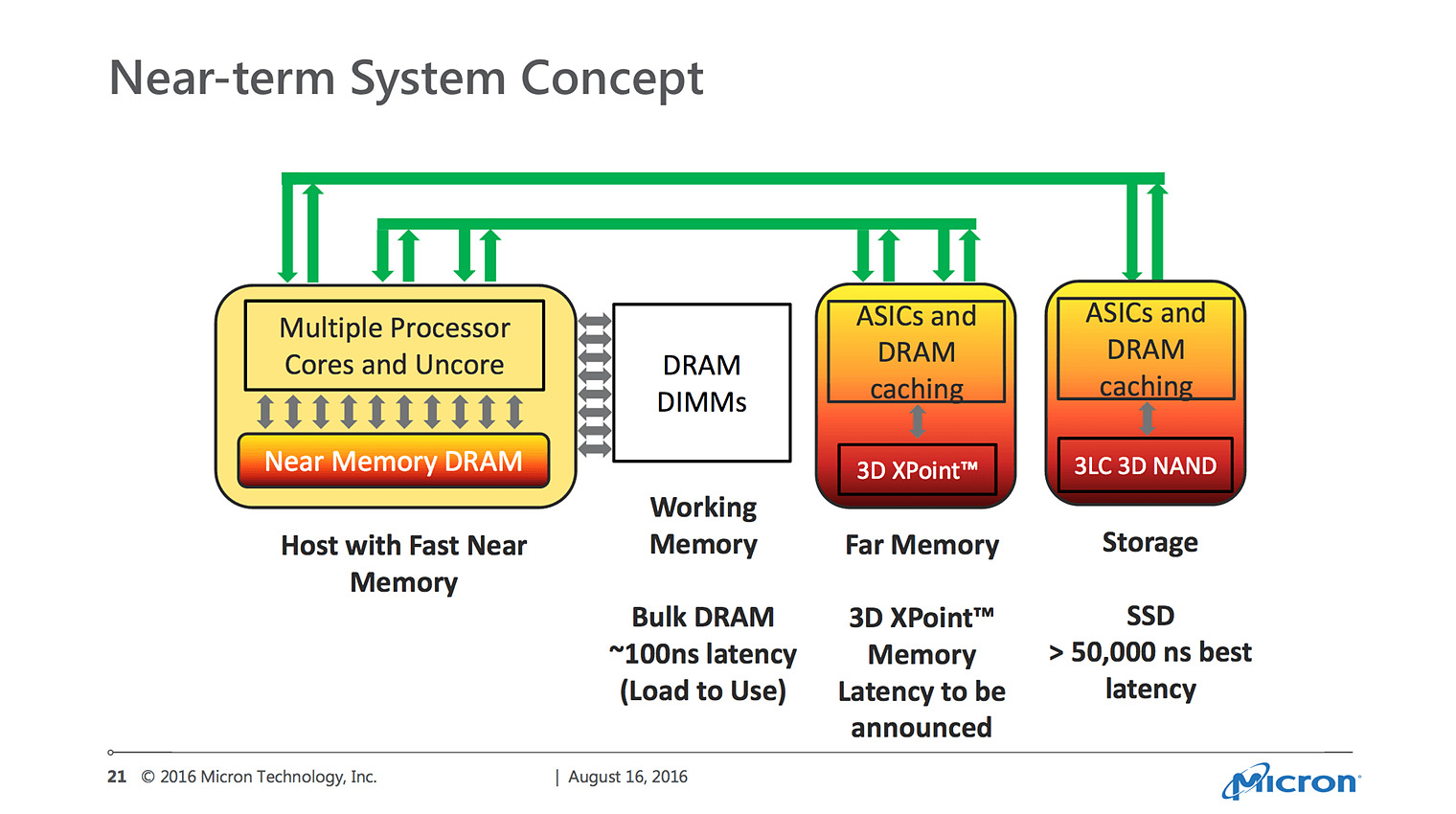

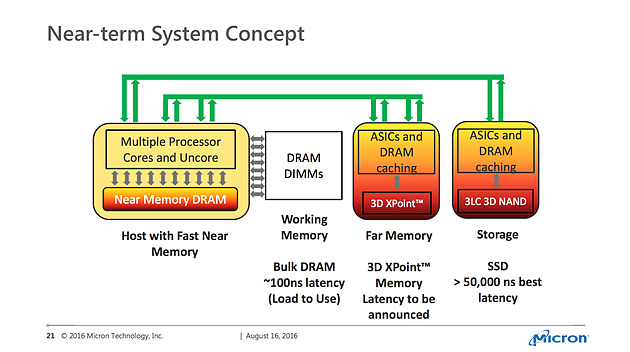

On retiendra ce dernier slide qui préfigure de ce que l'on devrait voir arriver sous peu sur les serveurs, avec deux tiers de mémoire DRAM. D'un côté une mémoire "proche", intégrée au processeur et rapide (HBM, ou plutôt HMC dans la vision de Micron) qui s'adjoint à la mémoire DRAM en barrettes plus classique. 3D XPoint et la 3D NAND proposant de leur côté deux tiers de stockages persistants.

Micron continue dans sa voie de l'originalité, dans un marché de la mémoire certes très concurrentiel. La société continue de mettre en avant sa GDDR5X, certes standardisée par le JEDEC mais qui n'a pas été adoptée par ses concurrents, mais aussi des solutions plus propriétaires comme l'Hybrid Memory Cube et 3D XPoint. Avec les ambitions de SK Hynix et de Samsung de pousser la HBM sur le terrain des PC clients, on peut cependant se demander si le pari d'ignorer la mémoire HBM ne se retournera pas contre Micron dans les mois à venir.

Micron en charge de la mémoire des Knights Landing

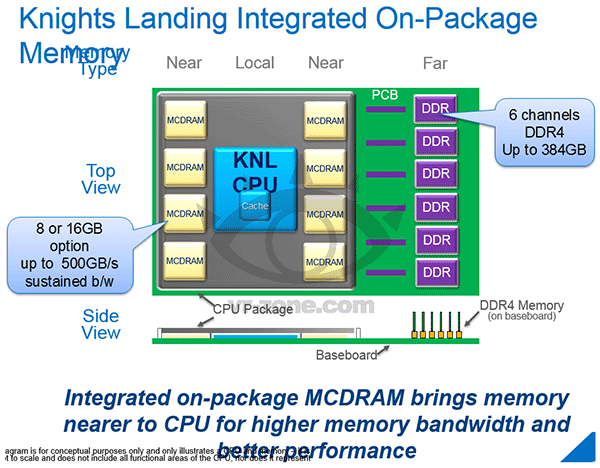

Nous vous en parlions en novembre dernier, la prochaine génération de Xeon Phi (Knights Landing) prévue pour la mi-2015 intégrera jusqu'à 16 Go de mémoire embarquée ultra-rapide délivrant une bande passante de l'ordre de 500 Go /s.

On apprend aujourd'hui que cette mémoire sera produite par Micron, qui l'a développée en collaboration avec Intel en prenant pour base l'Hybrid Memory Cube dont on parle depuis quelques années déjà. Les puces se trouveront sur le même packaging que les Xeon Phi, et seront reliées à ce dernier par une interface à très haute vitesse.

Dans son communiqué Micron indique que cette mémoire a une bande passante 5x supérieure à la DDR4 tout en prenant 50% de place en moins et avec un ratio bande passante/consommation multiplié par 3.

Pour rappel ces nouveaux Xeon Phi gravés en 14nm devraient gérer l'AVX-512, la DDR4, le PCIe Gen3 et seront disponibles en version Socket comme en carte fille PCIe. Un Xeon Phi pourra intégrer jusqu'à 72 curs de type Silvermont associés par paire, gérant chacun deux grosses unités vectorielles prenant en charge le traitement des instructions AVX-512 et partageant un cache L2 de 1 Mo. En sus de la mémoire embarquée, ils géreront six canaux de DDR4 permettant d'adresser 384 Go de mémoire supplémentaire.