Les contenus liés aux tags Intel et Cannon Lake

Afficher sous forme de : Titre | FluxQuelques détails sur Kaby Lake

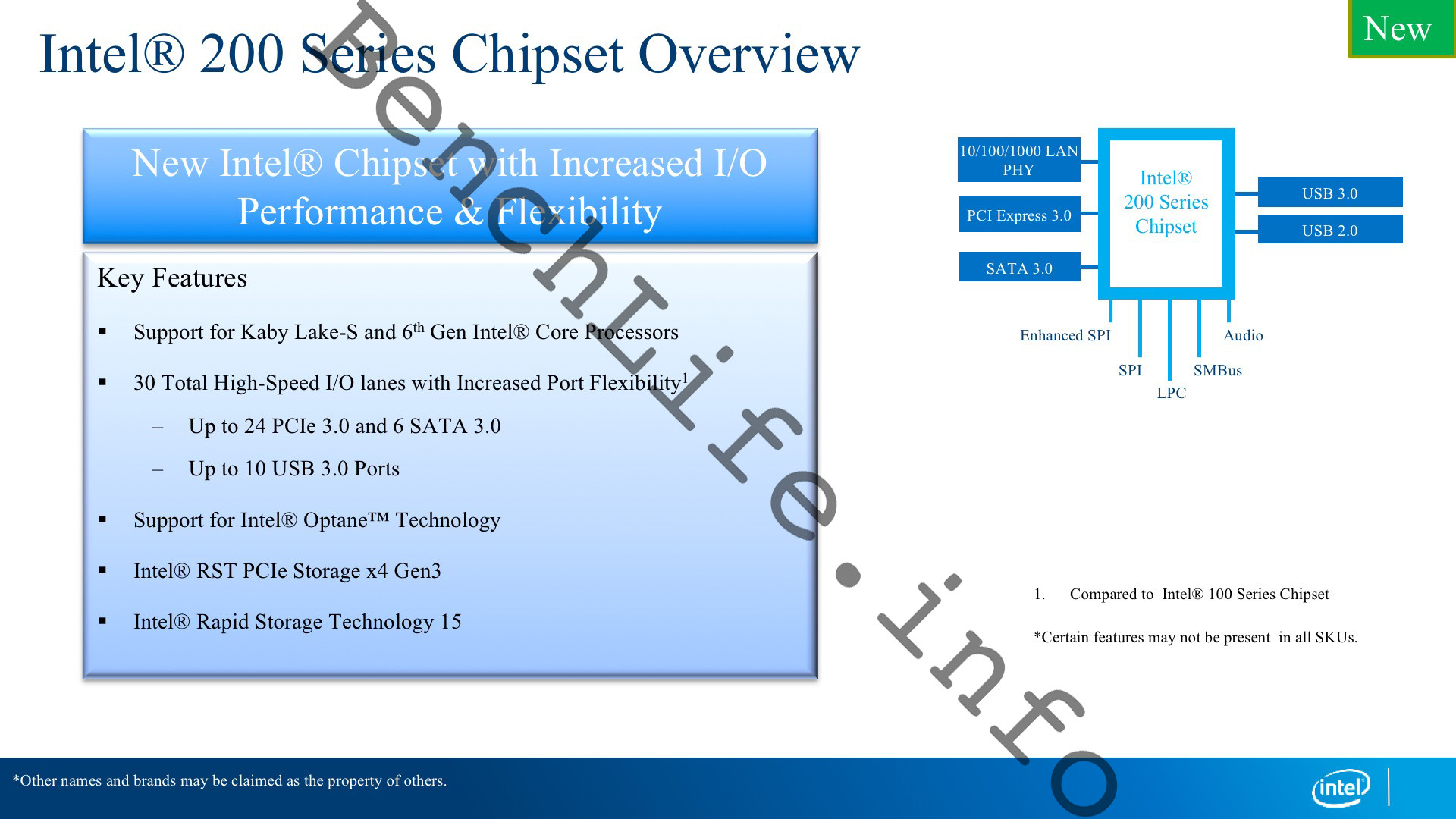

Benchlife.info publie quelques extraits de ce qui serait des documents Intel concernant Kaby Lake. Pour rappel, Kaby Lake est attendu pour fin 2016 environ, il s'agit d'une nouvelle génération de produit 14nm en attendant Cannonlake 10nm qui est en retard. Au niveau de la gamme de chipset Serie 200 qui sortira en même temps on apprend que le nombre combiné de lignes PCIe, ports USB 3.0 et ports SATA passera à 30 contre 26 sur Z170 (cf. ici).

On restera "limité" à un maximum de 10 USB 3.0 et 6 SATA, mais dans cette configuration on pourra disposer de 14 lignes PCIe 3.0 sur un total de 24 possibles, contre 10 sur un total de 20 sur Z170 sachant bien sûr qu'in fine le lien avec le CPU est de type DMI 3.0 équivalent à x4 Gen3. Les chipsets Serie 200 supporteront à la fois Kaby Lake-S et les Skylake actuels, le support des futurs SSD Intel Optane en 3D XPoint est également mentionné bien qu'on ne voit pas ce qui empêcherait leur utilisation, d'un point de vue technique tout du moins, sur les plates-formes actuelles.

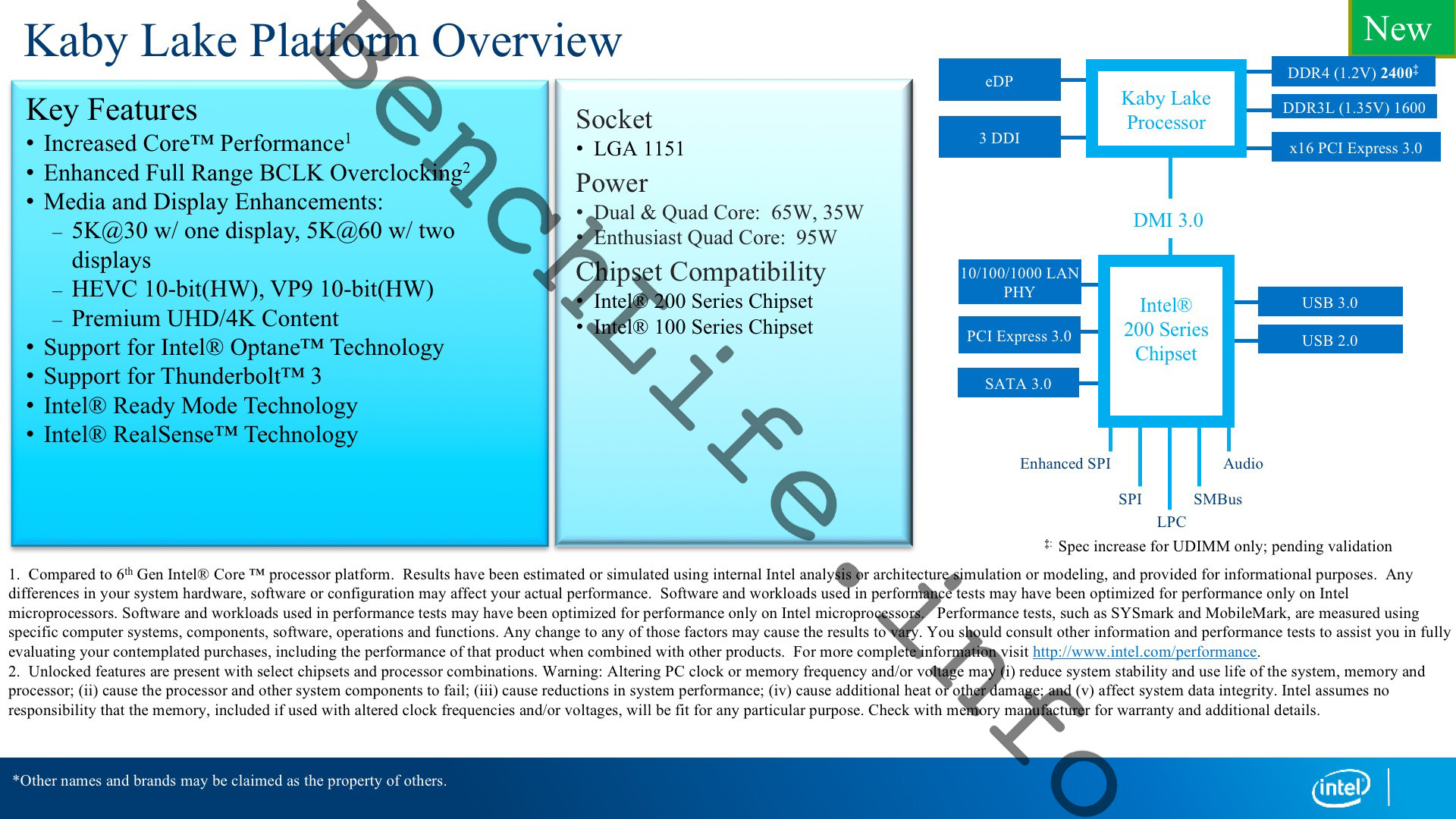

Au niveau du processeur Kaby Lake, il est précisé que les curs CPU seront plus performants, sans que l'on sache par quel biais (IPC et/ou fréquence) et que l'overclocking par le bus sera amélioré. Côté iGPU il sera possible avec un câble DP de piloter un écran 5K à 30 Hz et de passer à 60 Hz avec deux câbles, alors que le décodage du HEVC et du VP9 10-bit sera assuré en hardware. Comme Broadwell-E, Kaby Lake supportera officiellement la DDR4-2400 et il est précisé qu'il sera compatible avec les chipsets actuels Serie 100. Attention toutefois, pour rappel Intel devrait lancer en même temps un "super" Skylake doté d'eDRAM et qui lui ne serait compatible qu'avec les cartes mères en Serie 200 selon les dernières rumeurs !

Kaby Lake pas avant fin 2016 sur desktop

Intel l'a confirmé officiellement en juillet, le tick-tock est abandonné et le 14nm restera d'actualité au second semestre 2016 avec l'arrivée de Kaby Lake, après Broadwell en 2014 et Skylake cette année. Il faudra attendre un an supplémentaire pour voir débarquer Cannonlake et sa gravure en 10nm.

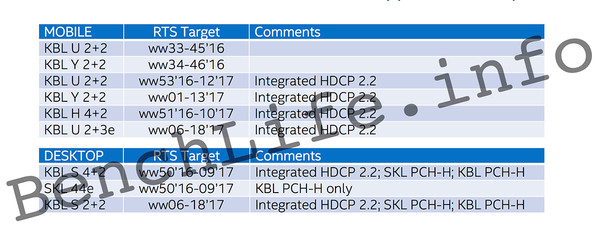

On ne sait encore pas grand choses des améliorations apportées par Kaby Lake mais les dernières informations publiées par Benchlife.info donnent quelques détails pour le timing. Premièrement le lancement se fera en deux temps, puisqu'une première version 2 curs de Kaby Lake sera prête à être livrée sur portables en version U et Y (basse et très basse conso) entre la mi-août et la fin octobre.

Celle-ci ne bénéficiera toutefois pas du support du HDCP 2.2 qui n'arrivera que sur une nouvelle version dont l'arrivée est prévue au mieux en toute fin d'année et plus probablement au premier trimestre 2017 sur portable. Bizarrement seule une version 2 curs se voit associée à un iGPU et de l'eDRAM (3e), et il n'arrivera qu'entre février et mai.

Côté desktop Intel attendra cette révision supportant le HDCP 2.2 avec deux versions qui sont prévues, une première à 4 curs entre mi-décembre 2016 et fin février 2017, une seconde à 2 curs entre février et mai 2017. Ces deux versions sont annotées comme pouvant fonctionner avec les chipsets actuels série 100 ainsi qu'une nouvelle génération qui sortira en même temps. Une bonne nouvelle qu'il faut toutefois tempérer avec la présence d'une autre puce prévue en même temps que les 4 curs mais qui sera cette fois un Skylake 4 curs associé à un GPU de type GT4e, c'est-à-dire complet et avec de l'eDRAM qui apportera des gains de performances également en charge CPU. Cette fois il n'est question d'une compatibilité de cette nouvelle puce qui sera probablement le fer de lance de la gamme Intel en 2017 qu'avec les nouveaux chipsets !

Voilà donc une feuille de route assez erratique qui découle probablement de choix fait dans l'urgence suite au report du 10nm et de Cannonlake. Si on peut comprendre à la rigueur les raisons économiques entraînant un lancement en deux temps sur mobile, surtout si la seule différence se situe au niveau de l'HDCP 2.2, l'arrivée d'un "Skylake+" incompatible avec les cartes mères actuelles serait pour le moins navrante. Ce planning laisse également des doutes sur la capacité d'Intel à maintenir l'arrivée de Cannonlake en 2017.

Intel abandonne le Tick-Tock, confirme Kaby Lake

En marge de l'annonce de ses résultats financiers, la conférence dédiée aux analystes a été l'occasion pour Intel de confirmer ce dont l'on se doutait depuis un long moment : le 10nm du constructeur ne sera pas à l'heure.

En marge de l'annonce de ses résultats financiers, la conférence dédiée aux analystes a été l'occasion pour Intel de confirmer ce dont l'on se doutait depuis un long moment : le 10nm du constructeur ne sera pas à l'heure.

Au milieu de l'annonce de nouveaux retards sur sa roadmap mobile (notamment SoFIA LTE qui est désormais attendu pour la première moitié de 2016), Brian Krzanich a indiqué que la transition d'un node à l'autre ne tenait plus réellement le rythme des 24 mois que le constructeur souhaitait s'imposer, mais que sur les deux générations précédentes, il était plus proche des deux années et demi. En conséquence, la stratégie du Tick-Tock doit s'adapter et il aura confirmé l'arrivée d'un troisième produit 14 nm, Kaby Lake qui sera lancé durant la seconde moitié de 2016 (comme on le pressentait le mois dernier) !

Le CEO d'Intel décrit Kaby Lake comme « bâti sur les fondations de la micro architecture Skylake », mais « avec des améliorations clefs de performances ». Un phrasé relativement vague qui laisse entendre qu'il s'agirait d'un peu plus que d'un « Skylake refresh », sans vraiment s'engager (possiblement un nouveau GPU seulement ?). Le lancement de Cannonlake est lui bel et bien repoussé à la seconde moitié de 2017, en 10nm.

Interrogé (légèrement) sur le sujet par les analystes, Brian Krzanich a qualifié le retard par la complexité croissante de mise au point des process et que les difficultés du 10nm, si elles étaient similaires en pratique à celles rencontrées pour le 14nm, n'étaient pas directement liées au retard du 14nm. Intel est sur le sujet dans une position délicate puisque le constructeur a toujours clamé que le retard du 14nm n'aurait aucun impact sur le 10nm. Selon le CEO, la lithographie continue à être de plus en plus complexe, notamment à cause de l'augmentation des étapes de multi-patterning. En marge de cela, il aura rappelé que le 10nm d'Intel sera une solution sans EUV (le reste de l'industrie ne s'attends pas non plus à disposer de l'EUV pour le 10nm).

Pour le CEO, rajouter Kaby Lake à la roadmap permet d'améliorer la « prévisibilité » pour ses partenaires. Un argument qui ne manque pas d'ironie quand l'on connait l'historique du Tick-Tock chez Intel. La stratégie du Tick-Tock avait été mise en place en interne chez Intel au début des années 2000 par Pat Gelsinger dans le but de mettre de l'ordre dans le développement parfois anarchique des architectures qui a conduit à de nombreux projets et architectures repoussés et abandonnés. En interne, il s'agissait de délimiter clairement le périmètre de deux équipes de développement d'architectures, une située en Oregon et l'autre en Israël. Le tout articulé autour des changements de process tous les deux ans.

Ainsi chaque nouveau passage à un process (65 vers 45 nm, etc) serait un Tick. Une version légèrement modifiée de l'architecture précédente, portée vers le nouveau node (ce que l'on appelle un die shrink), tandis que la « nouvelle architecture », le Tock serait lancé l'année suivante, lorsque le process de fabrication serait arrivé à maturité.

Historiquement, ce n'est qu'avec beaucoup de créativité que le constructeur aura pu compter 24 mois entre chaque node, des retards de plusieurs mois ayant été observés au fil des années mais globalement jusqu'ici Intel s'était imposé de tenir le modèle de deux produits principaux (on met de côté les produits/architecture dédiées spécifiquement à la mobilité) par node sur environ deux ans.

Avec le 14nm le modèle n'était plus tenable, obligeant en 2014 Intel à proposer un Haswell refresh, simple « speed bump » d'Haswell, lancé en juin 2013 en lieu et place de Broadwell. En pratique si Intel s'est targué d'avoir « lancé » le 14nm en 2014, il s'agissait d'un seul processeur, le Core M, qui plus est dans un stepping remplacé avant même sa sortie ! Et pour le desktop, la gamme Broadwell aura été réduite au minimum avec seulement deux modèles, lancés le mois dernier pour tenir les annonces. Avec au final un retard d'un an sur la cadence que s'imposait jusqu'ici Intel.

En pratique Skylake (le tock original 14nm) est toujours attendu pour cette année même si Intel n'a pas encore confirmé de quelle manière s'effectuerait son lancement. Il a été indiqué par Intel qu'une des conséquences du ralentissement de l'activité en Q2 était un inventaire encore important, laissant penser que le constructeur pourrait repousser certains SKU de Skylake. Le lancement des modèles K était prévu pour rappel pour le 5 aout, tandis que le reste de la gamme 4 curs était attendue entre le 30 aout et le 5 septembre. On ne s'étonnerait pas de voir ces références repoussées de plusieurs semaines afin d'écouler les inventaires existants, même si Intel ne l'a pas dit clairement.

On notera également qu'au détour d'une question, Brian Krzanich a confirmé que le 10nm d'Intel utiliserait toujours des FinFET, et non un autre type de structures comme certaines rumeurs avaient pu le laisser entendre. Il a indiqué que le 10nm serait la troisième génération de FinFET d'Intel. A une autre question il a indiqué que des changements de matériaux étaient par contre attendus sans les préciser.

Interrogé enfin sur l'impact de ces retards sur « l'avance » d'Intel en matière de process par rapport au reste de l'industrie, Brian Krzanich s'est voulu rassurant, indiquant que l'avance d'Intel ne diminuerait pas sur le reste de l'industrie. De notre point de vue, il est probable que TSMC, et possiblement Samsung lancent une production en volume autour, voir même un peu avant Intel. Ce qui serait, au moins pour l'image, un véritable drame pour la firme de Santa Clara.

Cannonlake 10nm retardé à 2017, Kaby Lake pour 2016 ?

Selon Benchlife.info , Intel sera en retard sur Canonnlake, qui est pour rappel un "tick" en 10nm de Skylake. Afin d'avoir tout de même une nouveauté à se mettre sous la dent en 2016, une nouvelle ligne de processeur 14nm, Kaby Lake, serait à l'ordre du jour.

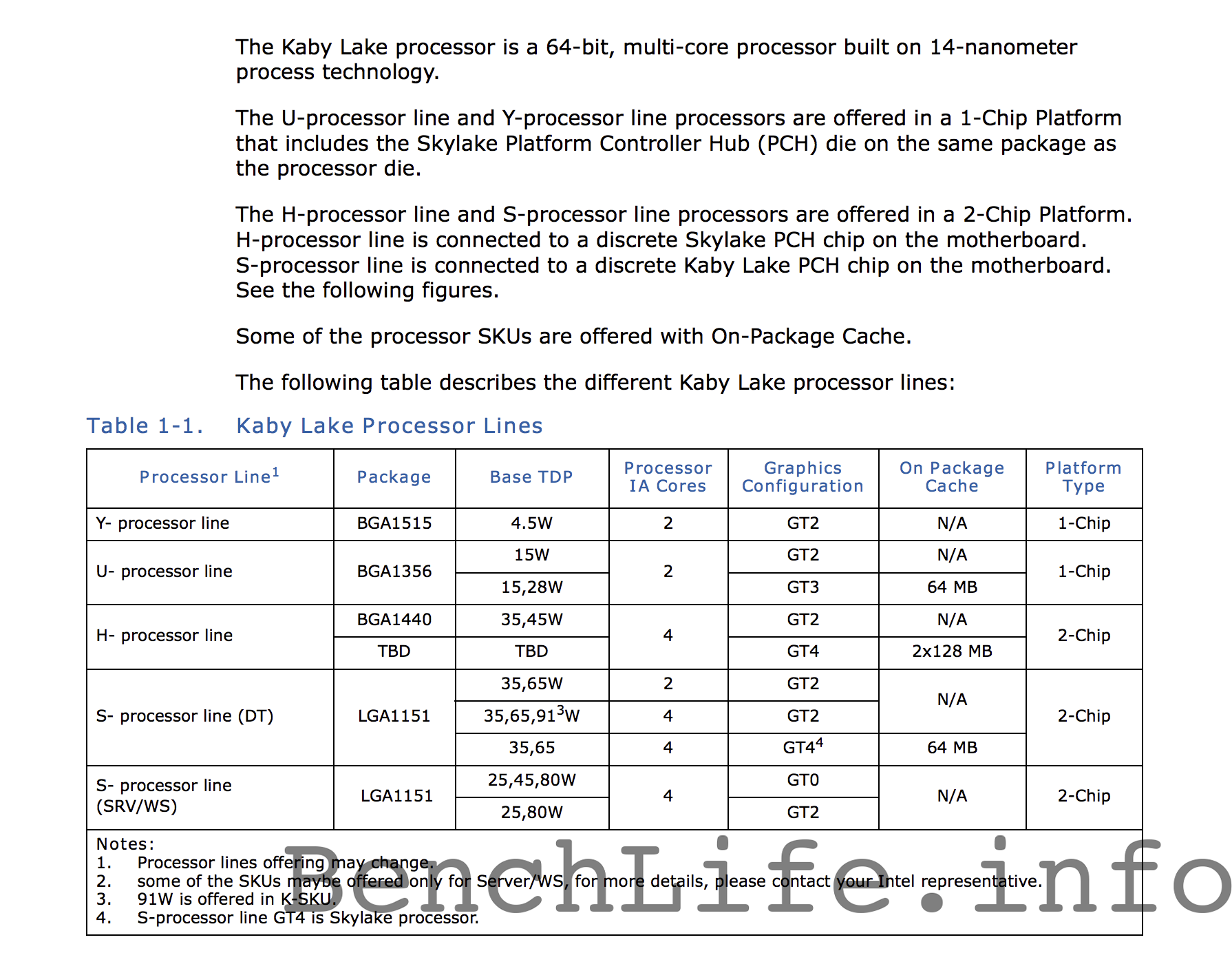

Comme d'habitude de nombreuses déclinaisons sont listées mais on ne sait pas vraiment en quoi ces processeurs seront différent des Skylake. S'agit-il d'un simple speed bump comme nous l'avons déjà connu avec Haswell Refresh ? Seule vraie nouveauté apparente, au format BGA en gamme H une puce est listée avec 2x128 Mo d'eDRAM embarquée, contre au mieux 128 Mo sur Broadwell et Skylake, ce qui devrait permettre d'augmenter les performances de l'iGPU.

Sur desktop on reste en LGA 1151 avec 2 à 4 curs, avec 35/65W en 2 curs et 35/65/91W en 4 curs. Le TDP de 91W concerne les processeurs en version K, ce chiffre est assez étrange puisqu'il est censé être de 95W sur le Skylake K. Intel prévoit également de sortir des versions 4 curs LGA 1151 accompagnées de l'iGPU soit GT4, qui intègre 72 Executions Units (soit 50% de plus que sur un GT3 Skylake ou Broadwell), et de 64 Mo d'eDRAM. Autre bizarrerie alors que ce tableau est censé représenter la ligne de processeurs Kaby Lake ces versions sont annotées comme étant des Skylake !

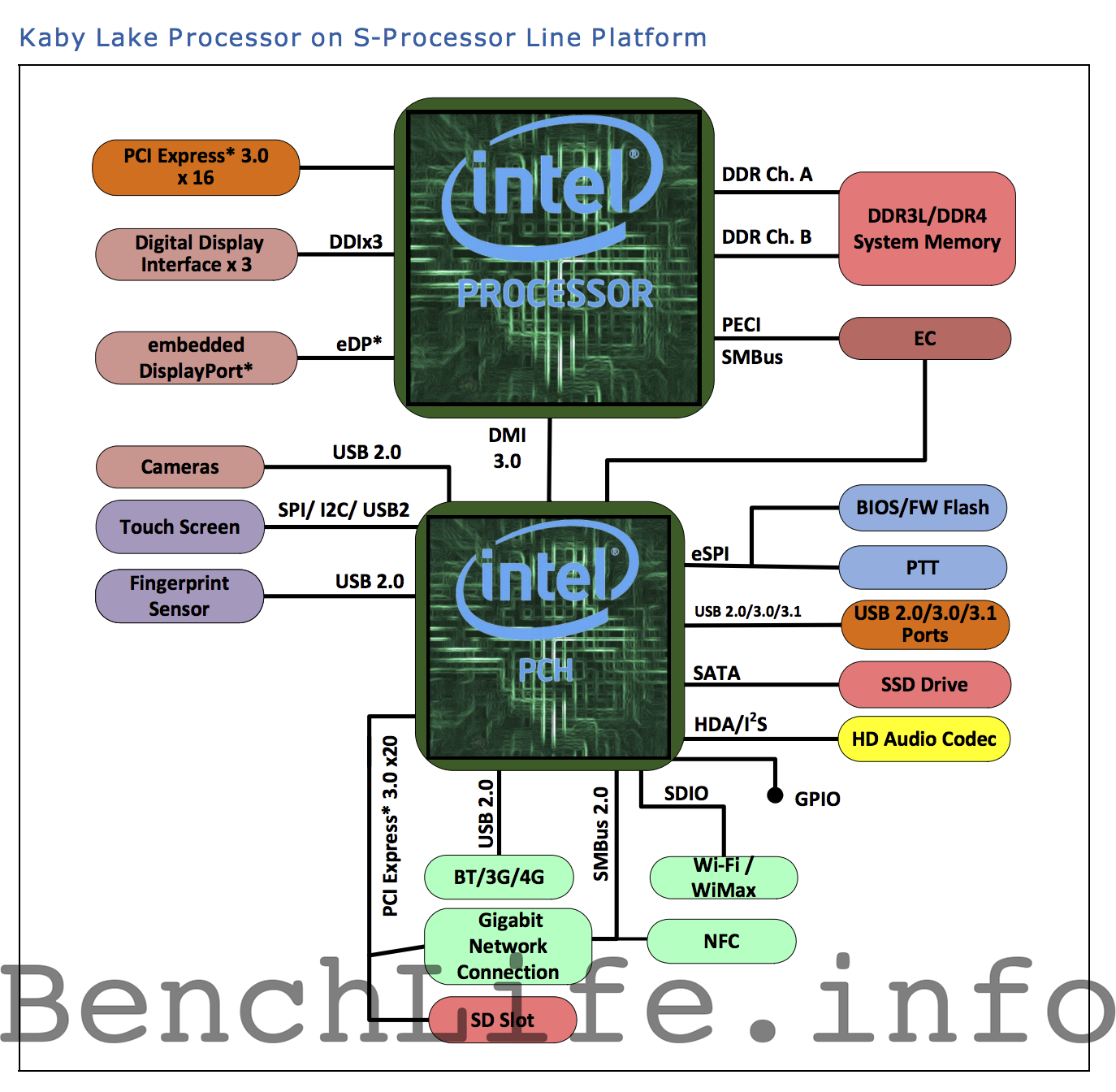

Côté chipset le diagramme laisse penser qu'on aura droit à une nouveauté avec l'arrivée de l'USB 3.1 qui pour rappel double les débits pour atteindre 800 Mo /s en pratique (cf. notre focus). Une mise à jour mineure mais qui permettra à tous les fabricants de cartes mères de sortir leur nouvelle gamme annuelle même en l'absence de nouveauté importante, comme ce fut le cas à l'époque du Z97.

Après un passage au 14nm retardé, Intel connaitrait-il des déboires sur le 10nm ? C'est ce qu'on peut penser si le retard de Cannonlake se confirme, ce qui augure d'une année 2016 assez morose côté CPU chez Intel, alors qu'on attend dans le même temps le retour sur le devant de la scène d'AMD avec Zen !

Pas d'AVX-512 pour les Core i7/i5 Skylake ?!

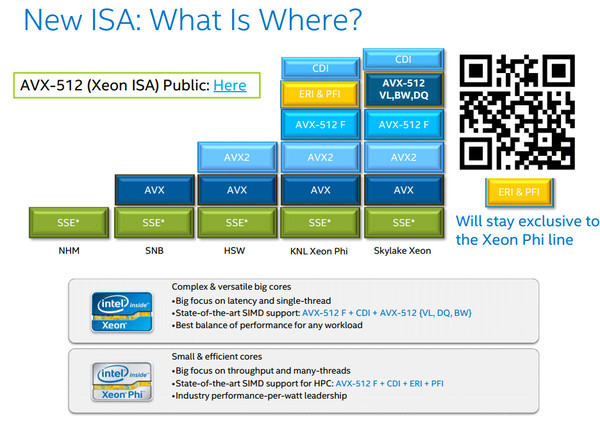

Annoncé en 2013, l'AVX-512 est une extension du jeu d'instruction AVX qui rajoute des instructions SIMD 512 bits, soit le double de l'AVX actuel, pouvant cibler aussi bien des données entières que flottantes. Il est ainsi possible d'appliquer avec ces instructions vectorielles une même opération sur 16 données 32-bits en simultané (ou 8x64 bits), contre deux-fois moins en AVX classique qui se limite à 256-bits d'ou des performances doublées dans des cas rares mais idéaux (cf. cette page pour le principe)

On trouve plusieurs groupes d'instructions AVX-512, avec pour commencer un socle commun dénommé AVX-512 Foundation (AVX512F) qui sera à la fois supporté par les processeurs x86 à compter de Skylake mais aussi par les coprocesseurs Xeon Phi à compter de Knights Landing, ces deux architectures devant voir le jour cette année. On trouve également des groupes d'instructions additionnels destinés à des domaines spécifiques et qui sont détaillé dans l'Intel Architecture Instruction Set Extensions Programming Reference .

Dans une présentation de juillet 2014 , Intel précisait que Skylake supporterait AVX512F ainsi que trois groupes d'instructions supplémentaires AVX512BW et AVX512DQ ainsi que la possibilité de travailler sur des vecteurs de taille inférieure à 512-bits (AVX512VL). Mais il était également précisé qu'AVX-512 était un jeu d'instruction pour Xeon, et ce n'est pas Skylake mais bien "Skylake Xeon" qui est mentionné.

Les Skylake en version "Core" seront-ils dépourvus d'AVX-512 ? Un autre indice se situe sur cette page dédiée à l'Intel Software Development Emulator, un logiciel qui permet d'émuler sur les processeurs actuels le support de futurs jeux d'instruction. Elle précise que les dernières versions apportent l'émulation d'instructions AVX-512 supplémentaires qui seront supportées par de futures versions des Intel Xeon qui seront introduites après Knights Landing. Difficile de savoir si il est bien question de Skylake ou de son successeur CannonLake, mais dans tous les cas il n'est bien question que de Xeon.

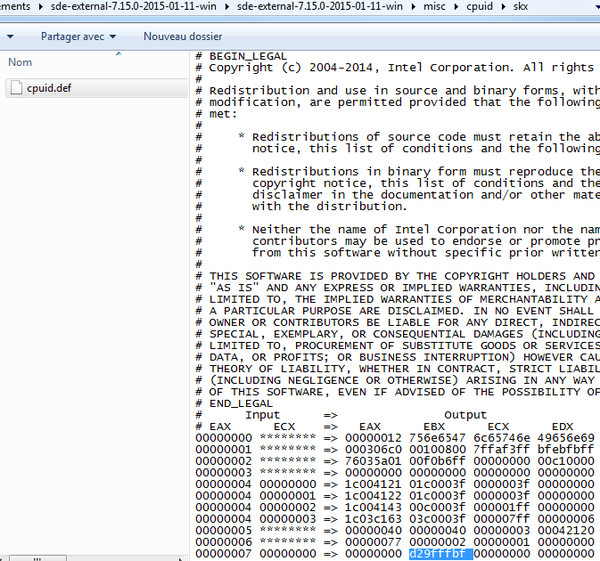

Pour aller plus loin nous avons téléchargé le logiciel Intel SDE qui propose dans son répertoire \misc\cpuid les CPUID (cf. Wikipedia ) attendus pour les futurs processeurs Intel présent mais aussi à venir. On trouve ainsi par exemple un sous-répertoire hsw pour Haswell, bdw pour Broadwell, cnl pour CannonLake mais aussi skl pour Skylake et sklx pour Skylake dans sa déclinaison Xeon. Si on analyse le contenu des registres permettant de connaitre les instructions supportées par les processeurs, on se rend compte que seul Skylake dans sa déclinaison Xeon supporte AVX512F (ainsi que AVX512VL, AVX512CD, AVX512DQ, AVX512BW) !

En jetant un il au contenu des versions précédentes de Intel SDE on note la présence du répertoire skl dès la dernière version encore téléchargeable, la 6.22 de mars 2014. Le CPUID est inchangé par rapport à la version actuelle, et il est probablement présent comme tel depuis la version 6.1 de juillet 2013 ayant introduit le support de Skylake pour l'émulation des instructions MPX. L'apparition du répertoire sklx date pour sa part 7.1.0 de juillet pour lequel Intel indiquait "Added support for additional Intel AVX-512 instructions.".

CannonLake a pour sa part fait son apparition avec la version 7.8 de juillet dernier pour laquelle il est indiqué "Added support for additional Intel AVX-512 instructions (AVX512-VMBI and AVX512-IFMA).", ces deux extensions d'AVX-512 étant bien annoncées comme supportées par le CPUID présent pour ce successeur de Skylake prévu pour 2016 en 10nm. Cette fois il n'y a pas de précision concernant les Xeon, ce qui laisse supposer qu'AVX-512 sera étendu aux processeurs grand public.

Au final si on combine la présentation de juillet et ce que l'on trouve dans Intel SDE, il apparait clairement qu'Intel a pour stratégie de réserver l'AVX-512 à la gamme Xeon sur la génération Skylake. Bien entendu, au moins dans un premier temps l'AVX-512 et sa transversalité avec les Xeon Phi intéressera surtout le monde professionnel, les applications devant être réécrites pour en tirer profit alors que les gains liés à une vectorisations sur 512-bit ne devraient concerner qu'une petite frange des calculs.

Reste maintenant à savoir si cette nouvelle segmentation est purement artificielle ou non, c'est-à-dire si les Skylake Xeon supportant AVX-512 seront les Xeon E3 v4 qui partageront la même puce que les Core i5 et i7, ou si AVX-512 sera réservé aux gros Skylake-E/EP/EX basés sur d'autres puces. Sachant que ces derniers ne devraient pas débarquer avant le second semestre 2016 dans le meilleur des cas, la première hypothèse semble la plus logique. Un tel bridage serait en tout cas une première qu'on ne peut que regretter : jusqu'alors les nouveaux jeux d'instructions SSE ou AVX étaient disponibles sur la gamme Core, seuls les Pentium et Celeron étant bridés à ce niveau.