| |

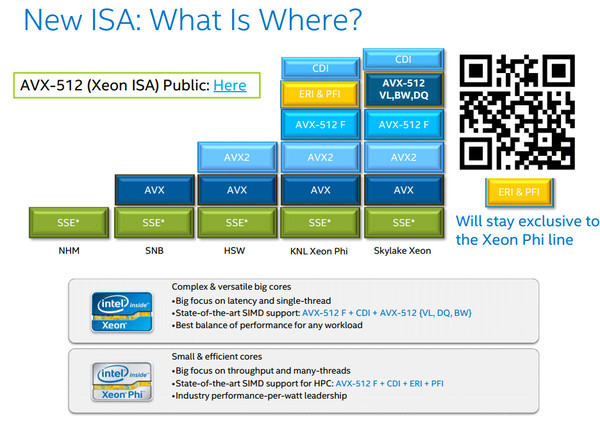

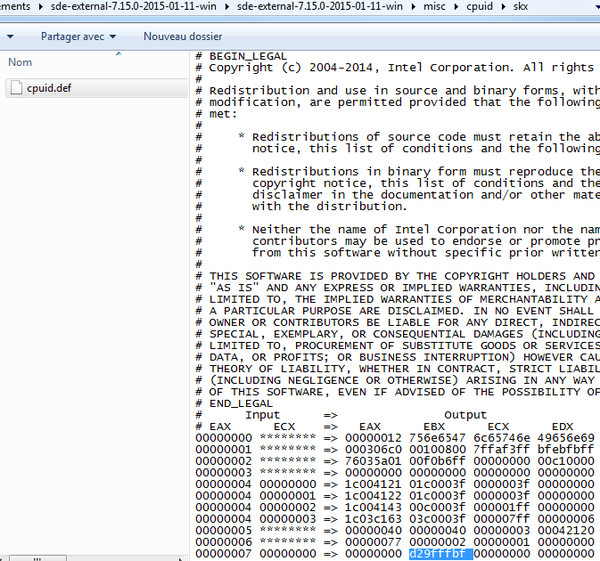

| Pas d'AVX-512 pour les Core i7/i5 Skylake ?! Processeurs Publié le Vendredi 6 Mars 2015 par Marc Prieur URL: /news/14121/avx-512-core-i7-i5-skylake.html Annoncé en 2013, l'AVX-512 est une extension du jeu d'instruction AVX qui rajoute des instructions SIMD 512 bits, soit le double de l'AVX actuel, pouvant cibler aussi bien des données entières que flottantes. Il est ainsi possible d'appliquer avec ces instructions vectorielles une même opération sur 16 données 32-bits en simultané (ou 8x64 bits), contre deux-fois moins en AVX classique qui se limite à 256-bits d'ou des performances doublées dans des cas rares mais idéaux (cf. cette page pour le principe) On trouve plusieurs groupes d'instructions AVX-512, avec pour commencer un socle commun dénommé AVX-512 Foundation (AVX512F) qui sera à la fois supporté par les processeurs x86 à compter de Skylake mais aussi par les coprocesseurs Xeon Phi à compter de Knights Landing, ces deux architectures devant voir le jour cette année. On trouve également des groupes d'instructions additionnels destinés à des domaines spécifiques et qui sont détaillé dans l'Intel Architecture Instruction Set Extensions Programming Reference .  Dans une présentation de juillet 2014 , Intel précisait que Skylake supporterait AVX512F ainsi que trois groupes d'instructions supplémentaires AVX512BW et AVX512DQ ainsi que la possibilité de travailler sur des vecteurs de taille inférieure à 512-bits (AVX512VL). Mais il était également précisé qu'AVX-512 était un jeu d'instruction pour Xeon, et ce n'est pas Skylake mais bien "Skylake Xeon" qui est mentionné. Les Skylake en version "Core" seront-ils dépourvus d'AVX-512 ? Un autre indice se situe sur cette page dédiée à l'Intel Software Development Emulator, un logiciel qui permet d'émuler sur les processeurs actuels le support de futurs jeux d'instruction. Elle précise que les dernières versions apportent l'émulation d'instructions AVX-512 supplémentaires qui seront supportées par de futures versions des Intel Xeon qui seront introduites après Knights Landing. Difficile de savoir si il est bien question de Skylake ou de son successeur CannonLake, mais dans tous les cas il n'est bien question que de Xeon. Pour aller plus loin nous avons téléchargé le logiciel Intel SDE qui propose dans son répertoire \misc\cpuid les CPUID (cf. Wikipedia ) attendus pour les futurs processeurs Intel présent mais aussi à venir. On trouve ainsi par exemple un sous-répertoire hsw pour Haswell, bdw pour Broadwell, cnl pour CannonLake mais aussi skl pour Skylake et sklx pour Skylake dans sa déclinaison Xeon. Si on analyse le contenu des registres permettant de connaitre les instructions supportées par les processeurs, on se rend compte que seul Skylake dans sa déclinaison Xeon supporte AVX512F (ainsi que AVX512VL, AVX512CD, AVX512DQ, AVX512BW) !  En jetant un il au contenu des versions précédentes de Intel SDE on note la présence du répertoire skl dès la dernière version encore téléchargeable, la 6.22 de mars 2014. Le CPUID est inchangé par rapport à la version actuelle, et il est probablement présent comme tel depuis la version 6.1 de juillet 2013 ayant introduit le support de Skylake pour l'émulation des instructions MPX. L'apparition du répertoire sklx date pour sa part 7.1.0 de juillet pour lequel Intel indiquait "Added support for additional Intel AVX-512 instructions.". CannonLake a pour sa part fait son apparition avec la version 7.8 de juillet dernier pour laquelle il est indiqué "Added support for additional Intel AVX-512 instructions (AVX512-VMBI and AVX512-IFMA).", ces deux extensions d'AVX-512 étant bien annoncées comme supportées par le CPUID présent pour ce successeur de Skylake prévu pour 2016 en 10nm. Cette fois il n'y a pas de précision concernant les Xeon, ce qui laisse supposer qu'AVX-512 sera étendu aux processeurs grand public. Au final si on combine la présentation de juillet et ce que l'on trouve dans Intel SDE, il apparait clairement qu'Intel a pour stratégie de réserver l'AVX-512 à la gamme Xeon sur la génération Skylake. Bien entendu, au moins dans un premier temps l'AVX-512 et sa transversalité avec les Xeon Phi intéressera surtout le monde professionnel, les applications devant être réécrites pour en tirer profit alors que les gains liés à une vectorisations sur 512-bit ne devraient concerner qu'une petite frange des calculs. Reste maintenant à savoir si cette nouvelle segmentation est purement artificielle ou non, c'est-à-dire si les Skylake Xeon supportant AVX-512 seront les Xeon E3 v4 qui partageront la même puce que les Core i5 et i7, ou si AVX-512 sera réservé aux gros Skylake-E/EP/EX basés sur d'autres puces. Sachant que ces derniers ne devraient pas débarquer avant le second semestre 2016 dans le meilleur des cas, la première hypothèse semble la plus logique. Un tel bridage serait en tout cas une première qu'on ne peut que regretter : jusqu'alors les nouveaux jeux d'instructions SSE ou AVX étaient disponibles sur la gamme Core, seuls les Pentium et Celeron étant bridés à ce niveau. Copyright © 1997-2026 HardWare.fr. Tous droits réservés. |