Les derniers contenus liés aux tags AMD et ARM

Afficher sous forme de : Titre | FluxAMD lance ses Opteron A1100 en ARM

Résultats en baisse pour AMD

La spécification HSA 1.0 disponible

AMD annonce son projet Skybridge et le K12

AMD annonce les Opteron ARM Seattle

Jim Keller rejoint... Intel !

C'est une petite surprise, Jim Keller, ingénieur connu pour les plus gros succès d'AMD (Athlon, Athlon 64 et Zen) rejoint aujourd'hui Intel d'après nos confrères de Fortune .

Connu pour son rôle dans le design des DEC Alpha, il a également dirigé les équipes qui ont conçu les K7 (Athlon) et K8 (Athlon 64) pour AMD, avant de se retrouver suite à un rachat (de P.A. Semi) en charge de la future architecture ARM custom d'Apple. Il est retourné en 2012 chez AMD ou il s'est occupé de l'architecture de Zen.

Depuis, il avait tenu plusieurs postes, dont un passage éclair chez Samsung. Depuis deux ans, il avait rejoint Tesla en tant que Vice Président en charge du hardware custom embarqué. Suite au départ de Chris Lattner (ex-Apple), il avait également récupéré la direction d'Autopilot.

Intel n'a pas encore communiqué officiellement sur son rôle, le communiqué de Tesla indiquant simplement que "la passion principale de Jim était l'ingénierie de micoprocesseurs et qu'il rejoint une société ou il pourra de nouveau s'y consacrer exclusivement".

Des failles de sécurité spécifiques aux Ryzen ?

Une firme de sécurité israélienne, CTS-Labs, a publié ces dernières heures un site web ainsi qu'un whitepaper décrivant selon eux treize vulnérabilités critiques (regroupées en 4 familles de failles) touchant les processeurs AMD Ryzen et dérivés. Le whitepaper publié est relativement avare en détails techniques (pour ne pas dire superficiel), mais il décrit globalement les méthodes et les impacts.

Trois "familles" de failles pour deux cibles distinctes

La première famille de faille, Masterkey, regroupe plusieurs attaques qui permettraient d'exécuter du code malicieux sur le Secure Processor (un CPU ARM Cortex A5 inclut dans les processeurs Ryzen, il s'agit peu ou prou du pendant de l'Intel Management Engine pour faire un parallèle). Le Secure Processor disposant (comme le ME) d'un niveau de privilège supérieur au reste du système, ce type de faille est en général considéré comme particulièrement critique (nous reviendrons plus bas sur l'impact réel). Dans ce cas cependant, l'exploitation des failles requiert que l'on flash au préalable un BIOS modifié/corrompu, ce qui limite sensiblement sa portée et sa facilité de déploiement.

La seconde famille de faille, Ryzenfall, s'attaque également au Secure Processor (l'ARM Cortex A5), ou plus précisément à son OS (Secure OS). AMD a choisi pour rappel d'utiliser les mécanismes de sécurité développés par ARM (TrustZone ). Deux implémentations de TEE (Trusted Execution Environment) coexistent, une développée par Qualcomm (QSEE) et l'autre par Trustonic (Kibini ). C'est cette dernière qui serait utilisée par AMD pour son "Secure OS" d'après le whitepaper. Les failles permettraient là aussi d'exécuter du code sur le Secure Processor et de bypasser les protections mémoires sous Windows. L'exploitation des failles est décrite comme requérant un accès système administrateur ainsi qu'un pilote signé spécifique (on ne sait pas lequel, s'il s'agit d'un pilote communément installé par les drivers AMD, ni s'il s'agit d'une version particulière du pilote). Bien que cela ne soit pas dit explicitement dans le whitepaper qui est assez avare en détails, le fait qu'un pilote Windows soit nécessaire laisse penser d'une part que la faille est spécifique à Windows, et de l'autre que la faille semble en grande partie logicielle. A noter que la troisième "famille" de faille, Fallout, est le pendant exact de Ryzenfall mais cette fois ci appliqué à Epyc plutôt qu'à Ryzen.

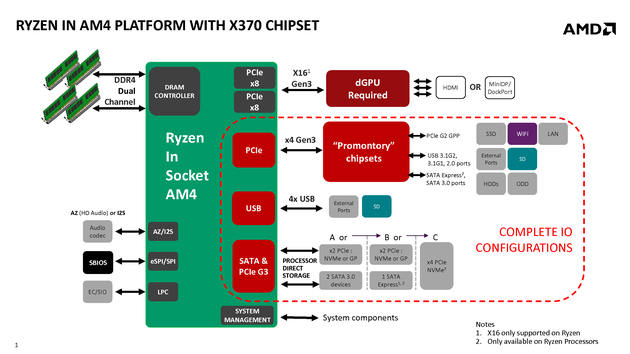

La dernière famille de faille, Chimera, s'attaque enfin au chipset utilisé par AMD pour les cartes mères Ryzen (les X370 et dérivés, connus sous le nom de code Promontory).

Ces chipsets sont pour rappels développés par Asmedia et s'occupent des I/O "lentes" (USB, SATA, réseau, ce que l'on appelait historiquement un southbridge). La faille pointée par la société permettrait d'exécuter du code directement sur le chipset et d'accéder à la mémoire via le DMA. Le whitepaper parle de deux failles distinctes, une liée au firmware, et l'autre lié au design de l'ASIC. L'exploitation de cette faille demanderait là aussi un accès système administrateur et un pilote signé (Windows n'est pas mentionné explicitement cette fois ci).

Des failles complexes à exploiter et peut être pas nouvelles

La première chose qu'il nous semble important de pointer est que ces failles requièrent systématiquement un accès administrateur (et donc un système déjà compromis) et soit un pilote signé, soit un BIOS modifié pour qu'elles soient exploitables. Elles sont incomparables de leur description avec des failles comme Meltdown qui permet sur les processeurs Intel une escalade de privilèges d'un espace mémoire userland vers root, ou comme les variantes de Spectre qui s'attaquent aux mécanismes d'exécution spéculatifs.

Ici, deux cibles distinctes sont pointées. Les trois premières familles de failles s'attaquent au Secure Processor et à son système d'exploitation avec une même finalité, exécuter du code dans l'environnement sécurisé. Si l'on doit faire un parallèle, ces failles font échos aux divers problèmes rencontrés par Intel autour de son Management Engine. Il ne s'agit pas non plus de la première fois que des failles sont pointées sur le Secure Processor d'AMD. En janvier 2018, une faille s'attaquant au trustlet (le nom des programmes tournant dans l'environnement TrustZone) fTPM (l'implémentation "firmware" du TPM, à distinguer d'un TPM hardware via le connecteur présent sur les cartes mères) avait été publiée par un ingénieur des équipes de sécurité de Google Cloud. Un patch avait été mis à disposition courant décembre par AMD. Rien ne laisse penser qu'AMD ne pourra pas corriger de la même manière ces failles qui semblent reposer sur le TEE et/ou sur les trustlets utilisés par AMD. La description de certaines des failles nous laisse penser qu'elles pourraient être exploitables sur d'autres SoC qui utiliseraient l'implémentation TEE de Trustonic (c'est le cas de certains SoC Samsung par exemple).

On notera aussi que le Project Zero de Google avait pointé l'été dernier un bon nombre de limites/failles dans les implémentations TrustZone/TEE de Qualcomm et de Trustonic, particulièrement au niveau de la question de la révocation de trustlets. Dans le cas de l'OS de Trustonic, la version 400 (utilisée par Samsung à partir des SoC intégrés dans les Galaxy S8) renforce les possibilités de révocation qui lorsqu'elles sont bypassées peuvent être utilisées pour exploiter des bugs présents dans d'anciennes versions du firmware (Project Zero décrit sur son blog une attaque sur le TEE de Trustonic pour les versions précédentes). Les détails dévoilés par la firme de recherche sont ténus, mais le fait qu'un flashage de BIOS soit nécessaire nous fait penser que la faille exploitée est peut être celle décrite par Google en juillet dernier.

On note d'ailleurs que les failles s'attaquent spécifiquement au fTPM ou à des fonctionnalités spécifiques du BIOS qui deviendraient désactivables. C'est là que les parallèles s'arrêtent d'ailleurs avec les failles du ME d'Intel puisque les descriptions de Masterkey ne parlent pas de la possibilité d'accéder à de la mémoire privilégiée, mais plutôt d'exécuter du code sur le SP sans préciser ce que cela veut dire réellement. Le blog Project Zero explique l'impact relatif :

"And what of Trustonic's TEE? Unlike QSEE's model, trustlets are unable to map-in and modify physical memory. In fact, the security model used by Trustonic ensures that trustlets aren't capable of doing much at all. Instead, in order to perform any meaningful operation, trustlets must send a request to the appropriate driver. This design is conducive to security, as it essentially forces attackers to either compromise the drivers themselves, or find a way to leverage their provided APIs for nefarious means. Moreover, as there aren't as many drivers as there are trustlets, it would appear that auditing all the drivers in the TEE is indeed feasible. "

Il n'y a donc pas d'accès mémoire direct autorisé aux trustlets, contrairement au modèle de sécurité utilisé par l'Intel Management Engine. Qui plus est, le whitepaper pointe le problème spécifique des pilotes (qui semble être ce qu'exploite Ryzenfall/Fallout qui requiert comme nous l'expliquions un pilote signé et qui est capable d'accès mémoire privilégié, on l'imagine via le pilote comme le décrit Google) comme point d'entrée, et la manière de mitiger les attaques, ce qui fait là aussi écho au papier de Project Zero :

" Although trustlets aren't granted different sets of capabilities, drivers can distinguish between the trusted applications requesting their services by using the caller's UUID. Essentially, well-written drivers can verify that whichever application consumes their services is contained within a whitelist, thus minimising the exposed attack surface. Sensitive operations, such as mapping-in and modifying physical memory are indeed unavailable to trusted applications. They are, however, available to any driver. As a result, driver authors must be extremely cautious, lest they unintentionally provide a service which can be abused by a trustlet."

Les parallèles dans la description du whitepaper nous laisse penser qu'il s'agit soit des failles décrites par le Project Zero l'été dernier, soit de variantes spécifiques aux trustlets utilisées par AMD. Si l'on ne connaît pas la version de Kibini utilisée par AMD dans les Ryzen, rien ne semble empêcher théoriquement le constructeur et Trustonic de sécuriser leurs pilotes (même s'ils ne semblent pas l'avoir fait, ou suffisamment depuis la publication de juillet dernier pour peu que les failles soient présentes dans les dernières versions des pilotes) et bloquer les failles publiées.

Le cas ASMedia

La quatrième famille de failles s'attaque spécifiquement au "chipset" fourni par ASMedia. Le whitepaper pointe le fait que le chipset est l'amalgamation sur un même die d'un contrôleur USB 3.1 ASM1142, d'un contrôleur SATA ASM1061 et d'un pont PCI Express. S'ils ne le disent pas explicitement pour leur faille, sur la page suivante la firme indique que les contrôleurs USB ASM1142 ont "une sécurité en dessous des standards" et qu'ils contiennent "des vulnérabilités côté logiciel et hardware".

Il nous est difficile d'évaluer les dires de la firme sur ce point, mais plus globalement, la sécurité des puces additionnelles intégrées sur les cartes mères est un problème important qui est en général limité par le fait que l'accès au périphérique est restreint par un pilote signé. Sans plus de détails il est impossible de savoir si la faille est liée à une version spécifique de pilote, si elle a été corrigée, ou si elle est corrigeable. Mais dans l'absolu, le fait que la faille semble liée a l'ASM1142 spécifiquement (et possiblement à sa version précédente, l'ASM1042) fait que son impact va bien au delà de Ryzen, ces puces contrôleurs USB 3.1 étant utilisées sur la quasi totalité des cartes mères vendues ces dernières années.

Un marketing très appuyé et orienté

Si la description technique des failles nous fait nous poser des questions sur leur impact réel et leur nouveauté, le marketing qui les entoure nous semble également assez orienté.

D'abord, là où en général les failles de sécurités sont communiquées en amont aux constructeurs, pour qu'ils puissent avoir une chance de les corriger, on notera que CTS Labs ne s'est fait connaître auprès d'AMD que 24 heures avant la publication de leur whitepaper. Un délai excessivement court et qui va a l'encontre des pratiques utilisées de nos jours par la majorité des firmes de recherches. Historiquement la question du délai entre le moment ou l'on prévient un constructeur d'une faille et le moment ou elle est rendue publique a toujours été un point de contention entre les chercheurs et failles et les sociétés informatiques. Les constructeurs ont longtemps abusé de la bonne volonté des chercheurs pour étendre au maximum cette durée qui se comptaient longtemps en mois. Google, via son Project Zero, a tenté d'imposer un standard de 90 jours, contesté par nombre de sociétés comme trop court mais qui nous semble être dans l'intérêt général. Le délai de 24 heures dénote donc assez fortement et ne nous semble pas particulièrement "responsable".

La lecture du whitepaper montre qu'il n'est pas non plus neutre dans sa rédaction (on est loin des standards utilisés par Google), quelque chose que l'on ressent également sur le site, le choix du nom de domaine (amdflaws.com), la présence d'une vidéo, ou le fait que ces failles de sécurités renvoient en bas de page vers une agence de relations presse. Dès l'introduction on trouve ce passage par exemple :

"We urge the security community to study the security of these devices in depth before allowing them on mission-critical systems that could potentially put lives at risk."

Dans le cas d'ASMedia, les failles sont présentées comme des backdoors et la conclusion est quelque peu lapidaire :

"This can allow attackers to bury themselves deep within the computer system and to potentially engage in persistent, virtually undetectable espionage, executed from AMD's Secure Processor and AMD's chipset."

La section "Legal disclaimer" à la fin de l'article contient également cette phrase qui n'est pas habituelle dans ce type de communication :

"Although we have a good faith belief in our analysis and believe it to be objective and unbiased, you are advised that we may have, either directly or indirectly, an economic interest in the performance of the securities of the companies whose products are the subject of our reports."

Ce type de mention d'intérêt financier direct ou indirect est surprenant (il n'est pas interdit de publier des "recherches négatives" tout en pariant à la baisse sur le cours d'une action dans la loi américaine), mais la raison pour laquelle on le mentionne est que la publication du whitepaper a été accompagnée, seulement une heure après, par un autre whitepaper de 25 pages (!) d'une société de recherche baptisée Viceroy Research . Sous le nom "AMD - The Obituary" ("l'éloge funèbre"), ils concluent ainsi (on vous passe le reste) :

"In light of CTS's discoveries, the meteoric rise of AMD's stock price now appears to be totally unjustified and entirely unsustainable. We believe AMD is worth $0.00 and will have no choice but to file for Chapter 11 (Bankruptcy) in order to effectively deal with the repercussions of recent discoveries."

Un élément relayé par la presse financière (non sans circonspection) par exemple dans cet article de Bloomberg qui pointe une augmentation significative des options à la baisse sur le titre d'AMD. Bloomberg rappelle que Viceroy Research est considéré comme un short-seller (voir cet article relayé par un lecteur d'Hacker News sur cette particulière société).

Le cours de l'action d'AMD n'a pas particulièrement réagi a la publication de ces informations hier, même si l'action du constructeur est en légère baisse (-1.1%) a l'ouverture aujourd'hui au moment ou nous écrivons ces lignes.

AMD de son côté n'a pas encore réellement communiqué sur le sujet, se contentant simplement d'un billet de blog sur son site réservé aux investisseurs :

"We have just received a report from a company called CTS Labs claiming there are potential security vulnerabilities related to certain of our processors. We are actively investigating and analyzing its findings. This company was previously unknown to AMD and we find it unusual for a security firm to publish its research to the press without providing a reasonable amount of time for the company to investigate and address its findings. At AMD, security is a top priority and we are continually working to ensure the safety of our users as potential new risks arise. We will update this blog as news develops."

Nouvelle faille de sécurité de l'Intel ME !

Pour la troisième fois cette année, Intel vient d'annoncer une nouvelle série de failles qui touche son système Management Engine. Pour rappel, l'Intel Management Engine est basé sur un coprocesseur indépendant et un firmware (basé sur le microkernel MINIX comme s'en émouvait son créateur, Andrew S. Tanenbaum, qui interpellait il y a quelques jours Brian Krzanich pour le manque de courtoisie de la société).

Ce système fait ainsi tourner un certain nombre de modules , certains optionnels et livrés avec certains modèles de chipset uniquement (comme les fonctionnalités iAMT qui visent la gestion des parcs informatiques d'entreprise), d'autres non (la validation du processeur, chipset et microcode par exemple, ou des vecteurs d'implémentation de DRM comme le PAVP et SGX). Le propre du ME est d'être fonctionnel en permanence (du moment que la carte mère est alimentée), d'avoir un accès total au système et de ne pas être désactivable par l'utilisateur, ce qui en fait un vecteur d'attaque particulièrement dangereux en cas d'accès au kernel MINIX.

Un tweet il y a deux semaines de cela avait montré une faille de la sorte avec un accès complet obtenu en mode local via un port USB. Cette faille est l'une de celle corrigée aujourd'hui par Intel dans sa mise à jour (il y en a d'autres dont une avec accès distant mais qui nécessite une authentification locale, même si elles sont jugées moins importantes). Contrairement à certaines failles pointées plus tôt qui ne touchaient que les systèmes utilisant les modules AMT, cette faille touche tous les systèmes Intel à partir de la génération Skylake (ME version 11) qui sont donc tous potentiellement vulnérables (l'implémentation actuelle présentée requiert l'activation du mode USB DCI dans le BIOS).

Pour pouvoir s'en prémunir, il faudra passer par une mise à jour de BIOS (certaines mises à jour de BIOS peuvent inclure une mise à jour du ME, quelque chose de généralement optionnel sur la plupart des cartes mères modernes qui vous proposent d'effectuer une mise à jour simple, ou également du ME), et donc qu'un BIOS existe pour sa plateforme ce qui ne sera pas le cas des plus anciennes qui ne sont plus supportées (par Intel ou les constructeurs de cartes mères). Tout au plus, Intel fourni un outil pour détecter la version du ME.

A défaut, ces utilisateurs pourront regarder du côté de me_cleaner qui tente de limiter au maximum la taille du firmware en désactivant la plupart des modules de l'IME, tout en gardant à l'esprit que cela ne résoudra pas la totalité des failles (comme la faille USB ci-dessus).

Ces failles de sécurité à répétition montrent les craintes légitimes que l'on peut avoir sur ce système implémenté par Intel sur toutes ses plateformes et le côté quelque peu trivial avec lequel le constructeur adresse les failles qui le touche. Contrairement au microcode des CPU, diffusable à grande échelle par Intel via des mises à jour de BIOS mais aussi des mises à jour des systèmes d'exploitation, la mise à jour du ME est beaucoup plus complexe. Elle requière au minimum la collaboration de deux acteurs, Intel et un OEM (dont les pratiques de suivi des mises à jour peuvent être variables, particulièrement dans le monde des PC portables), ainsi qu'une action non triviale de l'utilisateur. Ce n'est pas une pratique que l'on peut légitimement accepter pour un tel niveau de criticité.

Il faut enfin noter que si Intel est pointé (une nouvelle foi et à raison) du doigt, en grande partie par son obscurantisme durant des années sur les capacités réelles de l'IME, les dernières plateformes d'AMD disposent aussi d'un système équivalent, et pas plus documenté (on sait tout au plus qu'il s'agit d'une implémentation/variante du Trustzone d'ARM ) via son PSP qui n'est pas non plus désactivable.

10/7nm en avance pour TSMC, EUV pour le 5nm

TSMC vient de publier ses résultats financiers pour le troisième trimestre. Le fondeur taiwannais enregistre une hausse séquentielle de 17% (+22% par rapport à la même période sur 2015), au dessus de ses prévisions. Des bons chiffres qui s'expliquent selon TSMC par une forte demande sur le marché des smartphones.

Ramenés par process, le 16/20nm représente 31% des revenus de la société (contre 23% le trimestre précédent). Le 28nm voit sa part baisser à 24% des revenus, mais TSMC confirme que ses usines restent "pleinement utilisées".

En ce qui concerne les prochains nodes, TSMC a confirmé les informations publiées un peu plus tôt, à savoir l'avance prise par les process 10 et 7nm.

Le 10nm entre en production ce trimestre et les premiers produits finaux seront livrés au premier trimestre 2017. Ce node ne sera pour rappel utilisé que par les très gros clients de TSMC, à savoir Apple et possiblement Qualcomm. Les autres clients attendront le 7nm. La montée des yields est décrite comme "similaire" à celle du 16nm même si "techniquement plus difficile".

Le 7nm entrera en production "risque" au premier trimestre 2017 et TSMC s'empresse d'indiquer qu'il sera utilisé non seulement pour les smartphones, mais aussi pour des GPU, des puces serveurs, et des "PC et tablettes". TSMC décrit des tapeout aggressifs qui commenceront au début du second trimestre. 15 produits devraient être qualifiés en 2017.

La fondeur a également évoqué le 5nm, qui a quitté le stade de la recherche pure pour entrer dans une phase de développement. Et TSMC confirme qu'ils utiliseront de manière "extensive" la lithographie EUV. Cette dernière aurait fait des progrès sur tous les plans, que ce soit en fiabilité, ou sur les problèmes techniques complexes (masques, photo resist, etc). La production "risque" reste prévue pour la première moitié de 2019 (la production volume suit en général de 3 à 4 trimestres).

Lors de la présentation des résultats aux analystes financiers, le CEO de TSMC, Mark Liu, a réitéré une fois de plus voir "l'informatique haute performance" comme un marché sur lequel TSMC espère voir une progression de ses ventes. Les serveurs et les PC clients sont mis en avant, et on a du mal a ne pas y voir un lien avec les annonces d'AMD sur sa renégociation du contrat WSA qui les lie à GlobalFoundries.

Dans la séance de questions/réponses posées, on notera qu'a la question de savoir si la prise de licence ARM par Intel est un risque, Mark Liu estime surtout que cela renforce le rôle d'ARM, tout en ne négligeant pas le rôle qu'Intel pourrait jouer. Reste que sur ce trimestre, la part de marché de TSMC chez les fondeurs (hors activité propre comme Intel pour ses propres puces donc) était de 55%.

Hot Chips : M1, SVE, Parker, InFo et Skylake !

La conférence Hot Chips qui se tenait la semaine dernière a donné lieu a d'autres annonces intéressantes que nous avons essayé de regrouper dans cette actualité !

Rajouter des tiers de mémoire côté serveur

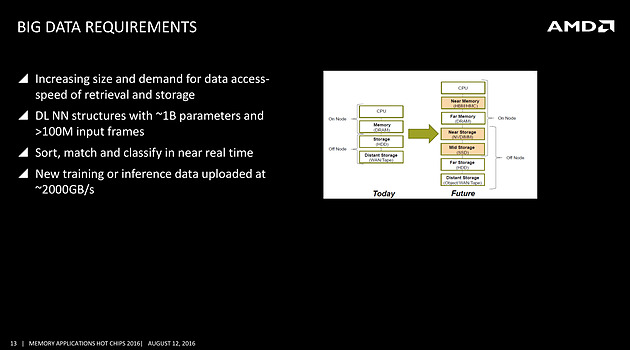

On avait déjà noté un peu plus tôt la volonté de rajouter de la mémoire HBM à divers endroits, et même la volonté de Samsung de travailler sur une version moins onéreuse, mais l'on rajoutera ce slide issu d'une présentation d'AMD qui rappelle les objectifs de la société côté serveurs, prenant pour le coup l'exemple du big data

On s'attardera sur le graphique à droite qui pointe l'ajout d'une mémoire intermédiaire côté CPU, type HBM ou HMC (AMD misera plutôt sur la HBM pour les déclinaisons serveurs de Zen), et aussi l'utilisation de NVDIMM pour s'intercaler avant un SSD. Il faudra attendre encore un peu pour voir comment seront déclinées ces technologies, mais il est intéressant de noter la manière dont les avancées côté mémoire sont mises en avant, parfois un peu trop tôt comme l'a fait Intel avec 3D XPoint, dans toute l'industrie.

Quelques détails de plus sur SVE

Chez ARM, outre une présentation de Bifrost côté GPU dont on vous avait déjà parlé, l'annonce principale concernait SVE, la nouvelle extension vectorielle introduite par la société.

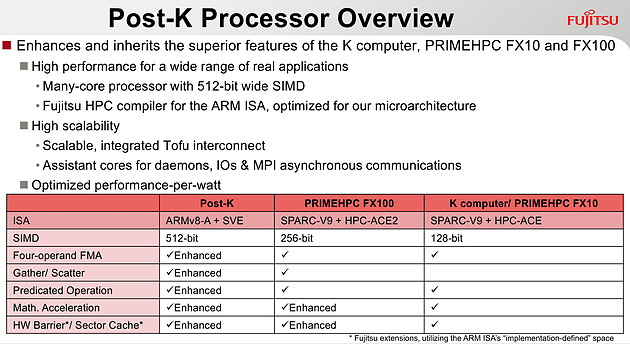

Le premier partenaire annoncé par ARM est Fujitsu, qui mettra au point des processeurs ARMv8 avec extension SVE pour le futur supercalculateur japonais Post-K. Fujitsu a donné quelques détails, indiquant par exemple que les unités vectorielles auraient une largeur de 512 bits sur ses puces.

Chez ARM, le constructeur présente plusieurs benchmarks assez théoriques, on notera surtout sur les barres grises les améliorations qui ont été effectuées côté auto-vectorisation, c'est a dire la capacité du compilateur à utiliser des instructions vectorielles pour extraire du parallélisme. ARM devrait proposer dans les semaines qui viennent des patchs pour les différents compilateurs open source, incluant LLVM et GCC.

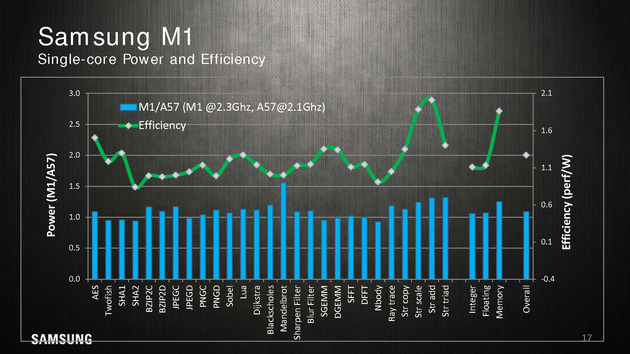

Le Samsung M1, un timide premier pas

La particularité de l'écosystème d'ARM est que les partenaires peuvent soit utiliser des coeurs "clefs en main", développés par ARM (les gammes Cortex, comme par exemple le Cortex A57), ou créer leurs propres implémentations de l'architecture ARM (qui restent compatibles, tout en étant différentes, à l'image des processeurs d'AMD et d'Intel qui diffèrent bien que restant compatibles). Plusieurs sociétés disposent de licences "architecture" qui permettent de créer ces puces, Apple étant jusqu'ici la société la plus à la pointe sur armv8 même si de nombreuses sociétés proposent tour à tour leurs architectures.

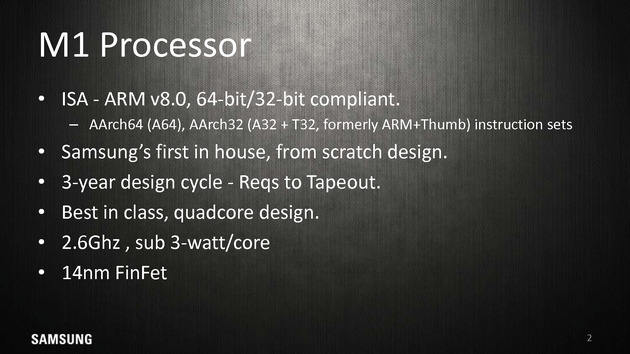

Parmi les nouveaux venus, il y a Samsung qui s'est lancé lui aussi dans le design d'une architecture armv8 custom pour ses Exynos M1. A la tête du projet, on retrouve Brad Burgess qui était architecte chez AMD pour les Bobcat. Il aura même été rejoint un court instant par Jim Keller (K8 chez AMD, A7 chez Apple, puis Zen chez AMD), qui n'est cependant pas resté très longtemps chez Samsung et qui n'aura probablement pas eu un grand impact. Le projet aura nécessité trois années, et en soit arriver a produire quoique ce soit du premier coup en un temps si court est un exploit.

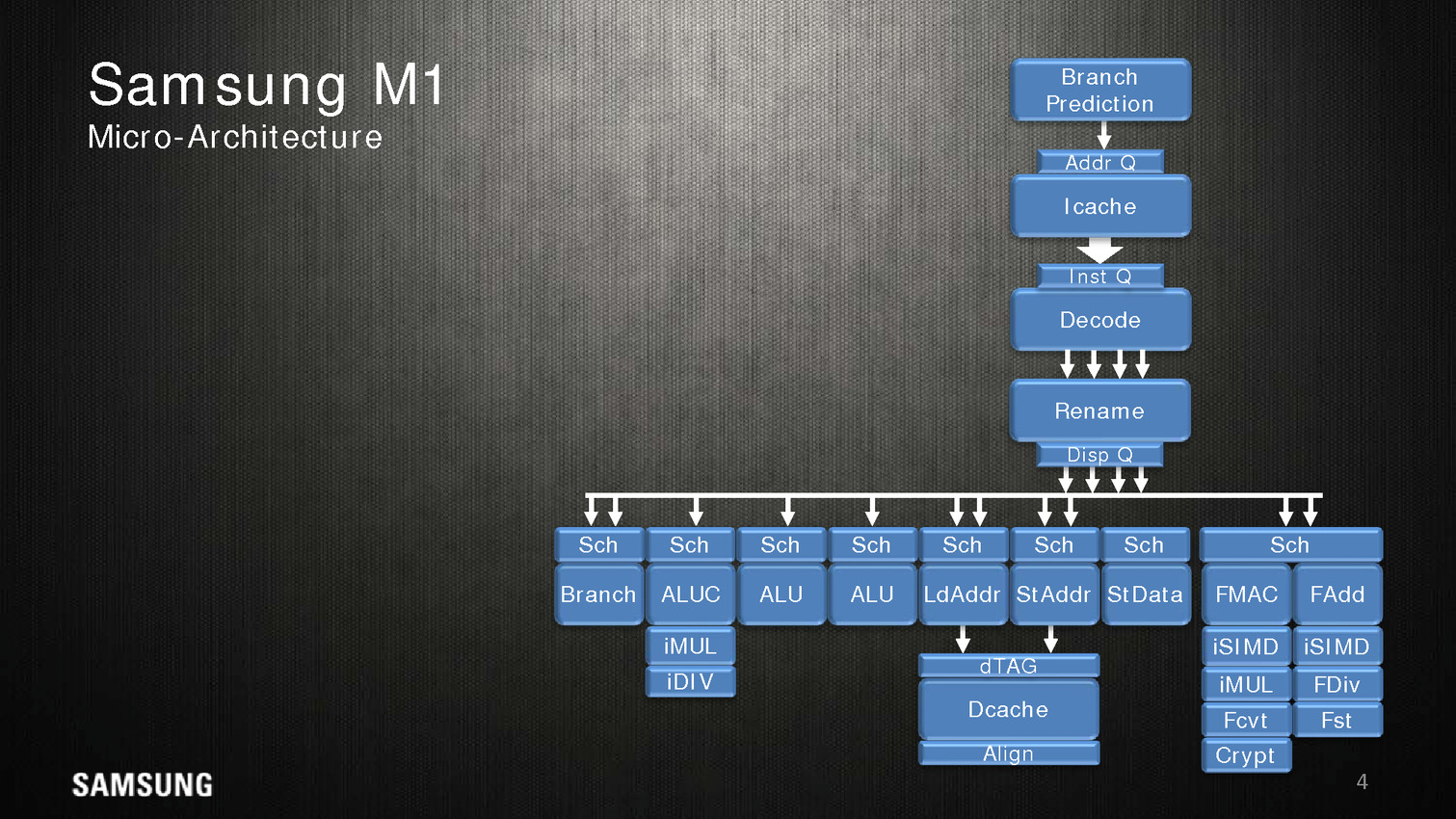

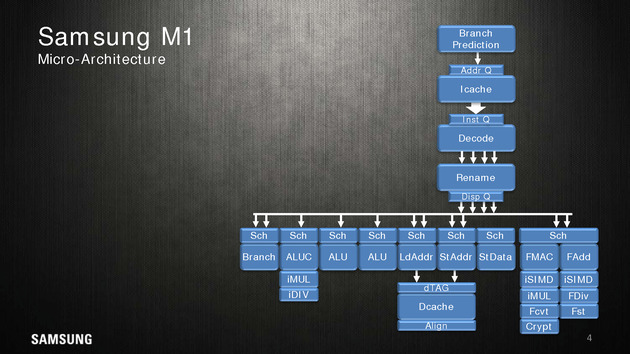

Côté architecture, Samsung indique utiliser un perceptron (un réseau de neurones simple) au niveau de ses mécanismes de prédiction de branches. Deux branches sont considérées par cycle, mais il est difficile d'estimer quoique ce soit sur l'éventuelle efficacité.

Quatre instructions peuvent être décodées/dispatchées par cycle aux unités d'exécutions qui sont regroupées sur sept files. On note deux files dédiées aux écritures mémoires, trois aux opérations mathématiques simple (avec un port sur lequel sont ajoutés les multiplications/divisions) et une aux branchements. Les opérations en virgules flottantes sont regroupées séparément avec un scheduler unique pour deux files. Samsung annonce 5 cycles pour effectuer une opération FMA.

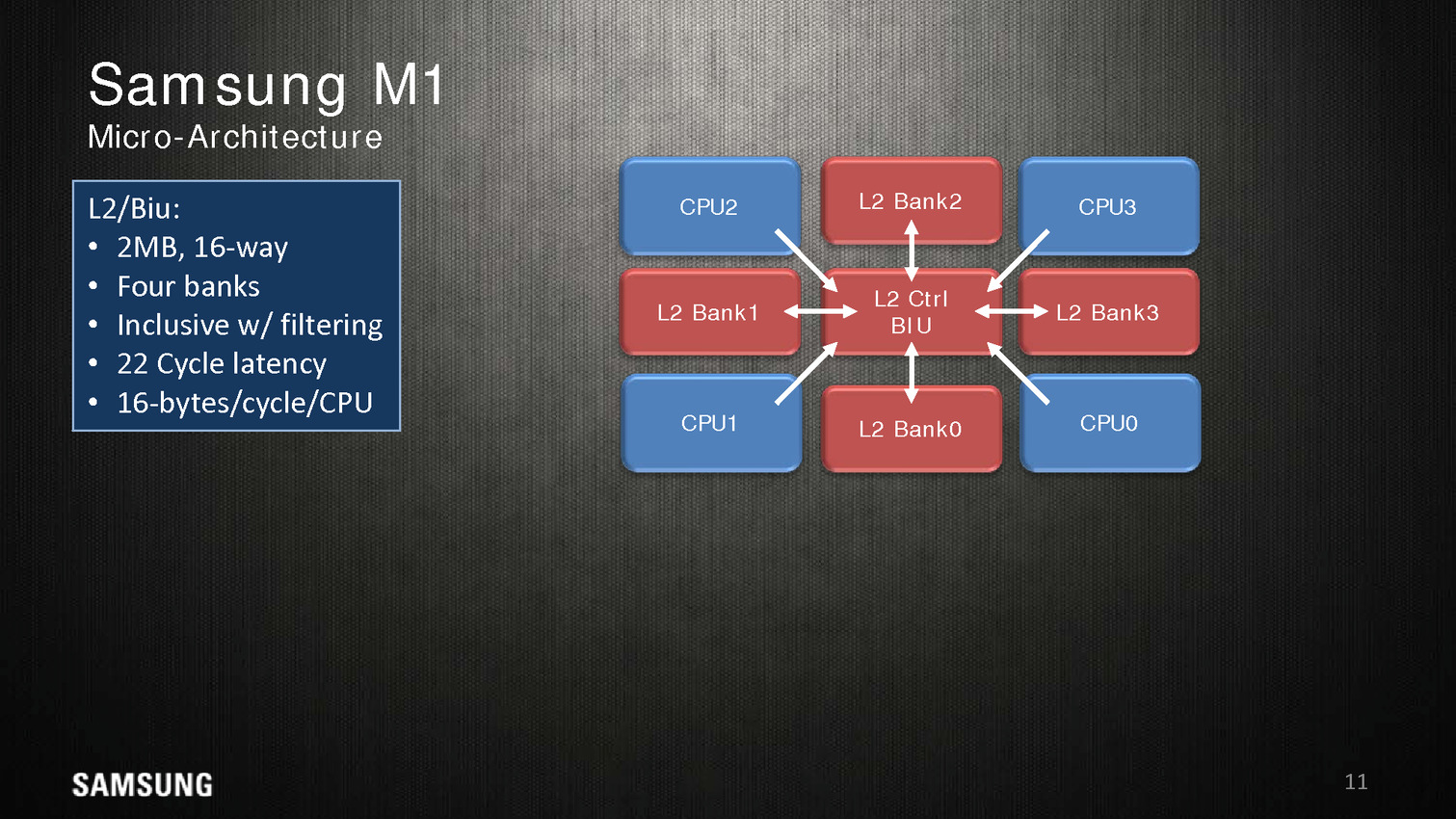

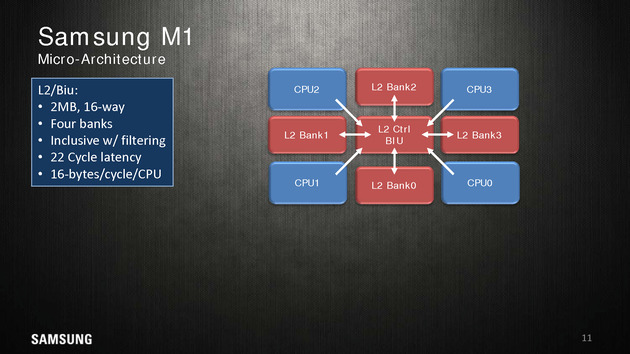

Dans une configuration quatre coeurs, le M1 dispose de 2 Mo de cache L2 coupé en quatre blocs, les coeurs accèdent au L2 via une interface commune. On appréciera aussi les schémas très spécifiques que propose Samsung, pas vraiment avare de détails techniques.

Reste qu'en pratique, les benchmarks mis en avant par Samsung ne sont pas forcément très convaincants. Avec 200 MHz de plus, sur un coeur, un M1 propose 10% de performances en plus qu'un Cortex A57 à consommation égale, ce qui est tout de même très peu. Samsung fait beaucoup mieux sur les opérations mémoires (c'est relativement facile, on l'a évoqué de nombreuses fois, les contrôleurs mémoires ARM ne sont pas particulièrement véloces/adaptés aux hautes performances), mais n'en tire pas particulièrement profit hors des benchmarks théoriques.

La présentation se termine en indiquant que ce n'est qu'un premier pas pour Samsung et que d'autres designs sont en cours d'élaboration. En soit si les performances ne vont pas révolutionner le monde des SoC ARM, Samsung a au moins une base de travail qu'ils pourront faire évoluer par la suite. A condition évidemment que Samsung continue d'investir sur le sujet dans les années à venir !

Les curieux pourront retrouver la présentation en intégralité ci dessous :

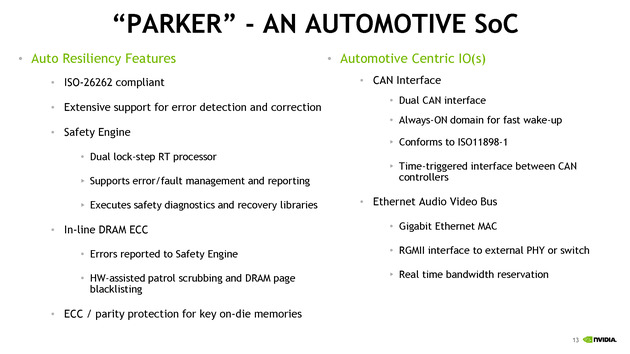

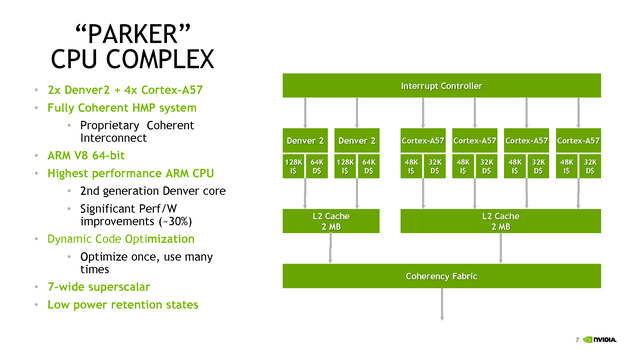

Parker/Denver 2 : design asymétrique

Nvidia était également présent à Hot Chips, donnant quelques détails sur son futur SoC baptisé Parker. Ce dernier est annoncé comme crée spécifiquement pour le marché automobile avec des fonctionnalités dédiées à ce marché. On ne sait pas si le constructeur le déclinera en d'autres versions plus génériques.

Les détails techniques ne sont pas particulièrement nombreux, on notera côté SoC que l'encodage 4K est désormais accéléré à 60 FPS, que l'on peut contrôler jusque trois écrans en simultanée, et que le contrôleur mémoire passe sur 128 bits (contre 64 précédemment). Côté GPU, Parker utilisera une version dérivée de son architecture Pascal.

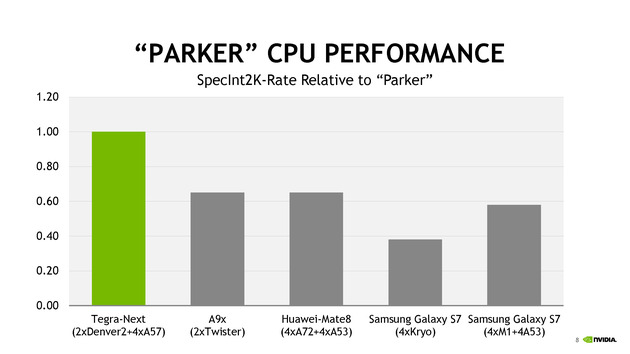

C'est du côté CPU que les choses sont les plus originales, après avoir utilisé son architecture Denver sur les TK1, puis être revenu aux Cortex A57 sur les TX1, Nvidia propose une architecture asymétrique avec deux coeurs "Denver 2" (sur lesquels aucun détail n'aura été donné, à part un gain performance/watts de 30% donné sans précision sur les process comparés) et quatre coeurs Cortex A57. Ce n'est pas la première fois que l'on voit des configurations originales, durant Hot Chips, le taiwannais MediaTek présentait un SoC 10 coeurs avec quatre coeurs Cortex A53 à 1.4 GHz, quatre coeurs Cortex A53 à 2 GHz, et deux coeurs Cortex A72 à 2.5 GHz !

Dans le cas de MediaTek, l'idée est de proposer différentes options à différents niveaux de consommation. Pour ce qui est de Nvidia, le choix est différent, le Cortex A57 étant "haute performance" contrairement aux A53 de MediaTek. Il faut dire surtout que le marché visé, l'automobile, n'a pas les mêmes contraintes de consommation que le marché mobile. Reste que Nvidia se doit de gérer cette asymétrie avec un scheduler qui doit décider sur quel coeur placer les threads, ce qui n'est pas particulièrement simple. On notera que chaque groupe de coeurs dispose de son propre cache L2 de 2 Mo.

Côté performances, Nvidia avec ses 6 coeurs se présente comme moitié plus rapide qu'un A9X d'Apple en deux coeurs. Le graphique mélangeant des puces à TDP différents (on y retrouve des puces pour smartphones et pour tablettes), on admettra que la comparaison n'est pas faite à TDP identique.

TSMC parle de ses packages InFo

Une des nouveautés présentées cette année par TSMC est la disponibilité d'un nouveau type de packaging, l'InFo-WLP. L'idée est de permettre de relier plusieurs dies en les "moulant" dans un substrat commun très fin qui contient également les interconnexions entre les puces. Il s'agit d'une version à cout beaucoup plus faible que les interposer (utilisés par exemple par AMD pour Fiji).

La présentation de TSMC est dédiée aux interconnexions entre les puces, et présente une puce 16nm reliant un SOC à une puce mémoire avec une bande passante de 89.6 Go/s sur 256 bits, le tout avec une consommation très réduite.

En plus de la solution présentée qui évoque le cas simple d'une puce mémoire et d'un Soc, TSMC évoque la solution comme permettant un jour de relier également plusieurs dies de logique, par exemple des groupes de coeurs séparés, pour réduire le coût de fabrication des puces (qui augmentent exponentiellement avec la taille des dies).

La présentation est technique mais reste intéressante, l'InFo-WLP ouvre des opportunités supplémentaires pour réaliser des produits qui mélangent processeur et mémoire. Le coût réduit et la finesse de l'interconnexion fait qu'on pourrait retrouver assez rapidement cette technique utilisée, y compris sur le marché mobile. Les prochains SoC d'Apple pourraient par exemple utiliser un tel package.

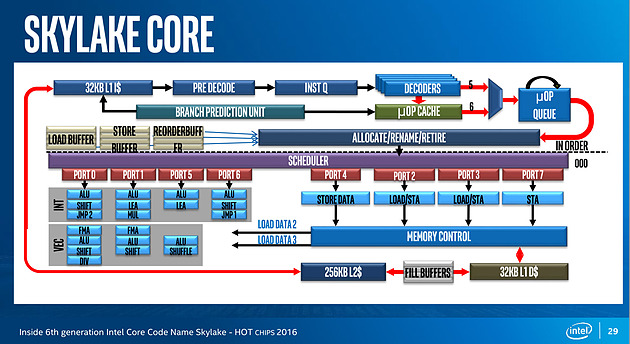

Et Skylake !

Juste avant la présentation de Zen, Intel proposait aussi une présentation de son architecture Skylake, lancée l'année dernière. Si la majorité du contenu est déjà connu, on aura noté un détail intéressant : un diagramme sur les unités d'exécution de Skylake. On rappellera que l'année dernière durant l'IDF, Intel nous avait promis plus de détails sur le sujet, sans jamais nous les donner !

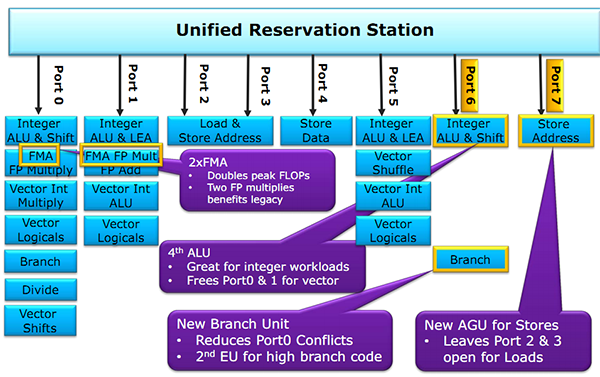

Pour rappel, voici la répartition sur Haswell :

Récapitulatif des ports/unités d'exécution sur Haswell

Un an après, voici enfin un diagramme similaire pour Skylake :

Conformément à ce que nous avaient indiqué les ingénieurs d'Intel l'année dernière, le nombre d'unité a bel et bien augmenté. Le nombre de ports reste constant, à 8, mais l'on compte... une nouvelle unité. Sur le port 1, Intel a en effet ajouté une unité de shift vectorielle. Pour le reste, la répartition reste similaire à celle d'Haswell. Un mystère enfin élucidé !