Les contenus liés au tag SK Hynix

Afficher sous forme de : Titre | Flux128 Go en DDR4 chez SK Hynix

Hybrid Memory Cube Gen2 en développement

CES: La GDDR5M victime des déboires d'Elpida

Le prix de la DDR3 remonte, une baisse en mars ?

Micron abdique contre Rambus

Samsung 1er du SSD avec 1/3 du marché

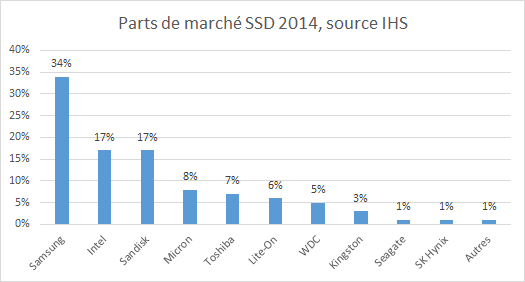

Selon les estimations du cabinet IHS publiées par ZD Net , Samsung est resté de loin le numéro un du SSD en 2014 avec 34% du marché mondial. Il est suivi par Intel et Sandisk qui se partagent chacun 17%, puis de Micron à 8%, Toshiba à 7%, Lite-On à 6%, WDC à 5%, Kingston à 3% et Seagate et SK Hynix à 1% chacun.

Nous ne disposons pas des estimations d'IHS pour les années précédentes, mais selon un autre institut (Gartner) le géant coréen était à 28,5% en 2013 contre 23,2% en 2012. Intel serait également en progression si un compare ces données après une baisse de 14,7% en 2012 à 13,1% en 2013 alors que Sandisk poursuit une croissance forte puisqu'il était à 5% en 2012 et 11,7% en 2013. Micron était pour sa part à 3,3% en 2012 et 6,9% en 2013, contre 9,2% et 5,6% pour Toshiba.

3D NAND 48 couches chez Toshiba

Toshiba vient d'annoncer avoir produit des puces mémoires flash (NAND) à construction verticale (souvent appelée 3D NAND) à 48 couches. Pour rappel, en 2007 Toshiba avait été le premier à produire une technologie de mémoire ou l'organisation des cellules se fait non plus de manière horizontale comme traditionnellement, mais cette fois ci de manière verticale.

La mémoire NAND traditionnelle au milieu en haut peut être empilée (Stack), la stratégie classique que l'on voit à droite, ou bien transposée verticalement (le chemin de gauche) pour réaliser une structure appelée BiCS par Toshiba qui peut être vue comme le pendant du FinFET pour la NAND

En 2007, Toshiba ne précisait pas le nombre de couches qu'il avait réussi à superposer dans sa structure mais évoquait dans son communiqué de presse le nombre de 32 pour expliquer les difficultés de l'empilement. Presque huit années après, le constructeur indique aujourd'hui avoir produit des puces 48 couches de 128 Gbits (16 Go) qui sont disponibles dès aujourd'hui sous la forme d'échantillons.

Toshiba indique également qu'il commercialisera cette mémoire à partir de 2016, elle sera fabriquée en volume dans la nouvelle Fab2 située à Yokkaichi au Japon. En 2014, Toshiba avait annoncé remplacer cette ancienne usine par une nouvelle qui serait capable de produire de la mémoire NAND classique et « 3D » à compter de 2016. Le communiqué de la marque indique que la Fab2 devrait être opérationnelle durant la première moitié de 2016.

Cette structure de mémoire permet théoriquement d'augmenter fortement la densité même si pour l'instant, il faut se contenter de puces 128 Gbits pour ce premier échantillon. On rappellera que si Toshiba a été pionnier de cette technologie, Samsung avait été le premier à lancer la production de sa propre version de mémoire NAND verticale, baptisée V-NAND en 2013. Si l'agencement technique semblait légèrement différent du BiCS de Toshiba (voir notre article), le principe de base reste le même.

Cette V-NAND s'est ainsi retrouvée dans les SSD 850 Pro du constructeur sous la forme de puces empilant 32 couches. De son côté, si Toshiba met en avant l'empilement de 48 couches, on ne connait pas encore la finesse de gravure qui sera utilisée. Plus de détails seront probablement dévoilés d'ici à l'année prochaine. Pour le reste de la concurrence, Intel et Micron devraient proposer leur version 3D NAND 32 couches au second semestre 2015, tandis qu'il faudra attendre 2016 pour Hynix.

La HBM 128 Go /s fait bien 1 Go, quid d'AMD Fiji ? MAJ

Ce contenu a été actualisé le 23/02/2015 après une première publication le 20/02/2015

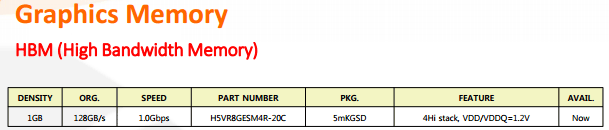

Depuis le troisième trimestre 2014, le catalogue mémoire SK Hynix fait mention de mémoire HBM (High Bandwith Memory). La dernière version de ce catalogue corrige une erreur qui était présente jusqu'alors, la capacité de cette puce HBM est bien de 1 Go et non 1 Gb (soit 128 Mo).

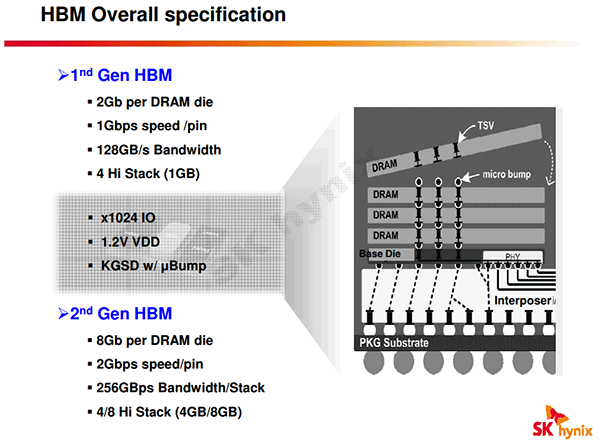

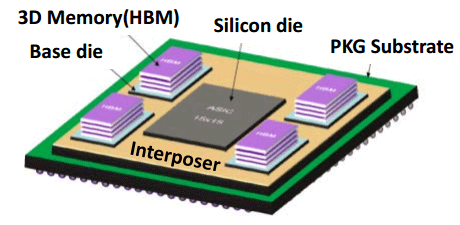

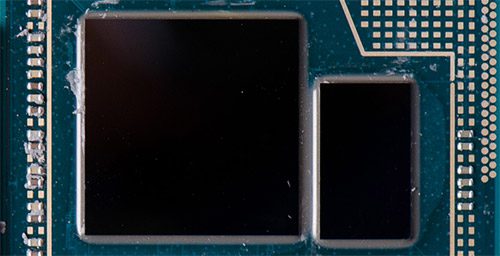

Pour rappel ce type de mémoire est composé d'un die logique de contrôleurs mémoire ainsi que de multiples dies de mémoire, ici 4, le tout étant relié les uns aux autres par des TSV (Through Silicon Vias), littéralement de petits trous dans les puces pour laisser passer des fils afin de connecter les dies entre eux.

L'avantage de la HBM se situe au niveau de la bande passante sur une même puce du fait d'un bus externe très large de 1024-bit. Malgré une vitesse de seulement 1 GT/s, cela permet à la H5VR8GESM4R-20C d'atteindre 128 Go /s. A titre de comparaison, une puce GDDR5 à 8 GT/s en 32-bit atteint 32 Go /s, mais sur les cartes graphiques plusieurs puces sont adressées en parallèle sur un bus de 128 à 512-bit, ce qui permet d'atteindre en théorie jusqu'à 512 Go /s.

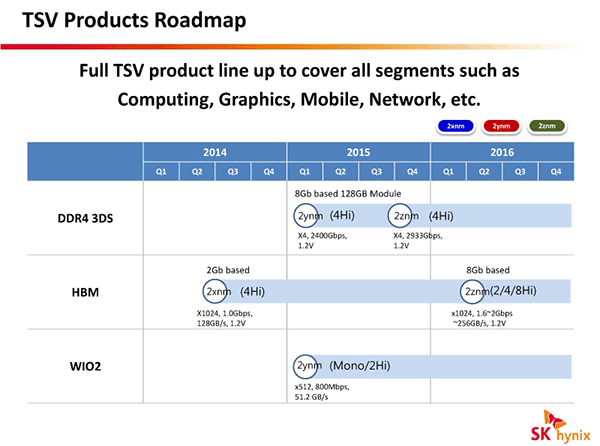

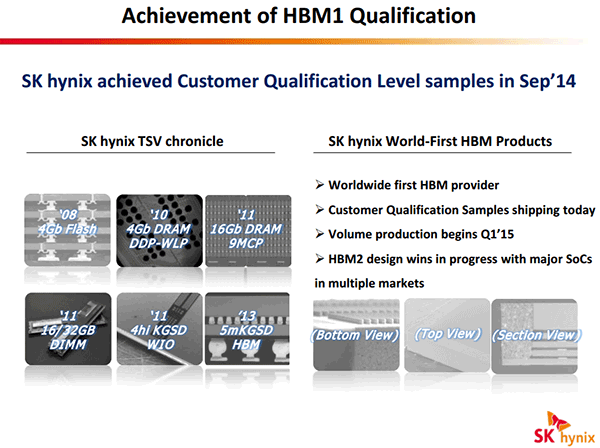

Si la HBM Hynix est affichée depuis le troisième trimestre 2014 comme disponible sur son catalogue, il s'agit de plus probablement d'une erreur puisque dans une présentation datée d'octobre ce dernier indiquait avoir débuté l'échantillonnage pour qualification auprès de ses clients en septembre 2014 avec une production en volume lancée au premier trimestre 2015.

Les rumeurs vont bon train sur Internet concernant l'utilisation de HBM par le prochain GPU haut de gamme d'AMD, Fiji, dont on attend l'arrivée pour la mi-2015. Celles-ci ont parfois tendance à s'auto-alimenter comme c'est souvent le cas sur le net, autant faire un point sur le sujet. En premier lieu elles ont eu pour source le fait que la HBM est un standard JEDEC initialement co-développé par AMD et SK Hynix, AMD ayant été historiquement très actif dans dans le domaine de la mémoire graphique et d'ailleurs le premier à utiliser la GDDR5, et que la production en volume de la première génération est donc imminente chez SK Hynix. S'ajoute à ceci quelques rapports Sandra (certains datant d'Octobre ) mentionnant un GPU à 64 CU et bus 4096-bit. Enfin en début d'année 2015 un ingénieur AMD avait indiqué sur sa fiche LinkedIn qu'il avait participé au développement d'un GPU 300W "2.5D" utilisant de la HBM et un silicon interposer.

Ce faisceau d'indice qui grossit est-il suffisant pour envisager l'utilisation de HBM dès Fiji avec certitude ? Pas complètement. Tout d'abord, AMD est loin d'avoir utilisé toutes les capacités de la GDDR5 jusqu'alors puisqu'il ne fait appel qu'à de la GDDR5 à 5 GT/s sur les R9 290X. Avant de partir sur la HBM, il dispose donc d'une marge de manuvre côté bande passante en conservant un bus 512-bit GDDR5, avec de la mémoire pouvant être 40% plus rapide en configuration 4 Go (16x256 Mo à 7 GT/s) et 60% plus rapide en 8 Go (16x512 Mo à 8 GT/s). Au mieux on pourrait ainsi atteindre 8 Go à 512 Go /s.

Si cette première génération de puces HBM est une étape importante, la combinaison de sa capacité et de son débit fait que son utilisation sur un GPU haut de gamme ne semble pas être si pertinente qu'elle peut y paraître au premier abord. Les rumeurs font ainsi état d'un énorme bus 4096-bit sur Fiji, mais cela ne permettrais finalement "que" d'adresser 4 puces HBM en parallèle et d'atteindre donc une capacité de 4 Go à une vitesse de... 512 Go /s. Quel est l'intérêt de partir sur une technologie qui en est encore à ses débuts, avec les surcoûts et risques que cela induit, si la bande passante n'augmente pas alors que la mémoire vidéo est bloquée à 4 Go, ce qui peut poser des problèmes notamment pour une déclinaison FirePro ?

L'efficacité énergétique de cette HBM de 1ère génération est supérieure à celle de la GDDR5 pour une telle bande passante, mais il n'est pas certain que ce soit un avantage décisif par rapport à la gourmandise d'un GPU haut de gamme. Les watts de gagnés au niveau des contrôleurs mémoire pourront être utilisés pour pousser plus loin le reste du GPU, mais en contrepartie les puces mémoire seront positionnées au niveau du packaging GPU ce qui va complexifier le refroidissement du tout. Est-ce pour cette raison, en sus des 300W mentionnés plus haut, que AMD envisagerais selon la rumeur de faire appel à un watercooling AIO pour Fiji ?

D'autres bruits de couloir font par ailleurs état d'une exclusivité d'AMD sur la HBM auprès de SK Hynix sur cette première génération, et il est possible que AMD souhaite dans tous les cas l'utiliser ne serait-ce que pour l'aspect marketing, voire soit obligé contractuellement d'acheter la HBM de 1ère génération à SK Hynix.

C'est surtout la seconde génération de HBM qui devrait s'imposer sans discussion possible sur les GPU haut de gamme. Les débits seront alors doublés, avec 256 Go /s par puce, et les capacités atteindront 4 et même 8 Go par puce... multipliez par 4 et les chiffres font rêver ! Alors que la GDDR5 pourrait suffire pour les GPU haut de gamme de 2015 si elle est pleinement exploitée, la HBM deviendra par contre essentielle pour tirer pleinement parti du saut de puissance attendu en 2016 avec l'arrivée du 14nm.

Une utilisation de la HBM de 1ère génération par Fiji est bien entendu possible, mais dans ce cas nous sommes impatients de savoir ce qui le justifiera par rapport à la GDDR5. Quoi qu'il en soit nous préférons ne pas avoir d'attente particulière côté mémoire et être agréablement surpris, par exemple avec une HBM qui serait plus rapide que ce qu'annonce Hynix à son catalogue (un des rapports Sandra parle de "1.25 GHz"), qu'être "déçus" si finalement Fiji se "contentait" de GDDR5... même si ce sont bien entendu les performances finales qui importent !

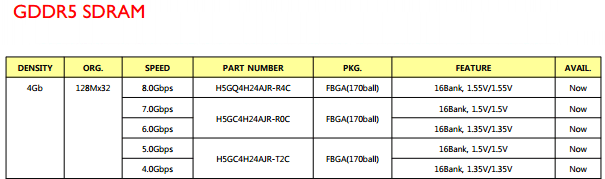

GDDR5 8 Gbps et HBM 128 Go /s chez Hynix

Dans son dernier catalogue destiné aux mémoires pour les puces graphiques, SK Hynix introduit une nouvelle GDDR5 à 8 Gbps soit 2000 MHz. La puce H5GQ4H24AJR-R4C est disponible en version 512 Mo et 32 bits, et offre seule une bande passante de 32 Go /s. Interfacée en 256 bits elle permet d'atteindre une bande passante de 256 Go /s contre 224 Go /s pour la GDDR5 7 Gbps qui prend place dans les GTX 970/980 par exemple.

Bien entendu une autre possibilité pour augmenter la bande passante mémoire disponible pour un GPU est d'augmenter la taille du bus, comme le fait AMD sur les R9 290/290X qui combinent de la mémoire à 5 Gbps et un bus 512 bits pour atteindre 320 Go /s.

On note également la présence de mémoire HBM (High Bandwith Memory), avec cette fois une puce de... 128 Mo seulement (1 Gbits) ! A l'instar de la mémoire HMC (Hybrid Memory Cube), ce type de mémoire est composé d'un die logique de contrôleurs mémoire avec de multiples dies de mémoire, ici 4, le tout étant relié les uns aux autres par des TSV (Through Silicon Vias). Cette mémoire fonctionne a seulement 1 Gbps mais avec un bus 1024 bits, ce qui lui permet d'atteindre une bande passante pour une seule puce de 128 Go /s, 4 fois plus que la GDDR5 la plus rapide donc.

Si certains voient dans l'arrivée de la HBM au catalogue d'Hynix les prémices d'une association de la HBM avec des GPU AMD dès le 1er trimestre 2015, il faut temporiser ces ardeurs. Premièrement, la mémoire HBM n'est en fait pas nouvelle dans le catalogue Hynix, elle était déjà présente au troisième trimestre .

De plus, si AMD a effectivement collaboré avec SK Hynix au développement de la HBM, une puce de 128 Mo n'est pas assez dense pour être utilisée sur des GPU qui ont besoin de beaucoup plus de mémoire - il est plus qu'improbable d'avoir 16 à 32 puces HBM 1024 bits intégrées sur le packaging GPU ou sur le PCB ! Nvidia a déjà fait une présentation de sa génération de GPU Pascal prévue pour 2016 qui utilisera un type de mémoire proche, on pouvait voir 4 puces intégrées sur le packaging du GPU ce qui fait déjà un bus 4096-bit.

Toutefois la capacité annoncée pour cette puce HBM est en fait très étrange, SK Hynix a probablement fait une typo d'autant que la présence d'un "8G" dans la désignation fait penser à une capacité de 1 Go / 8 Gbits. C'est d'ailleurs de la HBM de 1 Go (4 die de 2 Gbits), atteignant également une bande passante de 128 Go /s avec un bus 1024 bits, qui a été qualifiée en septembre 2014 auprès des clients de SK Hynix, avec une production en volume devant débuter au cours du premier trimestre 2015 - on est donc loin de la disponibilité "Now" indiquée dans les catalogues des deux derniers trimestres. Courant 2016, une nouvelle génération de HBM doublera les débits alors que la capacité passera à 4 voir 8 Go (4 ou 8 die de 8 Gbits), mais on ne sait pas encore comment les fabricants de GPU utiliseront ces deux générations de HBM... est-ce qu'ils attendrons comme Nvidia le fait la seconde ou alors est-ce que AMD sautera le pas dès la première en 2015 ? L'avenir nous le dira !

Reste que si la puce de 128 Mo HBM qui est au catalogue de SK Hynix existe, elle sera pour sa part plutôt utile sur des APU en tant que cache externe, comme le fait déjà Intel sur les Haswell GT3e / Iris Pro 5200 qui intègrent sur leur packaging une puce d'eDRAM maison de 128 Mo interfacée en 512 bits et offrant une bande passante de 50 Go /s dans chaque sens, ce qui permet un gain de performance net vu la faible bande passante de la mémoire centrale (25,6 Go /s en DDR3-1600 sur deux canaux).

Résultats Micron, pour quand la baisse de la DDR3 ?

Micron a présenté ses résultats pour son dernier trimestre fiscal qui prenait fin le 27 février dernier, l'occasion de faire le point sur le marché de la mémoire en général. Pour ce trimestre, Micron a réalisé 4,107 milliards de $ de ventes avec une marge opérationnelle à 34,2% et un bénéfice net de 731 millions de $. Un an auparavant, les ventes étaient de 2,078 milliards seulement avec une marge de 17,6% et une perte nette de 286 millions de $.

Du côté de la DRAM la marge brute est dans l'intervalle 35-40%, en hausse de 5 points par rapport au trimestre précédent, Micron profitant de la montée des prix depuis l'incendie de l'usine de SK Hynix de Wuxi début septembre. Cette usine est désormais de nouveau opérationnelle mais les prix restent élevés, il faut par exemple compter 3,656$ pour une puce DDR3-1600 de 512 Mo contre 3,143$ début septembre mais 4,268$ au plus fort de la hausse.

Micron explique cette situation par des stocks qui restent faibles chez les OEM et fournisseurs et une baisse de la production par ailleurs, avec par exemple chez Micron un passage des lignes de production de Singapour de la DRAM vers la NAND. Micron semble confiant dans l'avenir avec notamment cette phrase :

Our outlook for memory industry conditions remains favorable. We believe the current industry structure is fundamentally changed and we can now manage our business focused on return based capital and supply decisions which was not always possible in the past.On peut clairement en déduire que les niveaux de marges des années passées sur la mémoire, parfois il est vrai trop faibles, font pour Micron partie du passé à ce jour et qu'il est désormais possible pour la société de se concentrer sur son retour sur investissement du fait de la "structure" de l'industrie il est a priori question ici de la concentration du marché DRAM dont 90% de la production est entre les mains de Micron - qui a racheté Elpida - SK Hynix et Samsung.

Pour les 5 années à venir, Micron estime que la production de DRAM devrait être stable en termes de wafer, avec une hausse de 20 à 30% par an du volume de bit du fait de l'amélioration des procédés de fabrication. Pour la NAND Micron prévoit une hausse de 35 à 45% par an sur la même période, avec une hausse plus importante sur 2014 et 2015 (40-45%).

Sur le dernier trimestre Micron a augmenté de 35% ses ventes de NAND, avec une hausse de 35% en unités compensées par une baisse de 18% des prix de vente moyen. Contrairement à la DRAM, la marge brute est en baisse de 5 points sur ce marché et s'établie entre 25 et 30%, sans plus de précisions. La baisse de la marge est donc contenue par rapport à la baisse de prix du fait d'une réduction du coût par bit produit du fait de la hausse de la part du 20nm ainsi que de réduction de coûts liés à l'augmentation de la production de NAND à Singapour.