Les contenus liés au tag SK Hynix

Afficher sous forme de : Titre | FluxLa lente baisse de la DDR3 est amorcée

SK Hynix produit en volume de la MLC 16nm

DDR3 : +34 à 44% depuis l'incendie chez Hynix

Incendie chez SK Hynix, le point

Mémoire en hausse suite à un incendie chez SK Hynix

128 Go en DDR4 chez SK Hynix

SK Hynix vient d'annoncer avoir développé une barrette mémoire DDR4 d'une capacité de... 128 Go ! Ce module Registered fait toujours appel à des die DDR4 de 1 Go chacun fabriqués en 20nm, la densité doublée par rapport aux modules précédents étant obtenus via l'utilisation du TSV (Through Silicon Via) pour empiler les die.

Cette barrette fonctionne en DDR4-2133 à 1.2v, actuellement en cours d'échantillonnage sa production en volume ne devrait toutefois pas démarrer avant le premier semestre 2015. Pour rappel Intel supportera la DDR4 à compter des Haswell-E, EP et EN prévus pour le second semestre 2014.

Hybrid Memory Cube Gen2 en développement

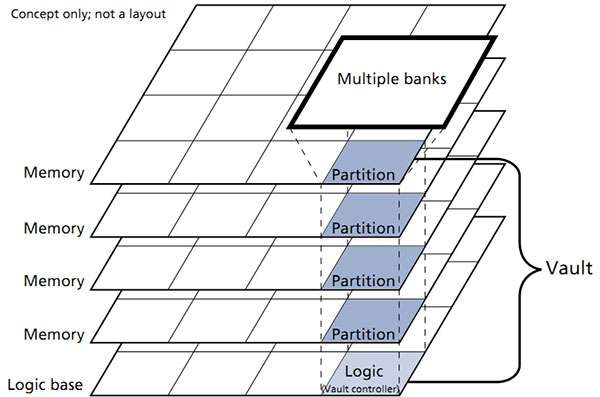

L'Hybrid Memory Cube Consortium (fondé par Micron et Samsung en 2011, rejoint ensuite par Hynix et 120 sociétés donc ARM, IBM, Microsoft et Xilinx) vient de publier un communiqué indiquant le développement d'une seconde génération de cette mémoire. Pour rappel, le concept de l'HMC est de superposer plusieurs dies de mémoire DRAM par-dessus une die de logique, le tout étant relié par des TSV (Through Silicon Vias, des fils qui traversent les dies).

Nous avions parlé un peu plus en détail de la première version de cette spécification en septembre dernier, nous vous renvoyons vers cet article si vous souhaitez plus de détails.

La nouvelle spécification est encore au statut de « draft » (en préversion) et n'a été pour l'instant partagé qu'avec les membres du consortium dans le but d'être finalisé en mai 2014. La nouvelle version de la spec évoque des augmentations de bande passante, en doublant à 480 Go/s la bande passante totale des puces pour le modèle 4 liens, et 480 Go/s également pour le modèle huit liens (contre 320 dans la spec version 1.0).

Si Samsung et Hynix sont impliqués dans le développement du standard, Micron reste pour l'instant le seul constructeur à avoir produit des échantillons commerciaux.

CES: La GDDR5M victime des déboires d'Elpida

Cet été, nous vous parlions de l'existence d'un type de mémoire qui était resté plus que discret et qui se présentait comme particulièrement bien adapté pour alimenter les APU : la GDDR5M. Il ne devrait finalement jamais voir le jour.

Pour rappel, la GDDR5M est un dérivé de la mémoire GDDR5, cette dernière étant avant tout destinée aux GPU (mais également exploitée sur la PS4). Si la base de la technologie est identique, la GDDR5M est optimisée pour autoriser un format "barrette mémoire" sans trop faire exploser les coûts, notamment à travers des puces de 4 Gbits interfacées en 16-bit, contre 32-bit pour la GDDR5 classique. De quoi permettre la mise en place de modules mémoire SO-DIMM de 2 Go et de 4 Go.

Durant la CES, nous avons eu l'opportunité de nous entretenir avec Joe Macri qui porte la double casquette de président du comité JEDEC en charge des mémoires DRAM et de Chief Technology Officer en charge des plateformes grand public chez AMD. Nous avons bien entendu voulu en profiter pour savoir ce qu'il était advenu de cette GDDR5M.

Les détails des futures APU A Series étant encore sous embargo, et l'abandon éventuel du support d'une technologie initialement prévue ayant peu de chances d'être discuté officiellement, nous n'avons bien entendu pas cherché à creuser le sujet en associant Kaveri à la GDDR5M. Nous estimons plus que probable qu'AMD avait prévu de l'utiliser pour Kaveri mais ceci reste de la spéculation de notre part.

Ce qui n'est plus de la spéculation par contre c'est que la GDDR5M est bel et bien morte et enterrée. Joe Macri nous a ainsi expliqué qu'il s'agissait d'une "superbe mémoire" qui se présentait extrêmement bien au départ. Très prometteuse, elle allait permettre de gagner du temps par rapport à l'arrivée des mémoires Wide I/O2, HBM ou encore HMC, et 2 industriels avaient pris la décision de la développer et de la produire.

C'est le point central du destin de cette GDDR5M puisque dans l'industrie de la DRAM, il est nécessaire qu'au moins deux sources d'approvisionnement soient confirmées pour qu'une technologie puisse évoluer vers une existence commerciale. Sans quoi les risques sont bien trop élevés au niveau la disponibilité ou encore de la tarification. C'est ce qui a tué dans l'uf le développement de la GDDR5M.

Les deux industriels qui s'étaient penchés dessus étaient Hynix et Elpida. Or, il y a presque deux ans, Elpida a dû annoncer sa banqueroute et sa mise sous protection par les autorités de régulation financières japonaises. Celles-ci ont mis fin à tous les nouveaux projets dont la GDDR5M. Ne restait alors que Hynix, et malheureusement aucun autre fabricant de DRAM, par exemple Micron, n'a voulu prendre le relais et se lancer dans l'aventure.

Si nos spéculations sont correctes, vous imaginerez sans difficulté que cette faillite d'Elpida a ainsi pu avoir des répercussions importantes pour AMD et Kaveri.

Le prix de la DDR3 remonte, une baisse en mars ?

Après avoir amorcé une (lente) baisse des prix depuis la mi-octobre, la DDR3 a vu son prix repartir à la hausse à partir de début décembre. Quasiment toute la baisse a été effacée en quelques jours, et les prix sont mêmes repassés depuis à des niveaux plus élevés pour les puces de 256 Mo DDR3-1600 qui sont à 2,46$, contre 2,33$ au plus haut entre septembre et mi-octobre, et 1,57$ avant l'incendie soit une hausse de 57%. Sur les puces de 512 Mo DDR3-1600, le prix unitaire est désormais de 4,11$, moins élevés que le plus haut de l'année à 4,27$ mais on reste tout de même à 36% de plus qu'avant l'incendie (3,14$).

Selon TrendForce , cette situation devrait malheureusement perdurer encore quelques temps puisque ce n'est qu'à compter de ce mois de janvier que cette usine, qui produit 10% de la mémoire mondiale, retrouvera sa pleine capacité de 130 000 wafers par mois. Après un mois de septembre vierge de production, SK Hynix avait lancé la production de 30 000 wafers de DRAM en octobre, puis 70 000 en novembre et 100 000 en décembre.

Attention toutefois, une puce ne se fabrique pas en une semaine mais en deux mois environ, c'est donc à compter de mars que ce retour à la normale devrait logiquement vraiment se ressentir sur les prix. On peut toutefois s'attendre à une baisse avant cette date, le niveau de production de décembre étant déjà assez élevé alors que dans le même temps Hynix a fabriqué de la DRAM sur des puces auparavant dédiées à la fabrication de NAND.

Micron abdique contre Rambus

Après Nvidia l'année dernière et SK Hynix en juin c'est aujourd'hui au tour de Micron d'abdiquer dans la guerre des brevets qui opposait la majeure partie de l'industrie à Rambus.

Pour rappel, ce feuilleton juridique avait démarré en 1991 lors des meetings du JEDEC (le comité de standardisation des formats de mémoire) autour du futur standard SDRAM. Entre 1991 et 1995, Rambus avait pris part au développement de la SDRAM et avait transmis les informations techniques du format en discussion à son département légal afin qu'il « solidifie et étende » les brevets de Rambus pour couvrir le standard SDRAM (une pratique interdite par les status du JEDEC qui réclamait que tous les brevets soient annoncés et proposés via une licence type FRAND Fair, Reasonable And Non Discriminatory, en français des termes raisonnables et non discriminatoires, c'est-à-dire semblables pour tous les acteurs).

Rambus avait alors claqué la porte du JEDEC en 1996 après avoir signé un accord avec Intel pour l'utilisation de la RDRAM, tout en préparant « un champ de mine de brevets » pour empêcher toute traction autour du standard SDRAM. Le début d'une longue bataille qui se termine finalement aujourd'hui. Si vous souhaitez plus de détails historiques sur ce sujet, nous vous conseillons vivement la lecture (PDF a partir de la page 3, en anglais) de ce verdict qui continent un rappel des faits très bien documenté et très complet.

Malgré de multiples invalidations de brevets , pertes de procès anti trust et encore d'autres invalidations de brevets pour destruction de preuves (voir le PDF au-dessus), la plupart des acteurs ont tout de même signé un accord à minima - avec Rambus.

Dans le cas de SK Hynix et Micron (les termes de l'accord de Nvidia ne sont pas connus) il s'agit d'accords bien loin de ce que pouvait réclamer jusqu'ici Rambus puisqu'aucun dommage n'est versé pour d'éventuelles violations de brevets durant les années passées, les deux sociétés ont simplement négocié un accord de licence : 12 millions de dollars par trimestre pour Hynix sur cinq années et aujourd'hui une licence flottante pour Micron ne pouvant pas dépasser 10 millions de dollars par trimestre pour une durée de 7 ans et qui inclut à son terme une licence perpétuelle sur « certains produits » non précisés. Des sommes certes non-négligeables, mais bien loin des 3.95 milliards de pertes évalués par Rambus lors de sa tentative perdue de procès anti trust contre Micron et Hynix.

A titre de rappel, Micron avait annoncé un chiffre d'affaire de 2.84 milliards de dollars sur le troisième trimestre de cette année. De quoi rendre négligeable le cout de la licence cédée à Rambus, même si Micron perd ce qui était ici une bataille de principes.