Les contenus liés au tag 7nm

Afficher sous forme de : Titre | FluxASML vend 15 machines EUV à Intel

Quelques (bonnes !) nouvelles de l'EUV

Intel densifie sa SRAM 14nm et parle du 10 et 7nm

Quelques nouvelles du 10 et 7nm chez TSMC

TSMC tenait la semaine dernière à San José son symposium, une conférence au cours de laquelle le fondeur taiwanais a partagé des détails inédits sur ses prochains process de fabrication de puces. Des détails rapportés par nos confrères d'EETimes et de Semiwiki (partie 1 et partie 2 ).

16FF+ et 16FFC

Pour le 16nm, si Apple l'utilise depuis de longs mois, les autres clients semblent peiner à lancer leur production, probablement à cause des coûts importants engendrés par la nouvelle technologie et aussi de quelques limites de capacité. TSMC s'est contenté de confirmer que son 16FF+ est en production "volume" (c'est à dire dédiée à des produits finis) depuis le troisième trimestre 2015 et qu'il s'attend à ce que son volume de wafers 16nm augmente significativement entre juin et octobre avec pour but d'atteindre 300 000 wafers par trimestre d'ici à la fin de l'année. Plusieurs produits 16FF+ sont déjà en production, comme les FPGA de Xilinx.

En parallèle TSMC propose également une version "compacte" (16FFC) de son process qui tente de réduire les coûts en diminuant par exemple le nombre de masques nécessaires. Cette version FFC sera celle qui sera privilégiée pour les usages non haut de gamme, même si elle propose plusieurs avantages intéressants, par exemple pour les usages très basse consommation (tension d'alimentation de 0.5V), mais aussi pour une version spécifique aux usages automobiles (une variante qui attendra mi 2017). TSMC avait annoncé cette variante publiquement en janvier, mais la production en volume sera entamée dès le mois d'avril. 70 tapeout 16FFC sont attendus cette année (à titre de comparaison, il y a déjà eu 70 tapeout 16FF+ en 2016), il sera intéressant de voir quels produits l'utiliseront !

10nm

TSMC est confiant sur l'arrivée du 10nm, même s'il s'agira vraisemblablement d'un node qui ne sera pas utilisé par tout le monde. La production en volume prendra place dans la Fab 15, dans deux nouvelles tranches construites pour l'occasion (les autres tranches produisent en 28nm). Le constructeur s'attend à produire 200 000 wafers par trimestres d'ici la fin de l'année 2017. Un premier tapeout 10nm pour un produit d'un de ses clients aurait été réalisé et la qualification est attendue au troisième trimestre cette année.

Malgré tout le 10nm reste un node qui sera limité côté clients, Xilinx ayant par exemple indiqué publiquement qu'ils attendraient le 7nm. Étant donné les délais suspicieusement courts entre le 10 et le 7nm, on peut les comprendre (productions en volume respectives annoncées pour 2017 et 2018) !

7nm

L'attente autour du 7nm est importante, et TSMC a commencé a donner quelques réponses à nos interrogations. D'abord, le fondeur proposera dès le début deux versions distinctes de son process 7nm, une version dédiée au mobile, et une autre aux produits hautes performances (+10 à 15% de performances en plus, avec pour but d'atteindre 4 GHz).

Les deux variantes devraient entrer en qualification en simultané au premier trimestre 2017. Pour expliquer le délai court entre le 10 et le 7nm, nous avions spéculé que le constructeur utiliserait une stratégie identique à celle utilisée entre le 20 et le 16nm, à savoir utiliser un BEOL (la partie basse de la puce qui contient les couches métalliques d'interconnexion) commun ce qui limiterait les gains de densité.

Après avoir évité a plusieurs reprises de répondre à la question dans ses conférences aux investisseurs, TSMC a confirmé que ce ne sera pas le cas : la variante mobile du 7nm apportera une densité 1.63x supérieure à celle de son 10nm ! C'est certes moins que le passage 28 à 20nm (1.9x) mais largement au dessus de la transition 20 à 16nm (1.15x, obtenu principalement par des optimisations des règles de design). Par rapport au 10nm, le 7nm devrait apporter 15 à 20% de performances en plus, ou 35 à 40% de consommation en moins selon les usages.

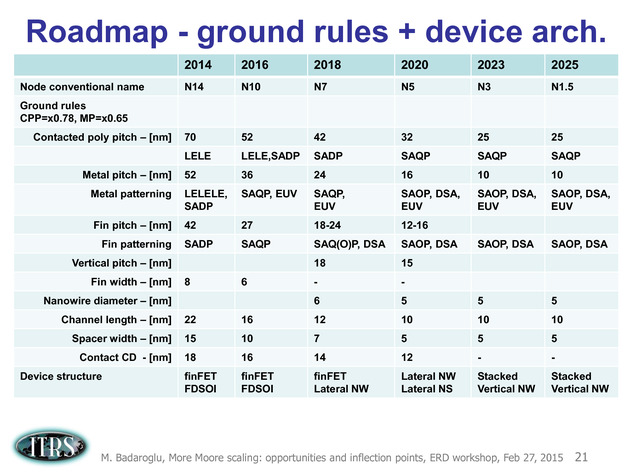

TSMC utilisera un matériel commun à 95% entre le 10 et le 7, facilitant la transition. La différence tiendra sur l'utilisation plus massive à 7nm du quadruple patterning (on ne sait pas encore exactement ou il sera utilisé, il semblait entendu sur les dernières roadmaps ITRS que le quadruple patterning - SAQP - serait utilisé pour les couches métal à 10 et 7 par exemple).

Le développement du 7nm avance puisque TSMC a indiqué avoir déjà produit des modules de SRAM de 128 Mbit, atteignant déjà des yields de 30% pour des dies pleinement fonctionnels. Il est toujours difficile de comparer ces chiffres tant les constructeurs les gardent secrets. En février 2010, soit une vingtaine de mois avant le lancement des premiers GPU 28HP (les Radeon 7970), TSMC annonçait cependant des yields sur sa SRAM de 26% . Atteindre 30% sur des puces pleinement fonctionnelles semble donc particulièrement encourageant à ce stade.

Si l'on considère les difficultés attendues par tous à 10 et à 7nm, la roadmap de TSMC semble particulièrement agressive et il faudra voir si le fondeur arrive a l'exécuter. On comprendra en tout cas qu'il ne faudra pas s'attendre à voir de 10nm ailleurs que chez Apple, ou possiblement Qualcomm étant donné les délais.

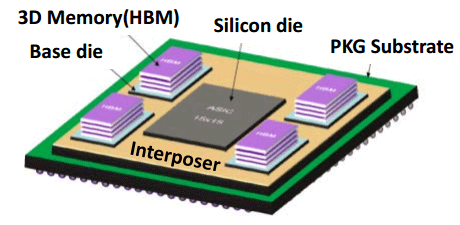

On conclura sur quelques informations données côté packaging, TSMC pense que c'est de ce côté que l'on réalisera des gains "faciles" et importants. D'abord pour la version haute performance CoWoS (Chip on Wafer on Substrate) qui consiste à utiliser un interposer en silicium pour relier des puces, le fondeur indique que l'on pourra atteindre des tailles plus importantes à 7nm dépassant les 1200mm2 (l'interposer utilisé par AMD sur les Fury X mesure un peu plus de 1000mm2) ce qui devrait donner un peu plus de marge. TSMC a également indiqué avoir réalisé le tapeout le mois dernier d'un "CPU" accompagné de deux piles de mémoire HBM2.

Côté mobile, c'est l'InFO WLP (Integrated FanOut Wafer Level Packaging) qui devrait apporter des gains intéressants. Par rapport au CoWoS, il s'agit d'une version beaucoup plus fine qui réduit voir élimine le substrat en "moulant" un ou plusieurs dies pour reconstituer un package très fin. TSMC annonce 20% de performances en plus pour une consommation 10% inférieure.

Exemple d'InFO POP

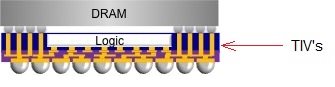

TSMC a rajouté une variante POP qui ajoute la possibilité de superposer un autre package (par exemple mémoire) par dessus un package InFO. TSMC utilise des fils dans les parties neutres du die pour relier la puce du dessus (des TIV, un concept identique aux TSV - through silicon Vias - si ce n'est que les fils traversent cette fois ci le package InFO et non un interposer). La production des InFO POP devrait débuter au second trimestre, ce qui coïncide côté timing avec le début de production attendu du prochain SoC d'Apple qui devrait utiliser ces technologies de packaging.

L'EUV possiblement pour le 7nm ?

Le site SemiWiki nous rapporte quelques informations sur l'état de la fabrication EUV, en provenance de la conférence SPIE Advanced Lithography qui se tient actuellement à San José.

Lors de la même conférence l'année dernière, les nouvelles étaient pour rappel plutôt bonnes (voir le lien pour un rappel complet sur la fabrication des processeurs et l'importance capitale de l'EUV !) et l'on espérait une introduction en cours de process pour le 10nm, et une introduction complète à 7nm. Malheureusement, on le rappelait en janvier, TSMC avait calmé les ardeurs en indiquant qu'il faudrait attendre le 5nm pour une éventuelle introduction de cette technologie.

SemiWiki confirme certains chiffres donnés lors de la dernière conférence aux investisseurs de TSMC, à savoir que la machine avait atteint sur une période de quatre semaines une production de 518 wafers/jour, un niveau encore largement insuffisant. Intel a partagé également quelques chiffres, un peu inférieurs à ceux de TSMC, à savoir entre 2000 et 3000 wafers par semaine (285-428 par jour).

On notera quand même que le taux de disponibilité des scanners de la société ASML a augmenté, passant de 55 à 70% chez TSMC (Intel rapportant une disponibilité identique) ! On notera que s'il est question d'une introduction en début de node à 5nm, TSMC laisse la porte ouverte pour le 7nm si jamais des progrès étaient effectués. Intel de son côté n'a pas donné d'information. Samsung envisagerait l'introduction à 7nm selon les présentations, sans plus de précisions.

Si la question de la disponibilité est importante, celle de la puissance de la source lumineuse l'est encore plus. Après avoir été limité à 40 watts l'année dernière, les machines actuellement en évaluation chez TSMC disposent désormais de sources 80 watts. C'est mieux, mais cela reste loin des 250 watts promis par ASML pour fin 2015. Les dernières prédictions sont désormais de 250 watts en 2016-2017, et au delà en 2018-2019, des plages particulièrement larges.

Atteindre les 250 watts de puissance permettrait d'augmenter significativement la cadence de production, atteignant 170 wafers/heure en théorie. ASML a effectué des démonstrations que TSMC et Intel semblent juger prometteuses de 185 et 200 watts. Reste à les voir en production, bien évidemment. Les challenges de cette technologie restent complexes et ne se limitent pas à ces deux points cruciaux, la question des défauts dans les masques est elle aussi importante même si là aussi TSMC et Intel ont visiblement noté quelques progrès. Vous pouvez retrouver plus de détails sur ces points dans l'article de SemiWiki .

TSMC vise 2020 pour le 5nm via l'EUV

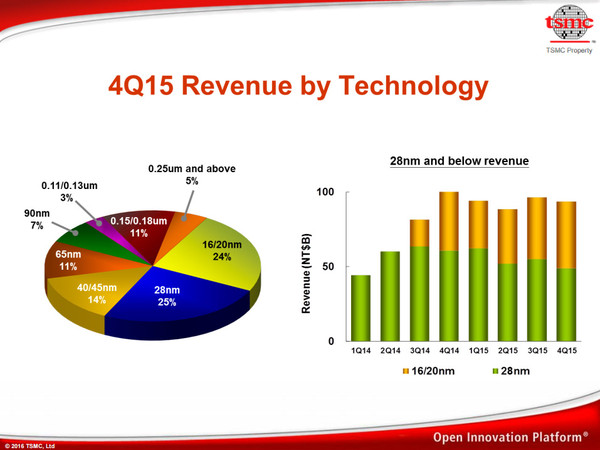

TSMC a présenté ses résultats pour le dernier trimestre 2015, pour une fois ils sont en baisse avec des ventes et un bénéfice qui baissent respectivement de 8.5 et 8.9%. La part du 16/20nm dans les revenus est en hausse, passant sur trois mois de 21 à 24%, ce qui se fait surtout au dépend du 28nm qui passe de 27 à 25%.

Le fondeur se montre confiant pour l'année à venir, indiquant qu'il devrait passer de 40% de parts de marché sur les process 16/14nm à plus de 70% en 2016. Cela se fera via 16FF+ (FinFet+) destiné aux produits les plus performants mais aussi nouveau 16FFC (FinFet Compact) pour le moyen de gamme et la basse consommation.

Pour le reste TSMC a confirmé le 10nm pour 2017, sans donner de date précise. Il y a trois mois il était question d'un début de la production en volume au dernier trimestre 2016 et de premiers revenus au premier trimestre 2017. La production en volume en 7nm a été annoncée pour le premier semestre 2018, et il faudra attendre 2 années supplémentaires avant de voir débarquer le 5nm. Le 5nm devrait finalement être le premier à utiliser l'EUV, mais TSMC travaille encore avec ASML à fiabiliser les machines : il a ainsi pu atteindre sur une période de 4 mois une moyenne de 500 wafer exposés par jour on est assez loin des 1000 wafer qu'elle peut atteindre en pointe.

16nm à l'heure, EUV en retard pour TSMC

TSMC a également annoncé ses résultats financiers. La société a enregistré pour le second trimestre un chiffre d'affaire de 6.62 milliards avec une marge brute atteignant 48.5%. Par rapport au même trimestre l'année dernière, cela représente une hausse de 12.2% du CA (et 33% pour les bénéfices).

Au-delà des chiffres, TSMC a donné quelques détails intéréssants, confirmant d'abord la cession de sa participation dans ASML qui avait été annoncée en janvier, en assurant que cela ne changeait strictement rien à ses liens avec la société basée aux Pays-Bas. TSMC a également cédé 5% de sa participation dans Vanguard (VIS), un spinoff de TSMC proposant des services spécialisés. TSMC garde malgré tout le contrôle de 28% de VIS, étant toujours l'actionnaire majoritaire.

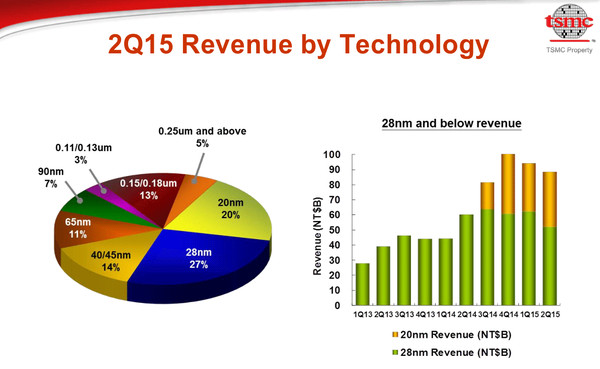

Le 28nm continue de représenter 27% des revenus tandis que le 20nm aura représenté 20% des revenus sur le second trimestre. TSMC note cependant que côté smartphones, les inventaires chez les constructeurs sont importants, particulièrement sur les produits d'entrée et milieu de gamme faute d'augmentation de la demande en Chine et dans les marchés émergeants. Le dollar elevé est l'une des causes mises en avant, tout comme les situations économiques locales. Tous ces facteurs font que TSMC s'attend à voir une hausse de son activité possiblement plus mesurée qu'ils ne le pensaient.

La nouvelle la plus importante est la confirmation que le 16nm est bel et bien en cours de production et que les premières puces ont été livrées ce mois-ci. Sur le 16nm, TSMC indique que la montée en puissance de son process sera extrêmement rapide, plus rapide que le 20nm profitant du BEOL (la seconde partie du process qui gère les interconnexions, plus de détails ici ) commun. Les taux de défauts sont annoncés comme extrêmement bas, et la courbe de réduction des défauts est la meilleure jamais obtenue par TSMC.

La société pense rafler en 2016 la majorité du marché 16nm. Les premiers clients en volume de TSMC sur le 16nm sont très probablement Apple (qui utiliserait aussi Samsung selon les rumeurs pour son A9) et Qualcomm qui ont en général la priorité sur les nouveaux nodes, même si AMD a annoncé avoir effectué deux tapeout sur ce process (sans préciser s'il s'agissait bien de TSMC, ou de GlobalFoundries).

TSMC a également profité de l'occasion pour parler du 10 et du 7nm. Selon TSMC les progrès réalisés sur le 10 nm sont « très encourageants » et continue de prévoir un début de la production en volume fin 2016. Une date qui, si elle est effectivement tenue, placerait potentiellement la sortie de produits 10nm en volume chez les très bons clients de TSMC avant même la sortie de Cannonlake chez Intel. Encore faut-il que TSMC tienne ses délais, bien évidemment, mais sur les deux derniers nodes cela a plutôt été le cas. Techniquement par rapport au 16 FinFET+ (la version la plus avancée de son process FinFET), le 10nm apporte 15% de vitesse à puissance égale, ou 35% d'économie d'énergie à vitesse égale. La densité est 2.2x celle du 16 FinFET+.

On notera avec intérêt que pour le 10nm, TSMC annonce des tape out sur un tas de secteurs, y compris ce qu'ils appellent high-performance computing, sous-entendu des CPU/SoC. Morris Chang, le chairman de TSMC est même allé un peu plus loin indiquant qu'il pense que TSMC va jouer un rôle important sous peu dans les marchés notebook et serveur, à condition de lier trois acteurs. Non seulement une fonderie (TSMC), ARM, mais aussi des sociétés capables de faire des designs custom « haute performance ».

TSMC a également évoqué le 7nm, s'attendant à lancer la qualification de son process au premier trimestre 2017, soit seulement cinq trimestres après la qualification attendue du 10nm. Le fondeur n'est pas très précis sur la technique, indiquant profiter de la maturité du 10nm pour mettre en place le 7nm, ce qui sous entends peut être que de la même manière qu'ils l'ont fait pour le 16nm avec le 20nm, TSMC pourrait garder le BEOL du 10nm sur le 7nm. Cela expliquerait très certainement le délai très réduit entre les qualifications.

Concernant l'EUV, Mark Liu, l'un des Co-CEO a indiqué que la porte était toujours ouverte et qu'ils travaillaient activement avec ASML, mais qu'il restait encore des challenges à résoudre, particulièrement autour des masques. Il a également indiqué que le 7 nm n'utiliserait « probablement pas » l'EUV dans un premier temps mais qu'il pourrait être introduit dans un second temps, et qu'il serait introduit dès le début à 5nm. Un changement de position et une mauvaise nouvelle pour ASML - par rapport au discours habituel qui indiquait que l'EUV serait possiblement introduit dans un second temps à 10nm et dès le début à 7nm.

Premières puces en 7nm pour IBM !

Alors qu'IBM a revendu son activité fabrication de semi-conducteurs à Global Foundries en octobre dernier (un rachat qui s'est finalisé le premier juillet de cette année), IBM vient annoncer avoir produit une puce de test fonctionnelle en 7nm, une première que rapportent nos confrères d'EETimes .

Si IBM réalise l'annonce, en pratique la puce a été fabriquée dans un centre de recherche du SUNY Polytechnic Institute financé en partie par l'état de New York et divers partenariats privés. Virtuellement toutes les sociétés du milieu participent puisque l'on retrouve dans la liste des sociétés, outre IBM, Intel, TSMC, Samsung, GlobalFoundries ou encore ASML. C'est à cet endroit que l'on retrouve par exemple l'effort de recherche du Global 450mm Consortium qui travaille sur la future transition aux wafers de 450mm (contre 300 actuellement, un mouvement qui a pris un coup d'arrêt ces dernières années).

Avant son rachat, IBM avait annoncé participer à hauteur de 3 milliards (sur 5 années) au développement de futures puces, tandis qu'en début d'année, suite au rachat par GloFo, IBM avait regroupé ses 220 ingénieurs restants sur le site de SUNY sous l'égide « IBM Research ».

Historiquement, IBM a toujours aimé jouer au jeu des annonces et continue ici dans sa tradition. En pratique il s'agit d'une première puce de test qui inclut transistors, cellules SRAM et interconnexions, les blocs essentiels même si, évidemment, on reste cependant très loin de la production en volume.

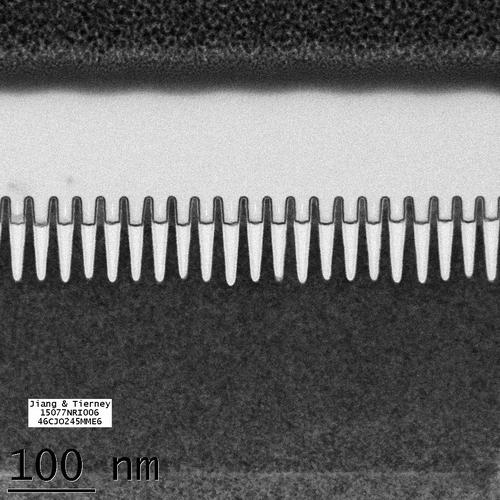

Les transistors FinFet 7nm vus au microscope

Au-delà de l'effort, on s'intéressera surtout aux choix réalisés par IBM pour son process, qui repose cette fois sur l'EUV. Nous avions eu l'occasion d'en parler, l'EUV va mieux et si une introduction est possible en cours de node pour le 10nm, TSMC et les autres visent une introduction ferme pour le 7nm et de ce côté IBM ne déroge pas.

Plus surprenant, les choix réalisés autour des structures et des matériaux. Alors que l'on s'attend probablement à voir d'autres structures que le FinFet introduites à 10 ou 7nm par Intel, IBM utilise ici des structures FinFet également, la différence s'effectuant sur les matériaux avec le retour du silicium-germanium (SiGe) étiré pour le canal, sur substrat en silicium. Ce n'est pas la première fois que le germanium apparait dans les process, même si aujourd'hui on le trouve principalement dans les process analogiques/radio . L'utilisation du SiGe étiré dans les semi-conducteurs est une innovation d'IBM et il est assez surprenant de le retrouver sur un process si avancé, qui plus est en EUV. D'autant que côté densité, les transistors peuvent être espacés de 30nm ce qui permettrait, par rapport au 10nm qui était en développement par IBM, d'augmenter la densité de 50%.

Développer un process « clef en main » - c'est comme cela qu'il est décrit par IBM qui dit avoir optimisé non seulement l'EUV, le dépôt du SiGe mais aussi les autres étapes du process comme l'interconnexion (BEOL) ne manque évidemment pas d'ironie mais nos confrères d'EEtimes notent qu'IBM fera profiter logiquement de ses travaux de recherche à GlobalFoundries qui pour rappel dispose d'une exclusivité de 10 années pour la production des processeurs serveurs d'IBM. Nos confrères sous entendent que Samsung pourrait également profiter de ces travaux, en se rappelant aux bons souvenirs de l'abandonnée Common Platform qui liait les trois sociétés.

Rien n'en est cependant moins sur puisque pour rappel, Samsung avait développé son propre process 14 nm sans IBM qui aura au final sauté ce node. Le fondeur coréen avait ensuite partagé son 14nm en intégralité avec GlobalFoundries. Pour le 10nm, IBM avait travaillé également sur son propre process que l'on retrouvera vraisemblablement tel quel chez GlobalFoundries. Les trois sociétés semblent cependant être restées en bons termes et l'on imagine que si la solution 7nm d'IBM est plus intéressante que les efforts développés en internes, ces sociétés continueront de mutualiser leurs efforts pour une éventuelle mise en production, que l'on n'attend pas de toute manière avant 2018 ou 2019. Ce que fera Samsung en 10 nm nous donnera peut-être un indice. Pour l'instant, si le constructeur a montré un wafer 10 nm, et indiqué qu'il s'attend à lancer la production en volume fin 2016, il n'a rien dévoilé sur la technique