Les contenus liés aux tags Samsung et Process

Afficher sous forme de : Titre | Flux7nm fin 2018 pour GlobalFoundries ?

Nouvel accord WSA entre AMD/GlobalFoundries

Intel Custom Foundry prend une licence ARM !

L'ITRS prépare l'après loi de Moore

Le 10nm de TSMC est bien à l'heure

Il y a quelques jours de cela, le site Digitimes avait fait circuler une rumeur par laquelle TSMC et Samsung disposeraient de yields trop bas pour leur production 10nm. De quoi lancer multiples spéculations sur des retards de production.

Pour rappel, TSMC et Samsung ont annoncé avoir commencé la production en volume (des puces qui se retrouveront donc dans des produits commerciaux) de leurs nouveaux process 10nm au quatrième trimestre.

Pour tenter de couper l'herbe sous le pied des rumeurs, TSMC a confirmé une fois de plus au Taipei Times que non seulement la production avait bien commencé au quatrième trimestre, mais que le 10nm générerait des revenus pour TSMC dès le mois prochain - ce qui signifie en pratique que TSMC aura livré des puces à ses clients.

Sur la question des clients, Digitimes avait spéculé qu'en plus d'Apple (client traditionnel en début de disponibilité de node pour TSMC), MediaTek et HiSilicon seraient parmi les premiers clients 10nm de TSMC. Des informations plutôt surprenantes pour les deux sociétés qui produisent (en grand volume) des SoC ARM à prix réduit, utilisant les blocs d'IP génériques (les "Cortex-A") dessinés par ARM.

Qualcomm, l'autre client habituel des débuts de nodes chez TSMC aurait cette fois ci misé sur Samsung pour le 10nm. Samsung n'a pas réagit aux rumeurs lancées par Digitimes. On notera cependant qu'il y a quelques semaines de cela, Samsung avait évoqué l'idée de mieux séparer ses activités. En effet, la marque coréenne entre assez régulièrement en conflit d'intérêts avec les éventuels clients de son activité "fabrication". Une situation que l'on a vue à de nombreuses reprises avec Apple par exemple.

Qualcomm, l'autre client habituel des débuts de nodes chez TSMC aurait cette fois ci misé sur Samsung pour le 10nm. Samsung n'a pas réagit aux rumeurs lancées par Digitimes. On notera cependant qu'il y a quelques semaines de cela, Samsung avait évoqué l'idée de mieux séparer ses activités. En effet, la marque coréenne entre assez régulièrement en conflit d'intérêts avec les éventuels clients de son activité "fabrication". Une situation que l'on a vue à de nombreuses reprises avec Apple par exemple.

Une restructuration qui séparerait les équipes de design de puces utilisées par Samsung (LSI et SoC) de l'activité "fab" serait donc envisagée selon nos confrères de Business Korea . Une séparation qui servirait surtout à rassurer d'éventuels clients car en pratique Samsung ne compte pas se séparer de son activité "fab".

Des détails sur le 7nm à l'ISSCC 2017

La conférence ISSCC (International Solid-State Circuits Conference) se tiendra pour son édition 2017 du 5 au 9 février à San Francisco, et nos confrères d'EEtimes ont eu accès à l'avant programme.

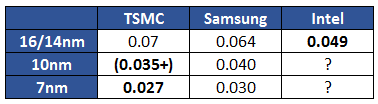

Comme tous les ans les acteurs du milieu des semi conducteurs y présenterons leurs nouveautés, et l'on notera que TSMC et Samsung présenterons leurs cellules SRAM (utilisées notamment pour la mémoire cache dans les puces). L'année dernière, Samsung avait proposé deux versions distinctes pour son process 10nm, optimisées pour la densité ou les performances, de 0.040 µm² et 0.049 µm².

D'après nos confrères, TSMC présentera une cellule SRAM 7nm de seulement 0.027µm², tandis que Samsung présentera une cellule SRAM 7nm de 0.030µm², mais fabriquée en EUV. D'après Samsung, l'EUV permettrait de diminuer la tension minimale nécessaire de 39.9mV (TSMC indique aussi des optimisations basse tension, on attendra la conférence pour comparer l'impact ou non de l'EUV).

La SRAM est un composant fondamental des puces et sa taille permet en général de se donner une bonne idée des process. Cependant il faut être assez méfiant, les constructeurs annonçant parfois des "records" de densité qu'ils n'utilisent pas forcément en production. Nous avons rapporté dans le tableau ci dessous les chiffres les plus bas (correspondant aux bibliothèques "hautes densité") pour TSMC, Samsung et Intel :

Par rapport au tableau, on notera qu'Intel n'utilise pas cette SRAM haute densité dans ses processeurs, mais de la SRAM 0.059 µm². Même en prenant cela en compte, Intel garde la meilleure densité à 16/14nm pour la SRAM. Le constructeur ne fournit pas encore d'infos sur ses futurs process.

TSMC n'a pas donné non plus de chiffre exact pour son 10nm, estimant simplement 50% de réduction par rapport à son 16nm sur la SRAM, ce qui nous vaut un chiffre entre parenthèses. Selon toutes vraisemblances, et conformément aux autres annonces sur la densité (2.1x d'après le constructeur), on estimera que TSMC devrait avoir une SRAM d'une taille légèrement inférieure à celle de Samsung.

Intel ne devrait pas effectuer d'annonce sur ce sujet lors de l'ISSCC, ce qui est assez dommage. Le constructeur devrait présenter les FPGA Altera Stratix 10 (14nm) tandis qu'AMD proposera une présentation plus en détails de Zen.

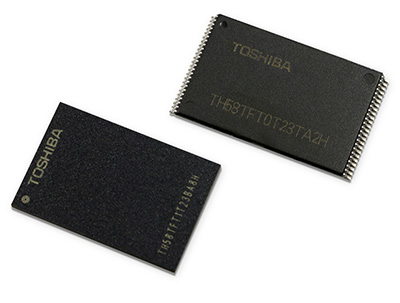

On notera aussi que Western Digital/Toshiba, ainsi que Samsung, présenterons des puces 3D NAND 512 Gbit TLC 64 couches. Dans le cas de Samsung, cette puce avait été annoncée cet été, plus de détails techniques devraient être disponibles. Pour Western Digital/Toshiba, cette puce avait été évoquée cet été comme objectif.

On notera que nos confrères pointent à raison un grand absent : une fois de plus, ni Intel, ni Micron, n'effectueront de présentation technique de leur mémoire 3D Xpoint !

Samsung annonce de futurs process 14 et 10nm

Samsung vient d'indiquer par un communiqué de presse qu'il proposera une quatrième version de son process 14nm. Baptisée 14PLU, elle fait suite au 14LPE (Low Power Early, la première version dispo lorsque les yields étaient faibles), 14LPP (Low Power Plus, version un peu plus optimisée lorsque les yields étaient stabilisés), 14LPC (possiblement Low Power Compact, la version réduit les couts et fait écho au 16FFC de TSMC, tout en ajoutant la possibilité de pouvoir fabriquer des radios, indispensable pour la fabrication de modems par exemple).

Samsung vient d'indiquer par un communiqué de presse qu'il proposera une quatrième version de son process 14nm. Baptisée 14PLU, elle fait suite au 14LPE (Low Power Early, la première version dispo lorsque les yields étaient faibles), 14LPP (Low Power Plus, version un peu plus optimisée lorsque les yields étaient stabilisés), 14LPC (possiblement Low Power Compact, la version réduit les couts et fait écho au 16FFC de TSMC, tout en ajoutant la possibilité de pouvoir fabriquer des radios, indispensable pour la fabrication de modems par exemple).

Comme souvent, ces "variantes" de process sont des itérations autour d'une même technologie. Elles sont l'occasion d'annoncer des gains obtenus par l'optimisation de l'exploitation des process. Dans le cas de la version U, Samsung annonce des performances "plus élevées" à consommation égale, avec des règles de design identiques à son process 14LPC. Pour Samsung, le 14LPU est adapté aux utilisations "hautes performances" qui requièrent "beaucoup de calculs".

Un appel du pied à peine voilé aux fabricants de GPU et de SoC haut de gamme. Si Samsung a réussi a obtenir la fabrication de quelques GPU Nvidia (notamment les GP107 des GTX 1050), il s'agit de puces plus petites avec des niveaux de performances moindres par rapport au haut de gamme, qui reste toujours fabriqué chez TSMC. De la même manière, si AMD a fabriqué Polaris chez GlobalFoundries (sur un process techniquement identique à celui utilisé par Samsung, GlobalFoundries utilisant le process de Samsung sous licence), il ne s'agit pas non plus du haut de gamme (les raisons d'AMD étant beaucoup plus complexes).

La compétition avec TSMC est excessivement rude pour Samsung, qui tente avec cette quatrième version de s'attirer de nouveaux marchés. Le dernier "gros coup" du fondeur avait été la co-fabrication des SoC A9 d'Apple, un marché obtenu grâce au retard annoncé de TSMC. Un retard comblé en dernière minute par le fondeur Taiwanais. Les comparaisons directes sont toujours à double tranchant, et si Samsung avait bel et bien un avantage de densité sur son concurrent, sur le plan des performances TSMC restait, malgré la précipitation, en tête.

Cette version 14LPU tentera de combler ce déficit d'image même si selon toutes vraisemblances, TSMC gardera une main mise sur le haut de gamme sur ce node.

En parallèle, Samsung annonce également un 10LPU, qui sera cette fois la troisième version du 10nm de Samsung. Contrairement au 14LPU, le 10LPU augmentera la densité par rapport aux 10LPE/LPP, et Samsung le présente comme le 10nm proposant le cout le plus faible "de l'industrie". Le nom de 10LPC aurait probablement été plus adapté pour décrire ce process mais peu importe !

Dans les deux cas, il s'agit d'annonces puisque les kits de développement (PDK) pour le 14LPU et le 10LPU ne seront disponibles qu'au second trimestre 2017 ! On ne s'attendra donc pas a voir des produits les exploiter rapidement, le 10LPP entrera en production en volume pour rappel mi-2017.

On notera enfin que Samsung confirme une fois de plus sa volonté d'utiliser la lithographie EUV à 7nm, pour au moins une partie des couches de la puce. On rappellera que le 7nm de Samsung devrait arriver plus tard que le celui de son concurrent, la société ayant sous entendu à plusieurs reprises ces dernières semaines que le 10nm aurait une durée de vie plus longue qu'annoncée par certains.

TSMC tente en effet de lancer la production 7nm volume avec un an de décalage par rapport au 10nm (soit respectivement Q4 2016 pour le 10nm, et Q4 2017 pour le 7nm). Un rythme infernal qui ne sera suivi par personne d'autre (et largement financé, faut-il le rappeler, par Apple), mais sur lequel TSMC semble extrêmement confiant.

Le 10nm LPE en production chez Samsung

Samsung vient d'indiquer par le biais d'un communiqué de presse avoir commencé la production en volume de son process de fabrication 10nm.

Samsung vient d'indiquer par le biais d'un communiqué de presse avoir commencé la production en volume de son process de fabrication 10nm.

Plus précisément, Samsung annonce avoir commencé la production en volume d'un SoC 10nm, une première pour l'industrie d'après eux. On se rappelle que TSMC doit de son côté lancer la production en volume de son propre 10nm ce trimestre.

La définition précise de la production en volume est toujours l'occasion d'interprétations diverses chez les fondeurs, on notera que Samsung indique que les premières puces seront disponibles dans des produits finis début 2017, et plus généralement en volume au courant de l'année. Un planning qui l'aligne dans les annonces avec son concurrent principal.

Si techniquement Samsung avait été plus agressif que TSMC côté densité sur le node 14/16, tout laisse penser que l'inverse va se produire. Les chiffres annoncés vont dans ce sens puisque le 10nm apporte selon Samsung un gain de densité de 30%. Selon les estimations du blog Semiwiki , si TSMC reprend un avantage de densité sur Samsung sur ce node, l'écart sera en pratique bien moindre que celui constaté à 14/16. On notera au passage que le fondeur indique utiliser du triple-patterning sur ce node.

La densité ne fait bien évidemment pas tout et Samsung évoque au choix 27% de performances en plus, ou 40% de consommation en moins. Des chiffres qui sont donnés pour les deux versions de son process sans plus de précisions. A l'image de ce qu'il avait fait pour le 14nm, Samsung proposera d'abord un 10LPE (early) et un 10LPP. C'est le 10LPE qui est entré en production volume aujourd'hui, le 10LPP étant prévu pour la seconde moitié de l'année 2017.

La société ne mentionne pas de clients ou de nombre de produits qui seraient qualifiés en 2017 mais rappelle que ses kits de développements sont disponibles.

Si Samsung produit pour ses propres besoins, la société dispose aussi d'une activité de fondeur pour clients tiers qu'ils tentent de développer petit à petit. Leur part de marché était de 5.3% en 2015, à titre de comparaison TSMC tenait 54.3% du marché cette même année.

Proposer du 10nm en même temps que le leader est une bonne chose, même si l'on sait que de nombreux clients ont annoncé passer directement au 7nm, en grande partie parce que ce dernier aura une durée de vie excessivement courte (un an chez TSMC). Chez Samsung, la durée de vie de ce node devrait être un peu plus longue, le 7nm étant prévu pour 2018.

TSMC et InFo PoP pour l'A10 de l'iPhone 7

Ce week end, la société Chipworks a procédé à son traditionnel "teardown" des puces incluses dans l'iPhone 7 , en se concentrant particulièrement sur le SoC A10 d'Apple.

Rappel sur l'A9

Avant de regarder l'A10, revenons un instant sur l'A9 inclus l'année dernière dans l'iPhone 6S. Il avait la particularité d'être sourcé en parallèle chez Samsung et TSMC, quelque chose de quasi unique pour des puces haut de gamme sur des process de dernière génération, ce qui nous avait permis d'effectuer quelques comparaisons.

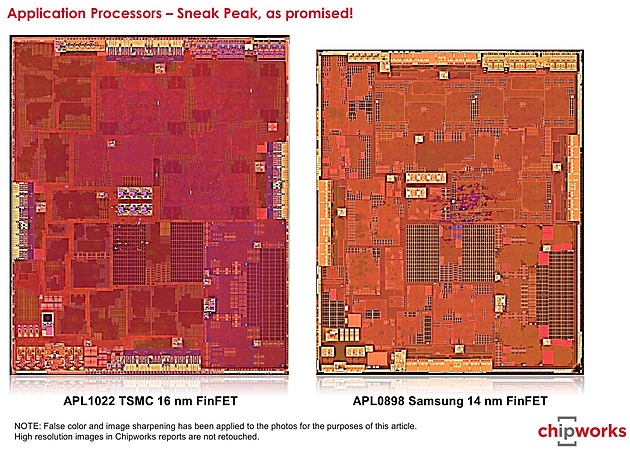

Les deux A9 de l'iPhone 6S (2015)

La différence la plus visible était la densité des deux process : l'A9 "Samsung" mesurant 96mm2, contre 104.5mm2 pour la version TSMC. A l'époque nous n'avions pas de certitudes sur les variantes exactes des process utilisées. Depuis, Chipworks a confirmé qu'il s'agissait bien du 14LPE chez Samsung. Le cas de TSMC est plus compliqué, Chipworks ne répondant pas (gratuitement) à la question. Les rumeurs laissent penser qu'il ne s'agissait pas d'un simple 16FF, mais d'une version "custom" empruntant en partie au process 16FF+.

Outre la densité, les tests pratiques avaient suggéré une différence de consommation à pleine charge avec un avantage pour la puce de TSMC. De quoi laisser penser que son process avait besoin de tensions inférieures à celui de Samsung pour obtenir les mêmes performances.

Depuis, Chipworks a la aussi répondu partiellement à la question suggérant que le problème se situerait pour le process de Samsung sur le rapport puissance/performances de ses NMOS . On ne sait pas si le problème persiste sur la version 14LPP qui a remplacé le 14LPE.

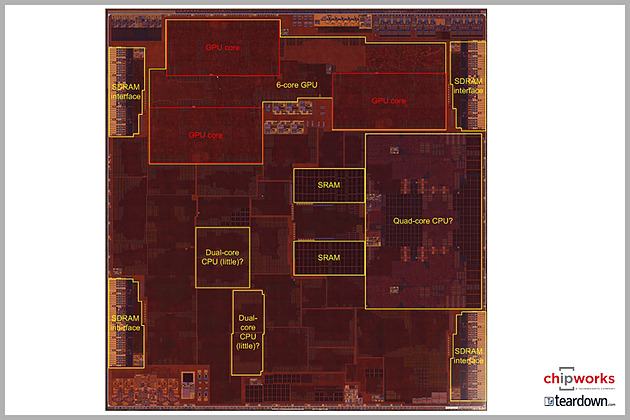

L'A10 : 16FFC TSMC

Première différence par rapport à l'année dernière, l'A10 semble produit cette année exclusivement par TSMC. Il est plus large que l'A9, mesurant 125mm2 pour 3.3 milliards de transistors annoncés. Côté process il s'agit du 16FFC (ou d'une variante) de TSMC, la troisième version "optimisée" du 16nm de TSMC. Annoncée en janvier dernier, le C signifie "Compact" et ce process vise avant tout les usages basses consommation tout en réduisant de manière significative les coûts de fabrication.

D'après Chipworks, l'utilisation des bibliothèques optimisées permet une bien meilleure utilisation du die, avec une compacité équivalente à celle des process TSMC précédents. Chipworks estime que la même puce aurait demandé 150mm2 en 16FF. Etant donné que 70 tapeouts de clients de TSMC sont attendus sur ce process cette année, les progrès de densité du 16FFC devraient profiter assez largement, on attendra de voir les constructeurs qui annonceront des puces l'utilisant.

Chipworks note également que l'A10 est beaucoup moins haut que les générations précédentes. Comme beaucoup de SoC, il est de type PoP et embarque la mémoire au dessus du die logique. Cependant plutôt que d'empiler les quatre dies de mémoire (2 Go de LPDDR4 Samsung sur l'A10 de l'iPhone 7), ils sont placés côte à côte.

Qui plus est, comme nous le supposions la puce utilise le nouveau packaging InFo de TSMC (dans sa version InFo-PoP) pour relier les dies entre eux.

big.LITTLE et performances

Côté performances les premiers benchmarks synthétiques évoquent 40% de gains pour le CPU ARM par rapport à l'année dernière, tout en restant en 16nm.

Pour arriver à ce gain, Apple augmente d'abord significativement la fréquence, passant de 1.85 GHz sur l'A9 à 2.35 GHz sur l'A10. Sur ce point, la marque exploite à la fois la marge notée de son process l'année dernière (on peut supposer facilement que l'A9 aurait eu une fréquence plus élevée s'il avait été sourcé uniquement chez TSMC) et les gains apportés par le 16FFC.

Ce gain de 27% de fréquence est accompagné de changements au niveau de l'architecture. Ceux ci ne sont pas encore connus, au delà du nom Hurricane, mais Chipworks note que le cluster CPU prend une place plus importante sur le die, 16mm2 face à 13mm2 sur l'A9, malgré l'utilisation d'un process plus compact.

Il est cependant difficile de se baser sur cette différence de taille étant donné que l'A10 est en réalité un quad core big.LITTLE dans la nomenclature ARM. En plus des deux coeurs hautes performances à 2.35 GHz (big), deux coeurs basse consommation à 1.05 GHz (LITTLE) sont également présents sur le die (leur emplacement exact est pour l'instant inconnu, ce qui vaut les points d'interrogation sur le diagramme au dessus).

Contrairement à d'autres implémentations dans l'écosystème ARM, les applications ne peuvent pas utiliser en simultanée les deux blocs de coeurs, le passage de l'un à l'autre étant transparent pour elles (géré par la puce et l'OS). L'intérêt de cet arrangement est bien entendu d'augmenter l'autonomie en ne sollicitant les coeurs haute performances que lorsque nécessaire.

Déjà largement en avance côté performances sur le reste de l'écosystème ARM, l'A10 commence à devenir embarrassant même pour Intel, dépassant un Core M Skylake en monothread sous Geekbench 4 (voir ici et là ), avec un "TDP" au moins deux fois inférieur (et sans mécanisme Turbo).

Intel se consolera tout de même de sa présence dans une partie des iPhone 7 car c'est l'autre information de Chipworks, la société confirme qu'une partie des modèles utilise un modem Intel XMM 7360 (certains modèles intègrent un modem Qualcomm X12). Très en retard, le XMM 7360 est un modem LTE 450 Mb/s Cat 10 certes dessiné par Intel, mais fabriqué selon toutes vraisemblances comme ses prédécesseurs... par TSMC.