Nouvelle étape pour la PRAM !

Publié le 30/06/2011 à 11:47 par Marc Prieur

La mémoire à changement de phase, appelée également PCM (Phase-change Memory) ou PRAM (Phase-change Random Access Memory), vient de franchir une nouvelle étape avec la mise au point par IBM d'un prototype capable de stocker 2 bits mémoires dans une cellule. Ce pas est important puisqu'il permet à la PCM d'avoir une meilleure densité et donc coût par bit inférieur, comme c'est le cas pour la Flash MLC qui stocke également deux bits par cellule.

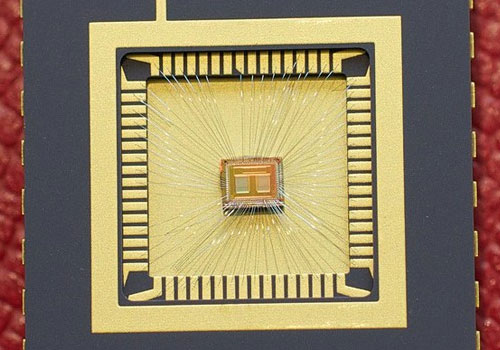

Pour l'instant on est toutefois loin d'une commercialisation et le prototype est une puce de 64 Mo gravée en 90nm, contre 25nm pour les dernières mémoires Flash. IBM vise pour le moment 2016 pour des applications serveurs, et a donc le temps de transposer la technologie sur des process plus fins d'ici là.

Comme la mémoire Flash NOR ou NAND, la PCM est non volatile et est donc capable de conserver les données même si elle n'est plus alimentée. Chaque cellule contient du chalcogénure, un matériau capable de passer d'un état vitreux (molécules en désordre) à un état cristallin (molécules rangées selon un motif). Ces deux états diffèrent par leur propriété électrique et la mesure de la résistance permet donc de lire les données qui sont écrites en changeant l'état par échauffement.

L'avancée d'IBM consiste donc à stocker gérer des états intermédiaires pour un total de 4 états correspondants à 00, 01, 10 ou 11 en termes binaires. Haris Pozidis, qui a mis au point la technologie, estime qu'il sera à terme possible de stocker 3 bits par cellules, voir 4 en changeant de matériaux.

Un problème à régler en urgence reste la gestion de l'évolution de la résistance des cellules au fil du temps. En utilisant des états intermédiaires, une telle mémoire est plus sensible à l'évolution de la résistance offerte par une cellule au fil du temps et qui peut entrainer des erreurs de lecture (lire 00 par exemple alors qu'on avait stocké 01). Pour contourner le problème IBM à mis au point un algorithme qui ne se base pas sur la résistance absolue pour mesurer l'état mais sur la résistance relative entre les cellules. Ceci permet à IBM d'annoncer un taux d'erreur d'environ 1 pour 100 000 après 37 jours à température ambiante, ce qui devrait permettre d'atteindre les 1 pour 10^15 (1 millions de milliards) avec une correction d'erreur, mais pour le moment l'algorithme n'as été utilisé que sur une puce de test plus petite et sur seulement 200 000 cellules.

Les promesses de la mémoire PCM sont multiples par rapport à la Flash, puisque IBM annonce des vitesses en écriture améliorées par un facteur de 100 avec une latence en écriture de seulement 10 microsecondes et une endurance d'au moins 10 millions de cycles. Reste maintenant à voir si ces promesses seront tenues en pratiques d'ici 2016 !

Pour rappel Samsung fabrique depuis 2009 de la PRAM , mais pour l'instant avec des spécifications qui la limite aux applications mobiles. Hynix et Micron travaillent également sur ce type de mémoire.

Vos réactions

Contenus relatifs

- [+] 17/10: 16 et 32 Go pour les premiers Intel...

- [+] 13/10: Alliance autour d'un nouveau bus mé...

- [+] 11/08: V-NAND Gen4 et Z-NAND pour Samsung

- [+] 10/08: PRAM 3D XPoint QuantX pour Micron

- [+] 18/05: IBM met au point de la PCM en TLC

- [+] 15/01: Du retard et de la PRAM pour 3D XPo...

- [+] 05/08: 3 millions d'IOPS pour un SSD HGST ...

- [+] 01/12: Une puce PRAM 8-Gbit chez Samsung

- [+] 30/06: Nouvelle étape pour la PRAM !

- [+] 22/09: Samsung fabrique (enfin) la PRAM