Actualités informatiques du 07-08-2013

- Un nouvel acteur dans la Resistive RAM

- La V-NAND en production chez Samsung !

- N760 HAWK, une GTX 760 boostée chez MSI

- IBM ouvre un peu plus l'architecture Power

| Août 2013 | ||||||

|---|---|---|---|---|---|---|

| L | M | M | J | V | S | D |

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 | 31 | |

Un nouvel acteur dans la Resistive RAM

Une startup a cherché (et réussi) à faire parler d'elle ces derniers jours en annonçant avoir développé un prototype de Resistive RAM (ou RRAM). Cette technologie mémoire dérivée du Memristor, prédit en 1971 et implémenté par Hewlett Packard pour la première fois en 2008, est censée cumuler les avantages de la NAND et de la DRAM, à savoir l'aspect non volatile de la NAND (les données ne s'effacent pas quand la mémoire n'est plus alimentée, contrairement à la RAM) et la rapidité d'accès aléatoire de la DRAM.

Ce n'est bien entendu pas le premier prototype du genre puisque l'on se souvient par exemple que Elpida (avec Sharp), mais aussi Hewlett Packard (avec Hynix), Samsung ou Panasonic ont annoncé respectivement des prototypes, et même Rambus s'intéresse au sujet, tout comme divers instituts de recherche comme l'ITRI ou l'IMEC .

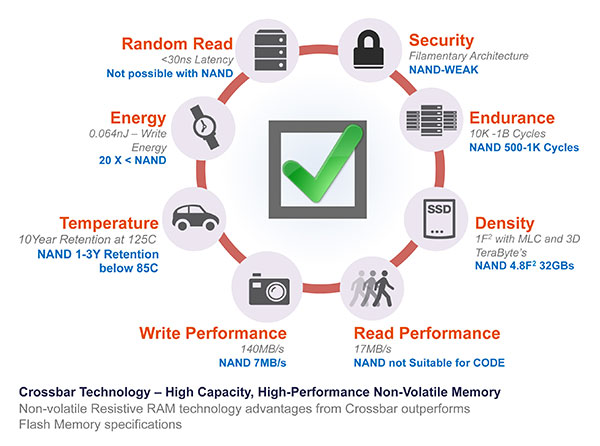

Le communiqué avance de gros chiffres : 20x plus rapide en écriture, une consommation 20x inférieure, et 10x l'endurance pour la moitié de la surface comparé à la meilleure NAND disponible actuellement. Le tout illustré par ce schéma :

On ne manquera pas de relever plusieurs grossières approximations sur le schéma, si le chiffre de 140 Mo/s en écriture est tout à fait remarquable, dire que la meilleure NAND peut seulement écrire à 7 Mo/s est un large raccourci. De même le graphique fait le choix de comparer les performances en lecture en aléatoire (bit par bit) à la NAND, alors que cette dernière ne s'accède pas de la sorte. Crossbar ne donne pas de chiffre pour sa RRAM en accès séquentiels, se contentant d'un 17 Mo /s en aléatoire alors qu'en séquentiel une puce de NAND classique se situe autour de 100 Mo /s.

A noter que si Crossbar indique sur ce schéma que le mode aléatoire n'est pas applicable à la flash, ce n'est pas le cas de ce white paper (PDF) , ou est indiqué 0.04 Mo/s (sic) pour la NAND avec le commentaire "RRAM will provide faster NAND-like products". En fait comme la flash de type NOR, la RRAM a l'avantage de disposer d'un accès pleinement aléatoire (les cellules sont connectées en parallèle et accessibles individuellement, et non pas en série comme sur la NAND) ce qui permet d'exécuter directement un programme sans devoir le charger en DRAM. Certaines valeurs de ce white paper, qui date pourtant de cette année, ne correspondent pas à l'illustration. Il parlait de 20 ans pour la rétention (contre 10 pour ce qu'on pense être la version finale) et de 1 million de cycles d'écriture (contre 10000 à 1 milliard, un grand écart, pour la version finale) ce qui laisse penser que le prototype ne se comporte peut être pas aussi bien qu'espéré.

Vous noterez enfin que le nombre de cycles d'écritures accordés à la NAND, de 500 à 1000 est particulièrement faible. 3000 cycles serait un peu plus réaliste.

Au-delà de tout ce méli-mélo de marketing, et dans l'absence de vraies données techniques (on ne sait pas par exemple en quel finesse de gravure a été produit le prototype, une des difficultés de la RRAM étant d'utiliser les finesses de gravures les plus faibles) difficile de juger ce qu'a réellement produit cette startup, probablement en recherche de capitaux ou d'un rachat. On suivra avec attention d'éventuelles évolutions sur le sujet assez crucial, dans cette startup ou dans d'autres acteurs du marché.

La V-NAND en production chez Samsung !

Le géant coréen vient d'annoncer la mise en production de sa technologie V-NAND, un nouveau type de mémoire flash conçu pour améliorer la densité. La V-NAND combine deux innovations par rapport à la mémoire flash NAND traditionnelle.

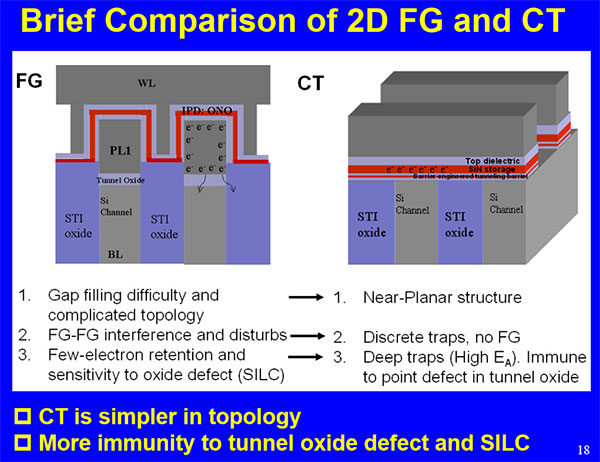

D'abord sur le fonctionnement même du stockage, la NAND traditionnelle utilise des transistors de type floating-gate pour stocker les informations. La V-NAND se distingue en utilisant un autre type de structure, dit charge-trap.

Schéma extrait de cette présentation de Macronix

La floating-gate est ici remplacée par une couche de nitrure de silicium, ce qui donne l'avantage d'une structure planaire plus facile à produire. Il ne s'agit pas en soit d'une technologie nouvelle puisque le concept date des années 70 et avait été popularisé par AMD et Fujitsu avec la mémoire flash NOR MirrorBit. Son application à la NAND avait été étudiée à plusieurs reprises, son inconvénient principal dans les structures traditionnelles SONOS (Silicon-Oxide-Nitride-Oxide-Silicon) étant qu'il est difficile de cumuler vitesse d'effacement rapide et rétention, bien qu'individuellement sur ces points la CT soit théoriquement plus intéressante que la NAND floating-gate. Depuis, des alternatives au SONOS utilisant par exemple des diélectriques high-k ont été mises au point.

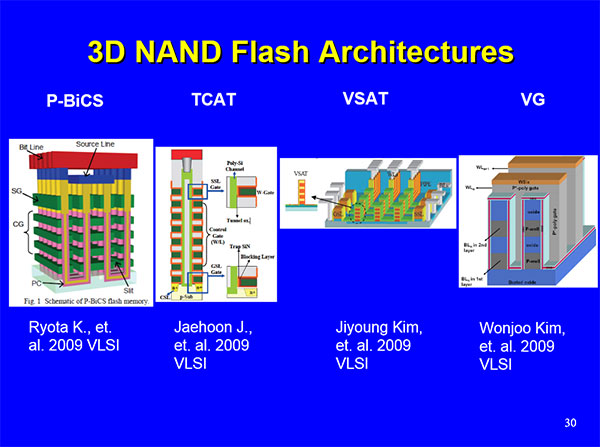

L'autre innovation consiste à produire ces structures de manière verticale, plutôt que de manière planaire. Samsung n'est pas le seul à travailler sur le sujet puisque Toshiba , dès 2007, avait proposé une structure de ce type que vous pouvez voir en image ci-dessous (la couche en rouge du schéma au-dessus est ici en (tube) jaune) :

En utilisant des structures verticales, il est possible d'améliorer significativement la densité de données, sans pour autant faire exploser les coûts. Plusieurs types de structures verticales étaient d'ailleurs à l'étude, Toshiba privilégiant sur le schéma ci-dessus une structure BiCS (Bit Cost Scalable) tandis que Samsung travaillait sur deux alternatives. Tout d'abord le TCAT (Terrabit Cell Array Transistor), une version améliorée du BiCS qui permet l'utilisation de diélectriques high-k et le VG-NAND (Vertical Gate NAND) dont la structure est un peu plus complexe :

Bien que le communiqué ne le précise pas exactement, nous supposons d'après certains termes utilisés dans le communiqué que c'est l'approche TCAT qui a été retenue, il s'agit en prime de celle qui semblait la plus prometteuse en termes de coûts. Le communiqué indique que Samsung pourrait en théorie placer jusqu'à 24 couches en hauteur, sans préciser le nombre de couches utilisées dans les premières puces.

Côté performances et caractéristiques, là encore le communiqué est flou et il faudra probablement attendre de voir les fiches techniques des puces pour avoir des informations précises. Samsung indique simplement que la V-NAND permet par rapport à de la NAND classique gravée en 1xnm (19nm probablement) d'augmenter la longévité des puces par un facteur compris entre 2 et 10x, tandis que les performances en écritures seraient doublées. Samsung se garde par contre d'indiquer quelle est la finesse de gravure utilisée pour cette V-NAND.

Il sera important de voir quelles seront les caractéristiques commerciales des puces, mais également leur prix ! La première proposera une densité de "seulement" 128 Gbit, une taille déjà atteinte avec des technologies classiques, avec pour objectif d'atteindre le Terabit sur une seule puce à terme via cette technologie.

N760 HAWK, une GTX 760 boostée chez MSI

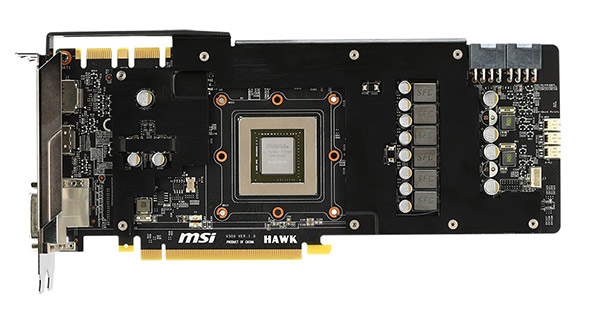

MSI va lancer une nouvelle GTX 760, la N760 HAWK. Histoire de faire simple (sic), cette carte reprend les couleurs de la gamme Lightning mais pas le nom, qui est désormais réservé aux cartes disposant du GPU Reactor (cf. en bas de page).

Par rapport la N760 TF 2GD5/OC (la GTX 760 actuelle de MSI, en version Gaming), on note en fait que la carte reprend en très grande partie le design de la N770 TF 2GD5/OC (version Gaming également) que ce soit au niveau du PCB ou du radiateur. MSI a par contre rajouté quelques fonctions pour l'overclocking, comme des points de mesure de tension et un second bios destiné à l'overclocking extrême (il désactive les protections contre les surintensités et la gestion dynamique du nombre de phases actives).

Le PCB intègre donc désormais 6 phases pour le GPU au lieu de 5, toutes placées à l'arrière de la carte et non plus à l'avant. Une plaque métallique est utilisée pour assurer la rigidité du PCB, elle est en contact avec les modules mémoire ainsi que les composants sensibles de l'étage d'alimentation. Une seconde plaque métallique est située à l'arrière de la carte.

L'alimentation du PCB se fait désormais via deux connecteurs PCI Express 8 pins (au lieu de 6+8 pins), et si le refroidissement est toujours de type Twin Frozr IV c'est ici une version à 5 caloducs : 1 de 8mm et 4 de 6mm (contre 1+3 sur la GTX 760 Gaming). La fréquence de base du GPU est légèrement revue à la hausse, 1111 MHz pour un boost à 1176 MHz, contre 1085 et 1150 MHz pour la version Gaming.

La MSI N760 HAWK devrait être disponible aux alentours de la mi-août au prix conseillé de 289 TTC.

IBM ouvre un peu plus l'architecture Power

Développée par IBM à la fin des années 80, l'architecture Power est une architecture RISC développée à l'origine pour des utilisations type station de travail et serveur, et qui a connu son heure de gloire avec l'alliance Apple/IBM/Motorola dans les années 90 pour produire ce qui deviendra l'architecture PowerPC, dérivé grand public de l'architecture Power.

Cette architecture Power est progressivement ouverte (par le biais de power.org ) depuis 2004 dans le cadre d'usages "grand public", et a été utilisée dans des co-développements comme le Cell avec Sony et Toshiba, ou des utilisations embarqués comme le PA6T de P.A. Semi. IBM a continué cependant en parallèle de développer la déclinaison serveur haut de gamme avec des processeurs comme les POWER4/5/6/7 destinés à des serveurs fabriqués exclusivement par IBM.

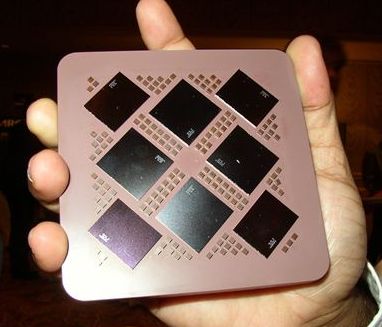

L'un peu encombrant Power5 en version MCM (Multi Chip Module) proposait 8 curs en 2003

La concurrence extrêmement forte du x86 sur le marché serveur aura probablement poussé IBM à vouloir changer de stratégie puisque le géant américain vient d'annoncer l'ouverture à licence des technologies propriétaires autour de la déclinaison serveur des POWERn, y compris les technologies relatives aux futurs POWER8.

Le constructeur essaye donc de créer un écosystème autour de ses serveurs en ouvrant le firmware (BIOS) en open source, ce qui permettra l'arrivée de partenaires côté cartes mères. Le communiqué de presse annonce l'arrivée de Tyan pour remplir ce rôle dans le nouveau consortium open-power.org , mais aussi de Nvidia dans le but d'intégrer ses GPU et Mellanox pour les interconnexions. Google fait également partie des membres du futur consortium, sans que son rôle soit précisé. Si l'ouverture d'une architecture de plus, qui plus est très focalisée sur les hautes performances est toujours une bonne chose, il faudra voir si en pratique cela permettra de relancer l'activité plutôt en berne d'IBM sur le marché des serveurs suite à la forte concurrence des x86 très abordables en comparaison.