AMD Radeon HD 7790 et GeForce GTX 650 Ti Boost en test

Publié le 22/03/2013 (Mise à jour le 08/04/2013) par Damien Triolet

Bonaire et GCN 1.1 pour la HSA ?

Bonaire est basé sur l'architecture GCN, comme les autres GPU de la gamme Radeon HD 7000. Vous pourrez en retrouver le détail ici. Rappelons grossièrement que cette architecture repose sur des blocs fondamentaux appelés Compute Units (CU) qui intègrent chacun 64 unités de calcul (les "cores" en langage marketing), 4 unités de texturing, des caches et toute la logique de contrôle nécessaire au bon fonctionnement de l'ensemble. Voici résumées les spécifications des 5 GPU GCN actuels :

Oland : 6 CU, 1 triangle par cycle, 16 ROP, 128 bits

Cape Verde : 10 CU, 1 triangle par cycle, 16 ROP, 128 bits

Bonaire : 14 CU, 2 triangles par cycle, 16 ROP, 128 bits

Pitcairn : 20 CU, 2 triangles par cycle, 32 ROP, 256 bits

Tahiti : 32 CU, 2 triangles par cycle, 32 ROP, 384 bits

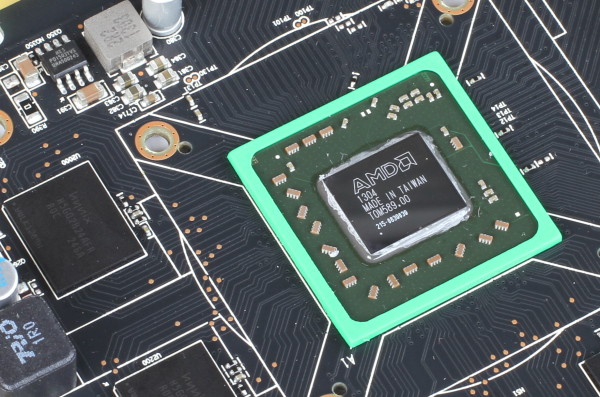

Comme les autres GPU de la famille GCN, Bonaire est fabriqué en 28 nanomètres chez TSMC. AMD ne précise pas la variante du process, mais nous supposons que tous ces GPU exploitent le 28 nm HPL, à l'exception de Tahiti qui exploiterait le 28 nm HP, raison pour laquelle les résultats de ce GPU sont plus variables en terme de consommation ainsi que de tension / fréquence lors d'overclockings.

Alors que Cape Verde se contente de 1.5 milliards de transistors et d'une surface de 123 mm², Bonaire passe à 2.1 milliards de transistors et 158 mm², ce qui reste plus petit que les 2.8 milliards de transistors et 212 mm² de Pitcairn mais aussi que les 2.5 milliards de transistors et 214 mm² du GK106.

L'architecture GCN évolue légèrementBien qu'AMD ne mette en avant ce point, ou tout du moins évite d'en parler, Bonaire introduit une légère évolution de l'architecture GCN qui pourrait être qualifiée de 1.1 (ce que ne fait pas AMD pour le moment). Ces évolutions concernent principalement le processeur de commande du GPU et sont destinées au GPU compute et à la HSA (Heterogeneous System Architecture).

Parmi les évolutions, notons le support de 8 files d'attente par compute pipeline, ce qui va dans le sens de la technologie Hyper Q de Nvidia réservée aux Tesla K20 et permet de mieux alimenter le GPU en évitant que lors de dépendances entre kernels (programmes à exécuter), le GPU ne se retrouver bloqué en attendant le résultat de l'un d'eux. Nous supposons ici que par compute pipeline AMD entend ACE (Asynchronous Compute Engine) et que les 2 ACE de Bonaire permettent de supporter 16 files d'attente.

Un adressage mémoire unifié est également au programme et de nouvelles instructions font leur apparition dont certaines dédiées au débogage du code.

Voici un extrait du document qui détaille l'évolution du jeu d'instruction mais qui a été retiré par AMD le temps d'en corriger certaines notations qui étaient peu claires au niveau du nom des différentes architectures :

Important differences between xx and yy GPUs

Multi queue compute

Lets multiple user-level queues of compute workloads be bound to the device and processed simultaneous. Hardware supports up to eight compute pipelines with up to eight queues bound to each pipeline.

System unified addressing

Allows GPU access to process coherent address space.

Device unified addressing

Lets a kernel view LDS and video memory as a single addressable memory. It also adds shader instructions, which provide access to flat memory space.

Memory address watch

Lets a shader determine if a region of memory has been accessed.

Conditional debug

Adds the ability to execute or skip a section of code based on state bits under control of debugger software. This feature adds two bits of state to each wavefront; these bits are initialized by the state register values set by the debugger, and they can be used in conditional branch instructions to skip or execute debug-only code in the kernel.

Support for unaligned memory accesses

Detection and reporting of violations in memory accesses

New instruction formats:

FLAT

New instructions:

FLAT_* (entire family of operations)

S_CBRANCH_CDBGUSER

S_CBRANCH_CDBGSYS

S_CBRANCH_CDBGSYS_OR_USER

S_CBRANCH_CDBGSYS_AND_USER

S_DCACHE_INV_VOL

V_TRUNC_F64

V_CEIL_F64

V_FLOOR_F64

V_RNDNE_F64

V_QSAD_PK_U16_U8

V_MQSAD_U16_U8

V_MQSAD_U32_U8

V_MAD_U64_U32

V_MAD_I64_I32

V_EXP_LEGACY_F32

V_LOG_LEGACY_F32

DS_NOP

DS_GWS_SEMA_RELEASE_ALL

DS_WRAP_RTN_B32

DS_CNDXCHG32_RTN_B64

DS_WRITE_B96

DS_WRITE_B128

DS_CONDXCHG32_RTN_B128

DS_READ_B96

DS_READ_B128

BUFFER_LOAD_DWORDX3

BUFFER_STORE_DWORDX3

Removed instructions:

V_QSAD_U8

V_MQSAD_U8

BUFFER_ATOMIC_RSUB, _X2

IMAGE_ATOMIC_RSUB, _X2

Sommaire

1 - Introduction

2 - Bonaire et GCN 1.1 pour la HSA ?

3 - Spécifications, PowerTune, GTX 650 Ti Boost

4 - Performances théoriques : pixels

5 - Performances théoriques : géométrie

6 - Sapphire Radeon HD 7790 Dual-X OC

7 - Consommation, efficacité énergétique

8 - Protocole de test

9 - Benchmark : Alan Wake

10 - Benchmark : Anno 2070

11 - Benchmark : Assassin's Creed 3

12 - Benchmark : Batman Arkham City

13 - Benchmark : Battlefield 3

2 - Bonaire et GCN 1.1 pour la HSA ?

3 - Spécifications, PowerTune, GTX 650 Ti Boost

4 - Performances théoriques : pixels

5 - Performances théoriques : géométrie

6 - Sapphire Radeon HD 7790 Dual-X OC

7 - Consommation, efficacité énergétique

8 - Protocole de test

9 - Benchmark : Alan Wake

10 - Benchmark : Anno 2070

11 - Benchmark : Assassin's Creed 3

12 - Benchmark : Batman Arkham City

13 - Benchmark : Battlefield 3

14 - Benchmark : BioShock Infinite

15 - Benchmark : Civilization V

16 - Benchmark : Crysis 3

17 - Benchmark : DiRT Showdown

18 - Benchmark : Far Cry 3

19 - Benchmark : Hitman Absolution

20 - Benchmark : Max Payne 3

21 - Benchmark : Sleeping Dogs

22 - Benchmark : The Witcher 2 Enhanced Edition

23 - Benchmark : Tomb Raider

24 - Benchmark : Total War Shogun 2

25 - Récapitulatif des performances

26 - Conclusion

15 - Benchmark : Civilization V

16 - Benchmark : Crysis 3

17 - Benchmark : DiRT Showdown

18 - Benchmark : Far Cry 3

19 - Benchmark : Hitman Absolution

20 - Benchmark : Max Payne 3

21 - Benchmark : Sleeping Dogs

22 - Benchmark : The Witcher 2 Enhanced Edition

23 - Benchmark : Tomb Raider

24 - Benchmark : Total War Shogun 2

25 - Récapitulatif des performances

26 - Conclusion

Vos réactions

Contenus relatifs

- [+] 30/01: AMD Mantle arrive, patch pour BF4 à...

- [+] 07/10: Baisse (temporaire ?) des GTX 660 e...

- [+] 14/08: AMD annonce son bundle Never Settle...

- [+] 05/08: Never Settle Forever, nouveau souff...

- [+] 15/05: AMD muscle Never Settle Reloaded

- [+] 17/04: Radeon HD 7790 2 Go, pourquoi faire...

- [+] 12/04: Bundle: AMD ajoute Far Cry 3 Blood ...

- [+] 08/04: Test : Nvidia GeForce GTX 650 Ti Bo...

- [+] 08/04: AMD Radeon HD 7790 et GeForce GTX 6...

- [+] 26/03: Nvidia lance le GeForce GTX 650 Ti ...