Les contenus liés au tag ASML

Afficher sous forme de : Titre | FluxTSMC va céder sa participation dans ASML

En 2012, le fabriquant d'outils de photolithographie ASML avait ouvert son capital à ses clients. Conjointement à des prises de participation de 15%, 5% et 3% pour Intel, TSMC et Samsung, ces clients avaient investis un total de 1,1 milliards d'euros afin de financer le développement de la lithographie EUV et de la transition vers des wafer de 450mm.

Les trois industriels ne pouvaient pas vendre leurs titres avant deux ans et demi et TSMC profite de la levée du blocage en avril prochain pour annoncer qu'il a passé au cours de l'année précédente des contrats avec plusieurs fonds afin de revendre ses 21 millions d'actions acquises à 39,91 pièce au tarif de 62,59 . Si la plus-value parait sympathique, TSMC ne profitera par contre pas de la récente hausse du court d'ASML, le titre étant passé de 70 à 88 au cours des trois derniers mois.

Au-delà de l'opération financière il est improbable que cela signifie quoi que ce soit vis-à-vis des relations qu'entretiennent TSMC et ASML. Alors qu'il y a 10 ans ASML, Canon et Nikon se partageaient le marché, ASML est depuis monté en puissance avec près de 80% du marché !

L'EUV prêt chez ASML pour 2015 ?

Nos confrères d'IEEE Spectrum viennent de publier un article relatant des nouvelles assez optimistes en provenance d'ASML.

Elles concernent bien entendu la photolithographie EUV, un point de plus en plus critique pour le développement des futures technologies de lithographie au-delà de 2015. Pour rappel, les procédés de photolithographies actuels reposent tous sur des sources lumineuses d'une longueur d'onde de 193nm, repoussée aujourd'hui dans ses derniers retranchements au travers de multiples techniques comme le patterning multiple. L'EUV apportera une source lumineuse plus flexible dont la longueur d'onde sera de seulement 13 nm, et dont la nécessité se fait de plus en plus pressante avec l'approche de la finesse de gravure 10 nm (attendue théoriquement pour 2015, mais peut être plus probablement pour 2016) où la technologie est vue comme quasi indispensable par beaucoup (Intel avait évoqué avoir mis au point une alternative "non EUV" en cas d'une nouvelle défaillance).

Le fournisseur d'outil ASML travaille depuis des années sur des machines de photolithographie EUV avec un succès relativement modéré, quelque chose que l'on doit à la grande complexité du problème qu'ils tentent de résoudre. Nous vous avions rapporté l'été dernier qu'ASML avait ouvert son capital à ses clients dans le but d'obtenir un financement spécifique pour accélérer le développement de la lithographie EUV. Intel avait ainsi investi 3.3 milliards d'euros, suivi rapidement par TSMC et Samsung.

De multiples problèmes restent à résoudre du côté de l'EUV, le principal étant l'intensité de la source lumineuse utilisée qui impacte directement le débit de la machine. Pour que la technologie soit économiquement viable, Mark Bohr d'Intel estimait qu'un débit de 50 à 100 wafers par heure était nécessaire. Un chiffre significativement plus important que les niveaux de production actuels des machines de préproduction EUV, plus proches de la dizaine de wafer par heure. Malgré tout, nous avions noté en avril que TSMC était confiant sur la possibilité de fabriquer, avec ASML, du 10nm EUV dès 2015.

Durant la conférence Semicon West , ASML a donné de nouveau détails et présenté une roadmap pour atteindre la mise en production en 2015 avec un objectif de 125 wafers/heure. Les avancées reposent en partie sur le rachat de la société Cymer en mai dernier par ASML. Cette société développe des sources lumineuses EUV qui combinent des minuscules goutes d'étain avec un laser pour créer un plasma qui emet à son tour de la lumière EUV. Une des avancées de Cymer concerne l'ajout d'un second laser en amont pour améliorer le rendement du laser principal. La technologie a déjà été appliquée sur une machine de préproduction d'ASML en mars dernier avec un rendement "stable" de 30 wafers par heure via une source lumineuse 40 watts.

ASML dispose désormais d'une roadmap - via Cymer - pour atteindre les 250 watts qui seront nécessaire à atteindre le niveau de production de 125 wafers/h en 2015 sur leurs machines de production NXE:3300B . La société pense pouvoir démontrer, d'ici à la fin de l'année un rendement - stable - de 80W. Un des problèmes des sources lumineuses EUV à l'étude était qu'au-delà de la puissance souvent trop faible, les valeurs annoncées étaient souvent en pointe et pas vraiment reproductibles dans la durée. Sur ce point ASML tente de rassurer indiquant avoir obtenu un niveau de qualité constant sur des tests répétés de plus de 40 heures d'affilés.

Si ces nouvelles sont plutôt bonnes en ce qui concerne les sources lumineuses, il ne s'agit bien entendu pas du seul problème à résoudre. Le niveau de défaut dans la fabrication des masques est un autre obstacle majeur sur lesquels les différents acteurs de l'industrie devront travailler en parallèle.

16nm en 2013, 10nm EUV en 2015 chez TSMC

Nos confrères d'EE Times ont publié le résumé d'une présentation par TSMC de ses nodes à venir, un article dans lequel on peut relever quelques informations intéressantes.

TSMC revient d'abord rapidement sur l'état de son node 28nm. Sa Gigafab 15 produirait aujourd'hui 50000 wafers dans ce node par mois. Cette quantité devrait cependant rapidement doubler avec la mise en route de la seconde tranche de la Gigafab 15. La production devrait démarrer d'ici un mois et arriver, d'ici cinq mois, à un débit de production identique à la première tranche.

En ce qui concerne le 20nm, TSMC donne quelques détails intéressants. Avec l'arrivée du double patterning sur ce node, les gains habituels de densité et de performances devraient être réduits, une tendance que l'on avait déjà entendue du côté de la Common Platform. Le 20nm sera vraisemblablement un node de transition vers le FinFET (le node suivant en 16nm), même si TSMC se refuse de le dire. Côté performances, quelques chiffres ont été donnés à savoir 20% de fréquence en plus, ou 30% de consommation en moins par rapport au 28nm, ce qui reste tout de même assez élevé. Une vingtaine de tapeouts sont attendus cette année dans les Gigafab 12 et 14 avec une production en volume pour 2014. Parmi ceux-ci, un Cortex-A15 20nm est attendu pour le mois de mai.

Pour le 16nm, le développement du node est actuellement en cours en parallèle, on se souvient de cette annonce en début de mois d'un premier tapeout de Cortex-A57. Assez peu de détails sont donnés, si ce n'est que les premiers wafers de tests clients pourraient être lancés vers la fin de l'année avec une production qui monterait (probablement très doucement) en volume en 2014. Actuellement, TSMC travaille principalement sur des structures SRAM 128 Mbit dont les yields sont en avance par rapport aux estimations. Si les blocs logiques ont déjà été testés (cf l'annonce du Cortex), les blocs d'interface (mémoire ou autre) devraient commencer à être testés en juin.

De manière beaucoup plus surprenante, TSMC à indiquer espérer produire d'ici 2015 des wafers 10nm utilisant la technologie EUV. Pour rappel, TSMC a investit également dans le fournisseur d'outils ASML.

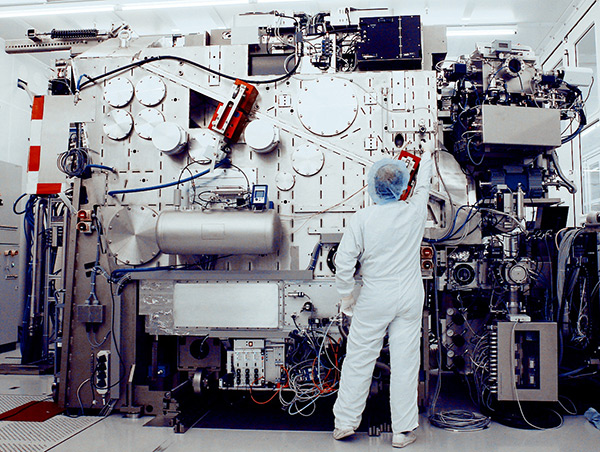

Une machine EUV ASML

La firme se réserve cependant assez prudente, indiquant qu'elle ne dispose toujours pas du dernier modèle d'outil de ASML (le NXE:3300 ). TSMC indique également continuer a travailler sur une technologie alternative pour ce node, le multiple electron beams sur lequel TSMC avait annoncé travailler avec MAPPER . La particularité de la technologie est qu'il ne s'agit plus littéralement de photolithographie, le masque disparaît et la source lumineuse est remplacée par des flux d'électrons qui viennent réagir avec un film préalablement déposé sur le wafer. Le débit de ces machines est qualifié par TSMC "d'encore trop lent", même s'il n'est pas comparé à celui, lui aussi très lent, de la technologie EUV actuellement (nous vous renvoyons a cette interview ou Mark Bohr évoquait le problème).

On notera enfin quelques informations sur les technologies de die stacking et les progrès en matière de 2.5D et 3D. Le concept du die stacking consiste à relier plusieurs dies directement entre eux par une couche de silicium, sans nécessiter de fils (des TSVs, Through Silicon Vias, sont utilisésà la place, ce qui permet d'augmenter significativement la bande passante et réduire la complexité). Les technologies dont on parle visent à terme à relier plusieurs dies logiques entre eux même si ce n'est pour l'instant qu'un objectif lointain.

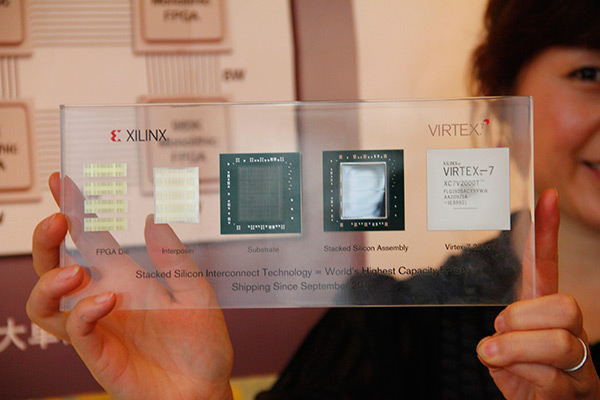

La technologie 2.5D consiste à placer côte a côte deux dies, qui reposent sur un interposer qui contient lui-même des TSV pour interconnecter les dies. L'épaisseur de cet interposer est actuellement de 100nm mais devrait se réduire de moitié. Xilink propose actuellement un FPGA fabriqué sur le process 28HPL de TSMC qui interconnecte quatre dies, le Virtex 7 2000T.

Sur cette photo de nos confrères de 52solution , vous pouvez voir à gauche les quatre dies logiques et l'interposer. La puce assemblée est en quatrième position.

TSMC indique que les yields obtenus dépassent les 95% sur les interposers utilisés pour cette puce et plusieurs autres tape-outs devraient avoir lieu cette année, sans plus de précision. TSMC continue de travailler sur le sujet de Wide I/O avec des puces de test qui lient un die 40nm avec une puce mémoire Hynix, un montage qui a passé les tests de validation du JEDEC.

En ce qui concerne la superposition de dies (la "vraie" 3D), TSMC pense effectuer le tapeout d'une puce 28nm avec sur chaque couche des dies mémoire, avant de passer au mélange logique/mémoire. Il faudrait cependant attendre 2015 ou 2016 pour retrouver ces puces en production selon TSMC.

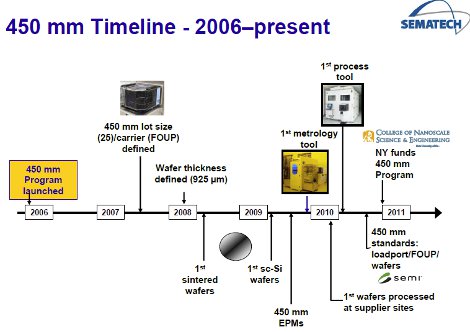

Notons enfin qu'en ce qui concerne le 450mm (la taille des wafers, elle est actuellement de 300mm de diamètre pour les nodes haut volume de TSMC), la production ne devrait pas démarrer au mieux avant 2016 voir 2017 malgré des tests en cours. Les outils EUV sont ceux qui poseront - là encore- le plus de problème selon TSMC, ils pourraient ne pas arriver avant 2017 en version 450mm.

Impact de l'EUV et du 450mm selon Intel

Nos confrères de X-bit Labs rapportent des propos tenus par Paul Otellini lors d'une conférence technologique organisée par la firme Sanford Bernstein, CEO en partance d'Intel, concernant les transitions à venir sur le marché des semiconducteurs.

Selon Paul Otellini, plusieurs transitions à venir dans la décennie (le passage de wafers 300mm vers 450mm et l'utilisation de la lithographie EUV) pourraient avoir un impact fort sur les acteurs du marché, le futur ex CEO indiquant qu'historiquement, seule la moitié des acteurs du marché survivaient à un changement de taille de wafers.

Contrairement à Intel et comme nous l'avions évoqué précédemment, le reste de l'industrie n'est en effet pas particulièrement pressé de passer au 450mm, une transition maintes fois retardée même si l'on avait noté il y à un peu plus d'un an de cela un début d'accord de la part des principaux acteurs côté fabrication. On avait d'ailleurs vu Intel, TSMC et Samsung investir successivement dans le fournisseur d'outil ASML.

L'impact du 450mm touchera probablement plus, et c'est ce que soulignait Paul Otellini, les acteurs dits fabless qui n'auraient pas des besoins en volume aussi importants que les autres, ou qui pourraient souffrir encore plus qu'actuellement de problèmes d'allocation sur les process de fabrication dernier cri. On avait vu récemment Qualcomm et Apple tenter de négocier par un investissement de plus d'un milliards de dollars des droits de productions exclusifs sur certaines usines.

TSMC investit aussi dans ASML

Après Intel le mois dernier, c'est aujourd'hui TSMC qui annonce un investissement dans la société de fourniture d'outils de photolithographie ASML. A l'image de l'investissement réalisé par Intel, celui de TSMC est lui aussi découpé en deux portions avec tout d'abord 276 millions d'euros sur cinq années pour financer le développement de deux technologies clefs : la lithographie EUV ainsi que la transition vers des wafers de 450mm de diamètre (contre 300 actuellement). L'autre partie de l'investissement consiste en une prise de capital de 5% du constructeur pour un montant de 838 millions d'euros.

ASML aura ainsi distribué 20% des parts de son entreprise à ses clients (15% à Intel en plus des 5% évoqués ici) par le biais de ce programme de co-investissement. 5% des parts de la société restent à prendre, ASML ayant décidé d'en distribuer jusque 25%.