Les derniers contenus liés aux tags GlobalFoundries et ASML

GlobalFoundries : 12nm, 7nm et EUV

TSMC confiant sur l'EUV en volume pour 2019

GlobalFoundries confirme son process 7nm pour 2018

ASML investit dans Carl Zeiss SMT pour l'EUV

Premières puces en 7nm pour IBM !

GlobalFoundries : 12nm, 7nm et EUV

Nos confrères d'Anandtech ont publié une (longue) interview de Gary Patton , l'actuel CTO de GlobalFoundries. Son nom vous est peut être familier dans un autre contexte, il était auparavant en charge du R&D semiconducteurs chez IBM et plus globalement de l'alliance "Common Platform" qui liait IBM, GlobalFoundries et Samsung.

L'alliance n'est plus, l'activité semi d'IBM a été repris par GlobalFoundries (avec la transition des équipes techniques) et si GlobalFoundries et Samsung ont "partagé" le 14nm, c'est avant tout parce que GlobalFoundries avait raté son développement interne et adopté sous licence le process de Samsung. Comme nous avions eu l'occasion de vous l'indiquer, ce partenariat n'a pas duré, les relations entre GlobalFoundries et Samsung ayant été excessivement mauvaises.

En récupérant l'activité d'IBM, GlobalFoundries a récupéré un process 7nm en cours de développement et c'est celui ci qui sera utilisé par la société (voir cet article d'une interview précédente). Sur ce point, Gary Patton a confirmé les détails donnés précédemment, à savoir une version optique avant l'introduction en cours de node de l'EUV sur certaines couches (la méthode adoptée également par TSMC).

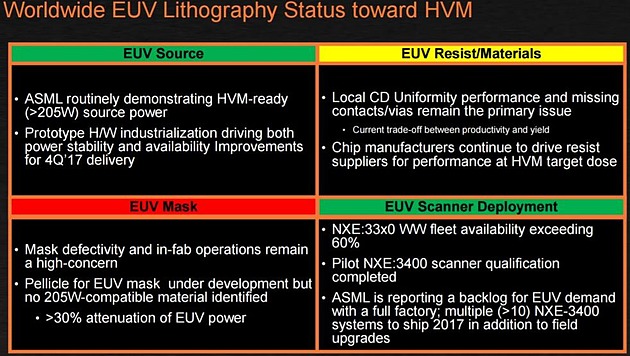

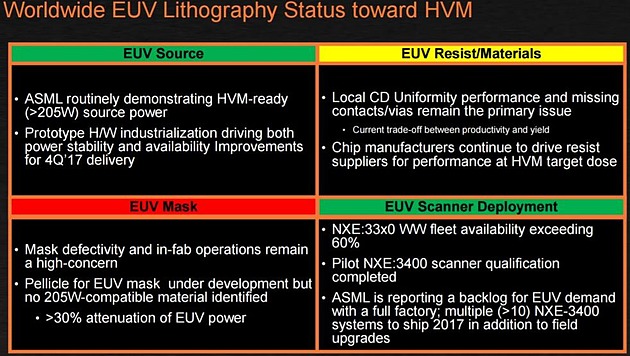

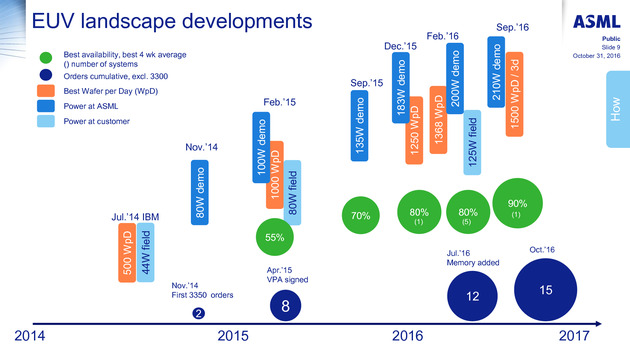

Pour l'EUV Gary Patton dit d'ailleurs ne plus avoir de doutes : le taux de disponibilité des machines serait aujourd'hui à 75% (avec pour objectif d'atteindre 85%) et la source lumineuse 250W semble être prête également côté ASML. La question du pelliculage des masques reste le gros frein même si des progrès ont été notés.

Dans ce slide de l'été dernier de Gary Patton, le pelliculage créait une atténuation de plus de 30% de la source lumineuse, et uniquement avec des sources lumineuses de moins de 205W. Aujourd'hui des matériaux semblent avoir été trouvés pour tenir 250W, et l'atténuation ne serait "que" de 20% ce qui est un net progrès.

La première version du 7nm (sans EUV) est toujours prévue en production volume vers la fin de l'année "ou plus probablement début 2019" ce qui semble être raccord avec ce que l'on a pu entendre jusqu'à présent.

A propos du 12nm qui va être utilisé par les Ryzen+, on sera surpris de voir Gary Patton indiquer que cette variante de 14nm n'est pas encore considérée en production "volume", mais que la production est pour le premier trimestre (les Ryzen+ sont attendus dès la mi-avril sur ce process). L'interview confirme des modifications principalement sur le passage 9T vers 7.5T et des améliorations sur le BEOL par rapport au 14nm.

L'interview dont l'on vous recommande la lecture balaye de nombreux autres sujets. On appréciera particulièrement la candeur du CTO en début d'interview sur les problèmes d'exécution de GF les année passées, si l'on lit entre les lignes il semble que le retard sur le 7nm soit assez léger (l'année dernière, GF avait indiqué s'attendre a voir des produits courant 2018 ce qui nous avait paru optimiste) et cohérent avec l'annonce d'un "Vega 7nm" vers la toute fin d'année.

TSMC confiant sur l'EUV en volume pour 2019

TSMC a également annoncé ses résultats un peu plus tôt dans le mois, l'occasion d'une conférence auprès des analystes qui aura été la dernière de Morris Chang, le Chairman et fondateur de TSMC. Il avait annoncé en fin d'année dernière qu'il prendrait sa retraite en juin 2018.

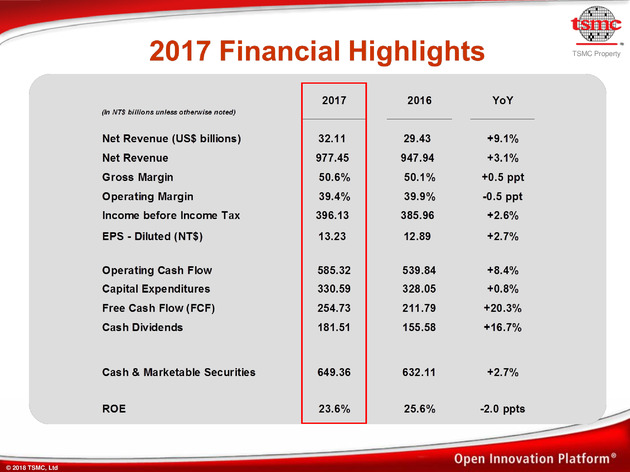

Sur l'année 2017, TSMC a réalisé un chiffre d'affaire de 32.1 milliards de dollars pour un résultat net de 11.2 milliards. Des chiffres qui progressent modestement en apparence par rapport à 2016, +3.1% et +2.6% en New Taiwan Dollar (+9.1% en dollars US, avec les effets du change).

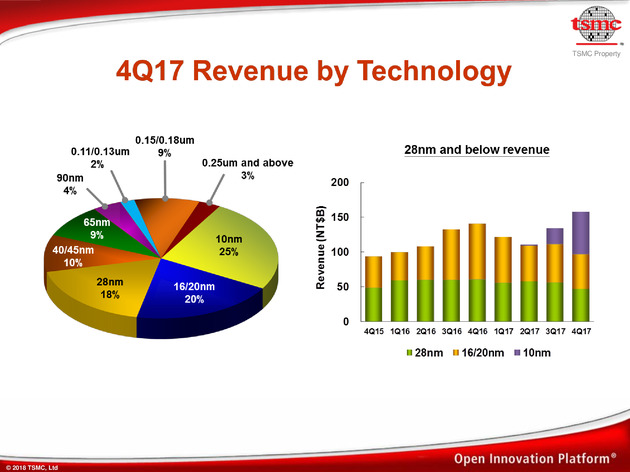

On notera que sur le dernier trimestre, le 10nm (utilisé quasi exclusivement par Apple) représente 25% du chiffre réalisé ce qui est assez massif. Sur 2017, le 10nm aura compté pour 10% du chiffre de TSMC. Les technologies "avancées", à savoir le 28nm et les nodes suivant ont compté pour 58% du chiffre d'affaire engrangé par les ventes de wafers, contre 54% en 2016.

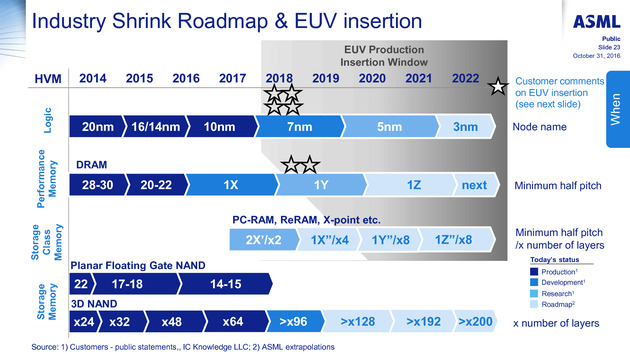

Les futurs process ont été évoqués, le 5nm (qui utilisera l'EUV chez TSMC) est prévu pour une production risque au premier trimestre 2019. TSMC indique avoir déjà atteint de bons yields sur des puces test de SRAM, et le niveau de développement est aussi avancé que pour le 7nm.

En ce qui concerne l'EUV, TSMC s'est félicité d'avoir obtenu des yields élevés en 7nm+ (la version EUV du 7nm de TSMC qui sera introduite dans un second temps) et 5nm. La question des sources lumineuses semble en passe d'être réglée, TSMC indiquant utiliser actuellement des sources 160 watts (on était à 125W l'année dernière), tandis que les sources 250W (annoncées par ASML l'été dernier) sont installées en voie de production. TSMC dit également être optimiste autour des questions compliquées autour du pelliculage avec des défauts bas. La société s'attend donc à ce que la production en volume du 7nm+ en EUV soit lancée au second trimestre 2019, et en 2020 pour le 5nm.

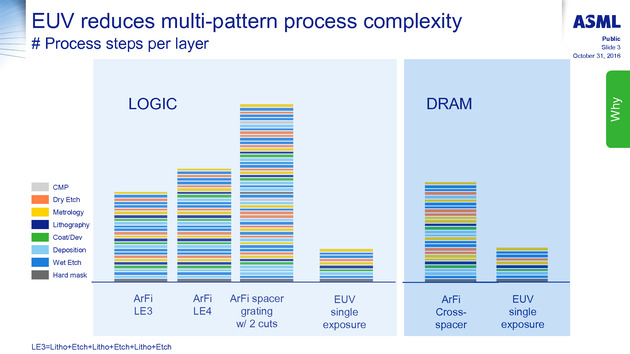

Le 7nm+ est annoncé comme 10% plus performant que le 7nm, et proposera des puces 10% plus petites en moyenne. TSMC n'a pas détaillé les gains directs obtenus en termes de réduction de couches, indiquant simplement un cas ou trois couches immersion peuvent être remplacées par une seule EUV.

Pour l'avenir proche, TSMC a annoncé avoir effectué le tapeout de 10 produits pour le 7nm (avec 10 tapeouts supplémentaires attendus au premier trimestre, et 50 attendus d'ici fin 2018), avec des qualifications en cours qui s'effectuent en parallèle dans deux fabs. Contrairement au 10nm qui n'a été utilisé que par Apple, le 7nm sera utilisé par tous les clients de TSMC. La production en volume commencera en juin et comme toujours, Apple devrait avoir la priorité (quelques produits au compte goutte pourraient être annoncés en 7nm vers la fin de l'année chez les plus petits clients de TSMC, C.C Wei indiquant qu'un décalage entre "smartphone" et HPC de quelques trimestre est attendu).

En 2018 c'est surtout en "12nm" (le 12FFC qui est la quatrième version du 16nm de TSMC) que l'on verra arriver des produits dans le monde du PC. Plus de 120 tapeouts de produits sont encore attendus sur ce node en 2018. A noter que TSMC ouvrira en mai son usine de Nanjing, en Chine, avec un peu d'avance sur son planning suite à une forte demande.

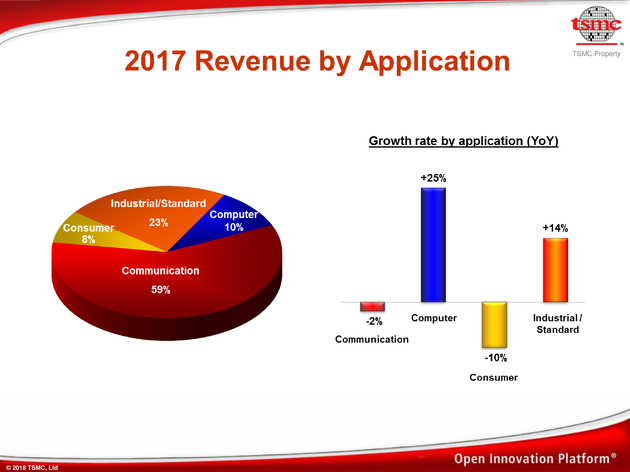

On note qu'en 2018, TSMC s'attend à ce que l'essentiel de sa croissance vienne de sa branche "high performance computing" et pointe particulièrement les GPU (...et les ASIC utilisés pour les crypto-monnaies). Morris Chang aura indiqué s'attendre à une hausse du marché du semi conducteur en 2018 comprise entre 6 et 8%.

La question de l'enquête anti-trust de la commission européenne , poussée par GlobalFoundries aura été vite balayée, TSMC indiquant rejeter les accusations de son concurrent. TSMC continue de se présenter comme la "Foundry de tout le monde" pour contrer l'argument, et tacler au passage Samsung en sous entendant qu'ils ne sont pas en compétition avec leurs clients. On terminera par un mot sur le 3nm, TSMC a indiqué qu'il continuait l'exploration de la technologie et que ces derniers mois, le manager du programme était de plus en plus positif, ne doutant plus de la simple faisabilité comme cela pouvait être le cas l'année dernière.

GlobalFoundries confirme son process 7nm pour 2018

GlobalFoundries vient par un communiqué de presse de confirmer le "lancement" de son process de fabrication 7nm pour 2018. Il s'agira cette fois ci d'un process propre à GlobalFoundries, on vous rappellera que la société, après des errements internes, avait décidé de s'offrir le process de Samsung pour le 14nm par le biais d'un accord historique. Les relations entre les deux sociétés, à ce qui nous a été rapporté, ont été tout sauf bonnes et la collaboration "complexe".

A l'époque, lorsque GlobalFoundries s'était lancé dans ce partenariat, c'était avant tout pour compenser le désengagement de plus en plus marqué d'IBM qui partageait jusqu'ici le développement de ses process avec GlobalFoundries et Samsung au sein de la Common Platform. Depuis, la société a récupéré l'activité d'IBM, des brevets, et surtout ses ingénieurs (qui avaient travaillés avant le rachat sur des process 7nm EUV).

Aujourd'hui pour ce 7nm, il s'agit bien d'un process basé sur les technologies d'IBM, nos confrères de SemiWiki ont d'ailleurs pu s'entretenir avec Gary Patton (à l'époque en charge du côté technique de l'activité semi d'IBM et aussi de la Common Platform, aujourd'hui CTO de GF) sur le sujet.

Les détails techniques restent assez légers dans l'annonce, on sait qu'il s'agit d'un process FinFET à lithographie "classique", avec l'option d'une introduction de l'EUV en cours d'exploitation. Le process portera le nom de 7LP, qui ne signifie pas "Low Power" mais "Lead Performance" et serait taillé avant tout pour les grosses puces. Dans sa plaquette commerciale (PDF) , la société met en avant les marchés serveurs, les CPU et GPU et également les puces mobiles haut de gamme. Pas de surprise étant donné qu'AMD et IBM sont deux clients clefs de la société, mais le fondeur tente de se démarquer de TSMC dont les process sont considérés, à tort ou à raison, comme optimisés spécifiquement pour les besoins d'Apple.

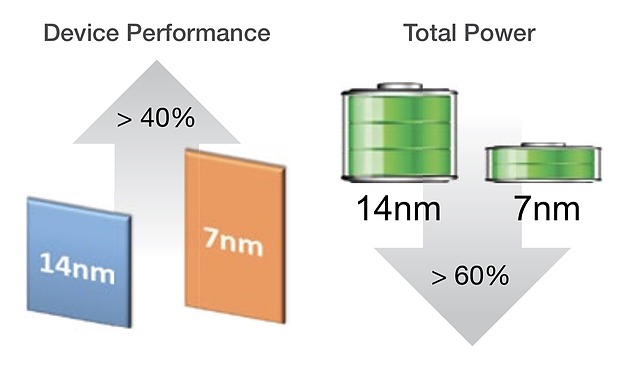

La société annonce une densité un peu plus que doublée par rapport au 14nm sans s'appesantir dans les détails. Côté performances GlobalFoundries évoque 40% de performances supplémentaires à puissance égale, ou une consommation de 60% inférieure à fréquence égale. On trouve même une bien vague mention de "5 GHz" que l'on évitera de trop interpréter ! Côté coûts, à nombre de transistors équivalent, on obtiendrait une baisse de 30% par die par rapport au 14nm.

Du côté de la disponibilité, la société indique que la production risque démarrera sur la première moitié 2018 et que l'on pourrait voir des "produits clients" dès cette date. On s'attends un peu plus à ce qu'ils arrivent avec la production en volume, prévue là encore de manière assez large pour la seconde moitié de 2018.

Pour revenir enfin sur la question de l'EUV, Gary Patton a indiqué à nos confrères de SemiWiki qu'il s'attendait à une introduction possible en 2019, sachant que les premières machines EUV dédiées à la production seraient mises en place dans la seconde moitié de cette année. Selon la société, certains problèmes persistent du côté des masques, très complexes à fabriquer. Leur pelliculage, devenu vraisemblablement nécessaire (ASML a tout fait pour l'éviter avant de céder sur la question) pose aussi de gros problèmes en réduisant la puissance de la source lumineuse de 30% (et donc la cadence des machines, un point déjà critique), mais aussi parce qu'aucun matériau n'a été trouvé pour des sources lumineuses de 205 watts (250 watts étant considéré comme la puissance qui sera utilisée par les machines d'ASML en production volume).

On restera donc assez prudents sur cette nouvelle annonce de GlobalFoundries. Si tout semble aller dans le bon sens, particulièrement pour AMD, la question de la disponibilité et des performances réelles reste entière. GlobalFoundries n'a pas non plus brillé ses dernières années par son exécution (on mettra de côté le 14nm) mais l'on peut espérer que l'apport de talents en provenance d'IBM permettra à la société de tenir des délais qui semblent très agressifs. Un produit 7nm chez AMD en 2018, même en toute fin d'année, entérinerait la fin de la domination perçue d'Intel en matière de process de fabrications face au reste de l'industrie.

ASML investit dans Carl Zeiss SMT pour l'EUV

ASML a annoncé hier qu'il comptait s'offrir un quart de Carl Zeiss SMT (24.9%) pour un montant de près de un milliard d'euros. Zeiss SMT est la filiale "Semiconductor Manufacturing Technology" du groupe allemand Zeiss spécialisé dans l'optique.

ASML indique dans son communiqué qu'il s'agit de renforcer la collaboration entre les deux sociétés, Zeiss SMT fournissant les systèmes optiques utilisés notamment dans les machines de lithographie EUV.

ASML investira en prime 220 millions d'euros dans le centre de recherche et développement de Zeiss SMT, et financera 540 millions d'investissements sur les 6 prochaines années.

L'enjeu de l'investissement, selon ASML, concerne les futures générations d'EUV avec la possibilité d'étendre la durée de vie de la technologie. Car si certains fabricants de semiconducteurs comme Samsung disent désormais (enfin !) qu'ils utiliseront l'EUV à 7nm, les très nombreux retards de la technologie font qu'elle court le risque de voir sa fenêtre d'utilisation réduite, au risque d'être remplacée par d'autres technologies.

Des systèmes optiques plus complexes avec une ouverture numérique de 0.5 (contre 0.33 pour les premières générations d'EUV) est ce que vise ASML dans cet investissement, qui ne devrait porter ses fruits que d'ici 2024. Il permettrait cependant d'étendre la durée de vie de l'EUV sous les 5nm et pour "plusieurs générations". On sait - en parallèle - qu'autour de 5nm, on atteindra les limites du silicium et l'utilisation d'autres matériaux deviendra nécessaire.

L'intérêt de la lithographie EUV est pour rappel de remplacer la source lumineuse utilisée actuellement par les scanners (elle est générée par des lasers à exciplexe Argon/Fluor avec une longueur d'onde de 193nm) par une source dont la longueur d'onde n'est que de 13.5nm, améliorant fortement les possibilités et réduisant le nombre d'étapes nécessaires pour arriver a fabriquer les puces en évitant la généralisation du multi-patterning.

ASML aurait réitéré à nos confrères d'EEtimes que quatre fabricants de puces, et deux fabricants de mémoires, se sont engagés à faire entrer l'EUV en production en 2018, quelque chose que la firme avait également indiqué dans une présentation aux investisseurs (qui évoquait 2018/2019). Une affirmation qui nous parait bien optimiste !

Aujourd'hui, seuls Samsung et GlobalFoundries se sont engagés publiquement à 7nm, pour des dates qui coïncident. En ce qui concerne TSMC, il faudra attendre le 5nm pour le voir arriver de manière extensive, sa production risque est prévue pour 2019 uniquement. Intel avait annoncé de son côté qu'il n'utiliserait pas l'EUV à 10nm, et qu'au mieux l'EUV était "une option" pour le 7nm. Le 7nm d'Intel utilisera une solution de lithographie a immersion classique. Et côté dates, 2019 semble extrêmement optimiste considérant l'exécution d'Intel ces dernières années (retards massifs sur le 14nm, introduction de Kaby Lake pour retarder le 10nm, lancement du 10nm repoussé à fin 2017 et uniquement sur des références mobiles, sans parler de l'introduction dans la roadmap de Coffee Lake en 2018... et en 14nm !).

En ce qui concerne les fabricants mémoire, Samsung avait évoqué la possibilité sans pour autant s'engager fermement. SK Hynix évoquait l'utilisation de l'EUV vers 2019.

Les machines qui seront utilisées en production, les NXE:3400B, atteindraient d'après ASML un débit de 125 wafers/heure, un progrès notable par rapport à mars 2015 ou ASML se félicitait de 42 wafers/heure (entre 50 et 100 wafers/heure étaient considérés comme le minimum pour éventuellement utiliser la technologie d'après Mark Bohr d'Intel). Pour arriver à ce chiffre, ASML devra augmenter fortement la puissance de la source lumineuse. Le constructeur aurait livré des sources 125W à ses clients cette année qui ont permis d'atteindre 85 wafers/heure.

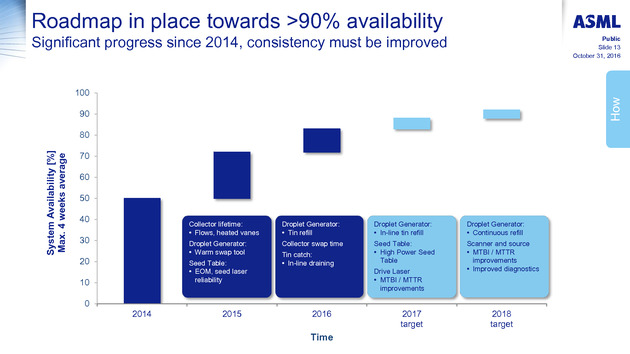

La question de la disponibilité des machines semble également être meilleure, de seulement 55% à l'époque, ASML atteint aujourd'hui entre 70 et 80%, avec l'objectif d'être a 90% en 2018.

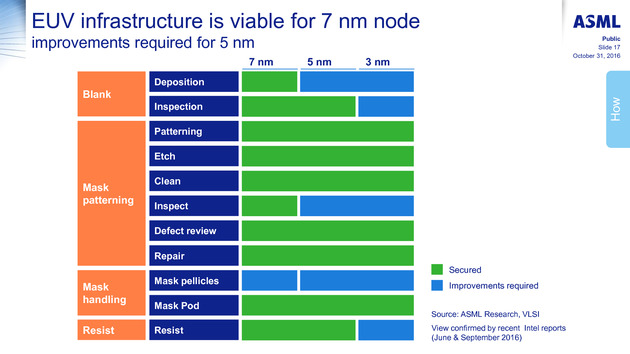

L'enthousiasme d'ASML - le seul à se lancer dans l'EUV - est forcément élevé pour sa technologie mais il faut une fois de plus rappeler que les scanners ne sont qu'une partie de la chaîne de fabrication. Les progrès réalisés, bien qu'importants, ne veulent pas dire que l'EUV est "prêt", loin de là.

La question des masques (la plaque transparente qui contient l'image de la puce à graver) et de l'inspection de leurs éventuels défauts n'a pas encore été résolue. Et si là aussi ASML tente d'apporter sa propre réponse, en pratique le problème reste complexe a solutionner avec des conséquences massives sur la viabilité de la technologie en production (plus de détails dans cet excellent article ).

Premières puces en 7nm pour IBM !

Alors qu'IBM a revendu son activité fabrication de semi-conducteurs à Global Foundries en octobre dernier (un rachat qui s'est finalisé le premier juillet de cette année), IBM vient annoncer avoir produit une puce de test fonctionnelle en 7nm, une première que rapportent nos confrères d'EETimes .

Si IBM réalise l'annonce, en pratique la puce a été fabriquée dans un centre de recherche du SUNY Polytechnic Institute financé en partie par l'état de New York et divers partenariats privés. Virtuellement toutes les sociétés du milieu participent puisque l'on retrouve dans la liste des sociétés, outre IBM, Intel, TSMC, Samsung, GlobalFoundries ou encore ASML. C'est à cet endroit que l'on retrouve par exemple l'effort de recherche du Global 450mm Consortium qui travaille sur la future transition aux wafers de 450mm (contre 300 actuellement, un mouvement qui a pris un coup d'arrêt ces dernières années).

Avant son rachat, IBM avait annoncé participer à hauteur de 3 milliards (sur 5 années) au développement de futures puces, tandis qu'en début d'année, suite au rachat par GloFo, IBM avait regroupé ses 220 ingénieurs restants sur le site de SUNY sous l'égide « IBM Research ».

Historiquement, IBM a toujours aimé jouer au jeu des annonces et continue ici dans sa tradition. En pratique il s'agit d'une première puce de test qui inclut transistors, cellules SRAM et interconnexions, les blocs essentiels même si, évidemment, on reste cependant très loin de la production en volume.

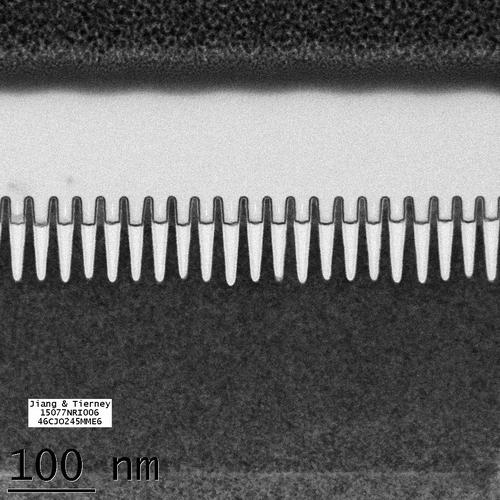

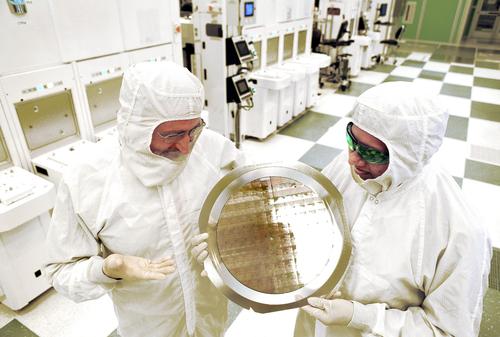

Les transistors FinFet 7nm vus au microscope

Au-delà de l'effort, on s'intéressera surtout aux choix réalisés par IBM pour son process, qui repose cette fois sur l'EUV. Nous avions eu l'occasion d'en parler, l'EUV va mieux et si une introduction est possible en cours de node pour le 10nm, TSMC et les autres visent une introduction ferme pour le 7nm et de ce côté IBM ne déroge pas.

Plus surprenant, les choix réalisés autour des structures et des matériaux. Alors que l'on s'attend probablement à voir d'autres structures que le FinFet introduites à 10 ou 7nm par Intel, IBM utilise ici des structures FinFet également, la différence s'effectuant sur les matériaux avec le retour du silicium-germanium (SiGe) étiré pour le canal, sur substrat en silicium. Ce n'est pas la première fois que le germanium apparait dans les process, même si aujourd'hui on le trouve principalement dans les process analogiques/radio . L'utilisation du SiGe étiré dans les semi-conducteurs est une innovation d'IBM et il est assez surprenant de le retrouver sur un process si avancé, qui plus est en EUV. D'autant que côté densité, les transistors peuvent être espacés de 30nm ce qui permettrait, par rapport au 10nm qui était en développement par IBM, d'augmenter la densité de 50%.

Développer un process « clef en main » - c'est comme cela qu'il est décrit par IBM qui dit avoir optimisé non seulement l'EUV, le dépôt du SiGe mais aussi les autres étapes du process comme l'interconnexion (BEOL) ne manque évidemment pas d'ironie mais nos confrères d'EEtimes notent qu'IBM fera profiter logiquement de ses travaux de recherche à GlobalFoundries qui pour rappel dispose d'une exclusivité de 10 années pour la production des processeurs serveurs d'IBM. Nos confrères sous entendent que Samsung pourrait également profiter de ces travaux, en se rappelant aux bons souvenirs de l'abandonnée Common Platform qui liait les trois sociétés.

Rien n'en est cependant moins sur puisque pour rappel, Samsung avait développé son propre process 14 nm sans IBM qui aura au final sauté ce node. Le fondeur coréen avait ensuite partagé son 14nm en intégralité avec GlobalFoundries. Pour le 10nm, IBM avait travaillé également sur son propre process que l'on retrouvera vraisemblablement tel quel chez GlobalFoundries. Les trois sociétés semblent cependant être restées en bons termes et l'on imagine que si la solution 7nm d'IBM est plus intéressante que les efforts développés en internes, ces sociétés continueront de mutualiser leurs efforts pour une éventuelle mise en production, que l'on n'attend pas de toute manière avant 2018 ou 2019. Ce que fera Samsung en 10 nm nous donnera peut-être un indice. Pour l'instant, si le constructeur a montré un wafer 10 nm, et indiqué qu'il s'attend à lancer la production en volume fin 2016, il n'a rien dévoilé sur la technique