Les contenus liés au tag Intel

Afficher sous forme de : Titre | FluxL'ITRS prépare l'après loi de Moore

Microcode anti OC chez Intel

Skylake 4+4e BGA débarque en Core i7 et Xeon E3

Les Celeron Skylake LGA 1151 arrivent

Intel fait pression sur ASRock pour SKY OC

Xeon E5-2600 v4, 1ers pas pour Broadwell-EP

Intel vient de lancer les Xeon E5-2600 v4, nom de code Broadwell-EP. Comme leurs prédécesseurs v3, Haswell-EP, ils utilisent un Socket LGA2011-v3. La gravure passe au 14nm et Intel en profite pour gonfler le nombre de coeurs quelle que soit la version du die :

- LLC : 246mm² et 3,4 milliards de transistors pour 10 coeurs

- MLC : 306mm² et 4,7 milliards de transistors pour 15 coeurs

- HLC : 456mm² et 7,2 milliards de transistors pour 24 coeurs

[ 1 ] [ 2 ]

C'est la version LLC qui sera utilisée pour les futurs Core i7 LGA2011-v3. Le 14nm permet à Intel de baisser notablement la taille des die qui était respectivement de 354, 492 et 662mm² sur leurs prédécesseurs pour 8, 12 et 18 coeurs. Malgré une hausse de 22 à 30% du nombre de transistors et de 25 à 33% du nombre de coeurs on a donc une baisse de 30 à 38% de la surface des die.

La taille du LLC reste à 2,5 Mo par coeur, et on retrouve la même configuration sur les versions MLC et HLC que sur Haswell-EP avec deux groupes de coeurs distincts avec un ring bus et un contrôleur mémoire chacun, les deux ring bus étant interconnectés. Chaque contrôleur mémoire gère alors 2 canaux contre 4 pour la version LLC.

Avant de parler des nouveautés on notera que les instructions TSX, désactivées sur Haswell-EP suite à un bug, sont de retour. En termes de microarchitecture, Broadwell apporte des améliorations mineures qui devraient tout de même apporter un gain de performance de l'ordre de 5% à fréquence égale, mais les améliorations sur l'instruction PCLMULQDQ permet d'obtenir un gain de 20 à 25% en AES et de 90% pour CRC. Le support de la DDR4 passe pour sa part la 2133 à la 2400. Enfin Intel a intégré des améliorations dédiées à la virtualisation, comme la possibilité d'observer par thread/application ou VM l'utilisation du cache et de la bande passante mémoire et de pouvoir agir sur l'allocation du cache afin d'éviter une accaparation des ressources, mais aussi la possibilité d'envoyer les interruptions externe directement à la machine virtuelle sans passer par l'hyperviseur.

[ 1 ] [ 2 ] [ 3 ]

L'unité de contrôle de la puissance a également été revue afin de mieux gérer les charges composées d'instructions AVX et d'instruction scalaires. En effet sur ces processeurs la fréquence varie notablement selon le type de charge, ainsi un E5-2699 v4 (22 coeurs et 145W) a une fréquence de base de 1,8 GHz en charge AVX pour un Turbo maximal allant de 2,6 à 3,6 GHz selon le nombre de coeurs utilisés. Hors AVX la fréquence de base est de 2,2 GHz pour 2,8 à 3,6 GHz en Turbo. Sur Haswell-EP dès qu'un coeur exécutait des instructions AVX, tous les coeurs passait en mode "AVX" avec des fréquences réduites, alors que sur Broadwell-EP coeurs exécutants des instructions scalaires peuvent utiliser des fréquences supérieures.

Bonne nouvelle côté tarif ces Xeon E5-2600 v4 sont aux mêmes tarifs que les v3 à numérotation équivalente alors même qu'ils profitent d'un nombre de coeurs en hausse de 25 à 33%. Les fréquences de base et Turbo varient un peu, parfois à la hausse parfois à la baisse. L'entrée de gamme est constitué d'un E5-2603 v4 à 213$ pour 6 coeurs à 1,7 GHz et 85W alors qu'on peut grimper à 4115$ pour les l'E5-2699 v4 offrant 22 coeurs à 2,2-3,6 GHz (hors AVX) pour 145W. Il existe 3 versions 10 coeurs :

- E5-2630L v4, 10 coeurs à 1,8-2,9 GHz pour 55W, 612$

- E5-2630 v4, 10 coeurs à 2,2-3,1 GHz pour 85W, 667$

- E5-2640 v4, 10 coeurs à 2,4-3,4 GHz pour 90W, 939$

Les dernières rumeurs font pour rappel état d'un tarif qui serait de l'ordre de 1500$ pour l'i7-6950X qui a une fréquence de base de 3 GHz et un TDP de 140W. Son lancement devrait intervenir lors du Computex en juin.

Andy Grove est décédé

Andy Grove vient de décéder à 79 ans. Titulaire d'un doctorat en génie chimique, il est le premier à rejoindre ses collègues de Fairchild Semiconductor Gordon Moore et Robert Noyce lorsqu'ils ont créé Intel en 1968. Il en devient président en 1979 puis PDG en 1987, poste qu'il occupera jusqu'en 1997 pour prendre la présidence du conseil d'administration jusqu'en 2004.

Gordon Moore, Robert Noyce et Andy Grove

Face à la concurrence japonaise, Andy Grove a joué un rôle important dans la décision de Gordon Moore de se concentrer sur les microprocesseurs et non plus sur la mémoire au début des années 1980. Sous sa direction Intel a pris une nouvelle dimension, au travers notamment du lancement du 386 et du Pentium, multipliant par 13 fois son chiffre d'affaires. Sa biographie, Seuls les paranoïaques survivent, érige en qualité la peur intense des évolutions de son marché afin de les anticiper et de s'adapter au plus tôt.

L'EUV possiblement pour le 7nm ?

Le site SemiWiki nous rapporte quelques informations sur l'état de la fabrication EUV, en provenance de la conférence SPIE Advanced Lithography qui se tient actuellement à San José.

Lors de la même conférence l'année dernière, les nouvelles étaient pour rappel plutôt bonnes (voir le lien pour un rappel complet sur la fabrication des processeurs et l'importance capitale de l'EUV !) et l'on espérait une introduction en cours de process pour le 10nm, et une introduction complète à 7nm. Malheureusement, on le rappelait en janvier, TSMC avait calmé les ardeurs en indiquant qu'il faudrait attendre le 5nm pour une éventuelle introduction de cette technologie.

SemiWiki confirme certains chiffres donnés lors de la dernière conférence aux investisseurs de TSMC, à savoir que la machine avait atteint sur une période de quatre semaines une production de 518 wafers/jour, un niveau encore largement insuffisant. Intel a partagé également quelques chiffres, un peu inférieurs à ceux de TSMC, à savoir entre 2000 et 3000 wafers par semaine (285-428 par jour).

On notera quand même que le taux de disponibilité des scanners de la société ASML a augmenté, passant de 55 à 70% chez TSMC (Intel rapportant une disponibilité identique) ! On notera que s'il est question d'une introduction en début de node à 5nm, TSMC laisse la porte ouverte pour le 7nm si jamais des progrès étaient effectués. Intel de son côté n'a pas donné d'information. Samsung envisagerait l'introduction à 7nm selon les présentations, sans plus de précisions.

Si la question de la disponibilité est importante, celle de la puissance de la source lumineuse l'est encore plus. Après avoir été limité à 40 watts l'année dernière, les machines actuellement en évaluation chez TSMC disposent désormais de sources 80 watts. C'est mieux, mais cela reste loin des 250 watts promis par ASML pour fin 2015. Les dernières prédictions sont désormais de 250 watts en 2016-2017, et au delà en 2018-2019, des plages particulièrement larges.

Atteindre les 250 watts de puissance permettrait d'augmenter significativement la cadence de production, atteignant 170 wafers/heure en théorie. ASML a effectué des démonstrations que TSMC et Intel semblent juger prometteuses de 185 et 200 watts. Reste à les voir en production, bien évidemment. Les challenges de cette technologie restent complexes et ne se limitent pas à ces deux points cruciaux, la question des défauts dans les masques est elle aussi importante même si là aussi TSMC et Intel ont visiblement noté quelques progrès. Vous pouvez retrouver plus de détails sur ces points dans l'article de SemiWiki .

Arctic Freezer i11 CO et Alpine 11 Passive

Arctic Cooling annonce deux nouveautés dans sa gamme de ventirad. La première est une déclinaison de son ventirad d'entrée de gamme Arctic Freezer i11. Pour rappel, l'i11 est un ventirad type tour dédié aux sockets Intel (LGA-115X, LGA-2011) qui utilise trois caloducs en contact direct.

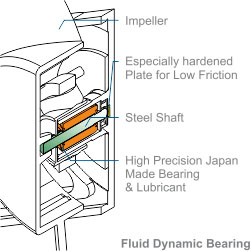

La nouvelle version baptisé Arctic Freezer i11 CO (Continuous Operation) remplace son ventilateur 92mm PWM habituel (système de rotation pallier/douille) par un modèle avec un double roulement à billes, annoncé pour une longévité cinq fois supérieure. Pour le reste les caractéristiques des ventilateurs sont identiques, il est annoncé avec une plage de fonctionnement de 500 à 2000 tours/minute avec un débit de 74 CFM. Même le niveau de bruit annoncé est identique, ce qui parait particulièrement surprenant !

La version CO est annoncée comme "optimisée" pour un fonctionnement continu 24/7. Les deux références apparaissent au même prix sur le site du constructeur , 40 euros, même si en pratique le Freezer i11 se trouve aujourd'hui sous la barre des 25 euros chez les revendeurs.

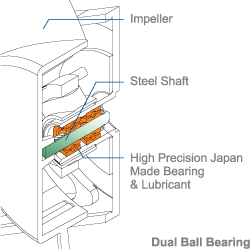

L'autre nouveauté est plus originale puisqu'il s'agit d'un radiateur passif pour processeurs Intel. L'Alpine 11 est annoncé comme compatible avec les sockets LGA115X, il mesure 95mm en longueur/largeur pour 69mm de hauteur, le tout pour un poids de 527 grammes.

Arctic l'annonce comme capable de refroidir jusqu'à 47 watts, même si le constructeur précise que des processeurs au TDP supérieur à 35 watts pourraient limiter leur fréquence en charge.

Côté prix, le modèle est annoncé sur le site du constructeur pour 13 euros, il s'agit du second modèle passif lancé par Arctic ces derniers temps, un modèle passif dédié à la plateforme AM1, l'Alipine M1 , avait été introduit en fin d'année dernière.

La disponibilité effective chez les revendeurs pour ces nouveaux modèles est encore inconnue.

Accélération SHA pour Cannonlake

Quelques petites informations et confirmations sont apparues ce week-end à propos de Cannonlake, la future architecture processeur d'Intel prévue pour la seconde moitié de 2017, et qui sera la première du constructeur à être produite dans un procédé de fabrication 10nm.

Quelques petites informations et confirmations sont apparues ce week-end à propos de Cannonlake, la future architecture processeur d'Intel prévue pour la seconde moitié de 2017, et qui sera la première du constructeur à être produite dans un procédé de fabrication 10nm.

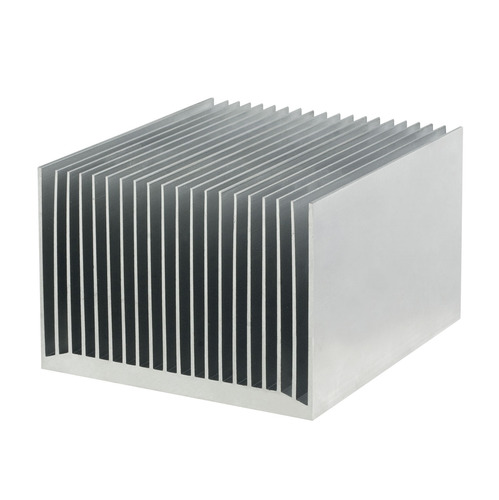

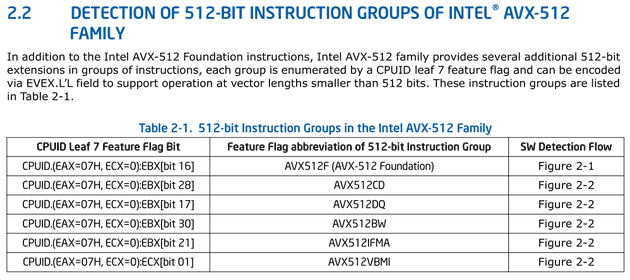

C'est par la publication d'un patch pour Clang, le compilateur C/C++/Obj-C de LLVM que l'on aura obtenu d'abord quelques confirmations sur le support d'AVX-512. Le patch en question que vous pouvez retrouver ici concerne l'énumération des fonctionnalités des familles de processeur. L'intérêt de ce code est de permettre aux développeurs, indépendamment de la machine qu'ils utilisent, de compiler des versions optimisées de leurs programmes pour une architecture donnée (par exemple, optimisée pour Skylake en ajoutant -march=skylake, plus de détails sur le sujet dans cet article).

Le patch, en développement depuis début février , indique le support spécifique de certains jeux d'instructions en fonction des familles. On retrouve ainsi les deux déclinaisons de Skylake, la version "client" (celle disponible pour les PC portables et de bureau) et la version "serveur" pour les Xeon. Cette dernière se différencie pour rappel par son support d'une partie du jeu d'instruction AVX-512.

Pour ce patch, Intel ne spécifie qu'une seule version de Cannonlake et l'on retrouve, comme promis, le support des instructions AVX-512. De manière plus précise, en plus des instructions déjà supportées par la version Xeon de Skylake, deux autres extensions sont présentes, avx512ifma et avx512vbmi (une information que nous avions notée l'année dernière). L'extension avx512ifma concerne les instructions dites fused multiply add (par exemple A x B + C), appliquées cette fois ci à des nombres entiers (sur une précision de 52 bits). avx512vbmi rajoute des instructions de manipulation/permutations vectorielles d'octets (Vector Byte Manipulation Instructions).

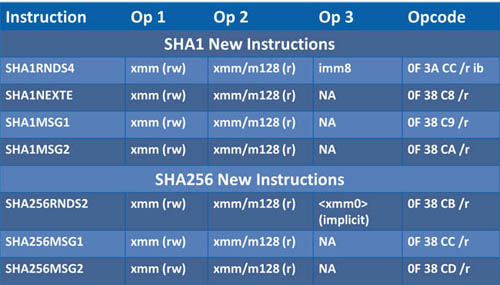

L'autre information est la confirmation de l'arrivée d'instructions dédiées aux calculs de hash cryptographiques. Les instructions sha font, sans trop de doute, référence à ces instructions présentées en 2013 par Intel , capables d'accélérer le calcul de hash aux formats SHA-1 et SHA-256 . Elles devraient être donc introduites pour la première fois sur Cannonlake.

On notera également dans le patch la mention d'une autre extension, umip pour laquelle nous n'avons pas encore trouvé de référence dans la documentation d'Intel !