Les contenus liés aux tags Intel et Samsung

Afficher sous forme de : Titre | Flux3D NAND 48 couches chez Toshiba

Intel précise son process 14nm

46% de parts de marché pour TSMC

Dossier: Comparatif SSD : 28 SSD de 480 à 512 Go

AMD 4è fabricant de microprocesseurs

V-NAND Gen4 et Z-NAND pour Samsung

Samsung est lui aussi bien évidemment présent au Flash Memory Summit et en profite pour annoncer sa quatrième génération de mémoire NAND 3D (connue sous le nom marketing V-NAND). L'année dernière, Samsung annonçait sa troisième génération qui faisait passer à 48 couches pour obtenir jusque 32 Go par die.

Cette année, Samsung annonce 64 couches pour une densité maximale de 512 Gbit en TLC, soit 64 Go par die. De quoi permettre d'atteindre pas moins de 1 To par package (en superposant 16 dies). Samsung proposera donc un SSD BGA de 1 To avec 1500 Mo/s en lecture et 900 Mo/s en écriture.

Le PM1643 de 32 To, photo The SSD Review

Le SSD PM1633a de 16 To (qui avait été annoncé lors du Flash Memory Summit 2015 il y a un an, mais seulement commercialisé ces dernières semaines sera remplacé à terme par un modèle 32 To, le PM1643.

Une version 32 To en NVMe est également annoncée sous la référence PM1735 et un modèle M.2 de 4 To est également au programme en taille standard, et Samsung compte proposer en 2017 un "nouveau" format de M.2 dédié aux serveurs, le M.2 32114 (32mm de large pour 114 de long) avec une capacité pouvant atteindre 8 To, ce qui permettra d'atteindre 256 To de stockage dans un rack 1U.

Bien évidemment, et le lancement ces derniers jours du PM1633a le prouve, les annonces de Samsung se traduiront au fur et a mesure dans les mois à venir, le communiqué de presse du constructeur évoque le quatrième trimestre pour les premières disponibilités de produits basés sur la V-NAND de quatrième génération. Le PM1643 est quand à lui annoncé pour 2017 sans plus de précision.

On notera enfin une dernière annonce très floue de la part de Samsung avec la Z-NAND, un "nouveau type de mémoire" qui partage "la même structure fondamentale que la V-NAND" en utilisant un "design de circuit et un contrôleur unique". Si cela ne nous dit pas grand chose sur la manière dont fonctionne la technologie, il faut y voir la réponse de Samsung à la PRAM 3D XPoint d'Intel/Micron, le constructeur ne s'en cache en reprenant les mêmes arguments, une mémoire qui vient s'intercaler entre la DRAM (volatile, très rapide) et la NAND (non volatile, moins rapide).

La Z-NAND aurait une latence similaire à la PRAM, des performances séquentielles 20% supérieures, et une efficacité énergétique significativement meilleure. Bien entendu ces chiffres sont assez creux sachant que Samsung ne précise pas à quelle PRAM il se compare, mais on voit bien qu'Intel et Micron sont visés par cette annonce. Plus de détails devraient être disponibles d'ici quelques mois, Samsung annonçant une disponibilité en 2017.

L'EUV possiblement pour le 7nm ?

Le site SemiWiki nous rapporte quelques informations sur l'état de la fabrication EUV, en provenance de la conférence SPIE Advanced Lithography qui se tient actuellement à San José.

Lors de la même conférence l'année dernière, les nouvelles étaient pour rappel plutôt bonnes (voir le lien pour un rappel complet sur la fabrication des processeurs et l'importance capitale de l'EUV !) et l'on espérait une introduction en cours de process pour le 10nm, et une introduction complète à 7nm. Malheureusement, on le rappelait en janvier, TSMC avait calmé les ardeurs en indiquant qu'il faudrait attendre le 5nm pour une éventuelle introduction de cette technologie.

SemiWiki confirme certains chiffres donnés lors de la dernière conférence aux investisseurs de TSMC, à savoir que la machine avait atteint sur une période de quatre semaines une production de 518 wafers/jour, un niveau encore largement insuffisant. Intel a partagé également quelques chiffres, un peu inférieurs à ceux de TSMC, à savoir entre 2000 et 3000 wafers par semaine (285-428 par jour).

On notera quand même que le taux de disponibilité des scanners de la société ASML a augmenté, passant de 55 à 70% chez TSMC (Intel rapportant une disponibilité identique) ! On notera que s'il est question d'une introduction en début de node à 5nm, TSMC laisse la porte ouverte pour le 7nm si jamais des progrès étaient effectués. Intel de son côté n'a pas donné d'information. Samsung envisagerait l'introduction à 7nm selon les présentations, sans plus de précisions.

Si la question de la disponibilité est importante, celle de la puissance de la source lumineuse l'est encore plus. Après avoir été limité à 40 watts l'année dernière, les machines actuellement en évaluation chez TSMC disposent désormais de sources 80 watts. C'est mieux, mais cela reste loin des 250 watts promis par ASML pour fin 2015. Les dernières prédictions sont désormais de 250 watts en 2016-2017, et au delà en 2018-2019, des plages particulièrement larges.

Atteindre les 250 watts de puissance permettrait d'augmenter significativement la cadence de production, atteignant 170 wafers/heure en théorie. ASML a effectué des démonstrations que TSMC et Intel semblent juger prometteuses de 185 et 200 watts. Reste à les voir en production, bien évidemment. Les challenges de cette technologie restent complexes et ne se limitent pas à ces deux points cruciaux, la question des défauts dans les masques est elle aussi importante même si là aussi TSMC et Intel ont visiblement noté quelques progrès. Vous pouvez retrouver plus de détails sur ces points dans l'article de SemiWiki .

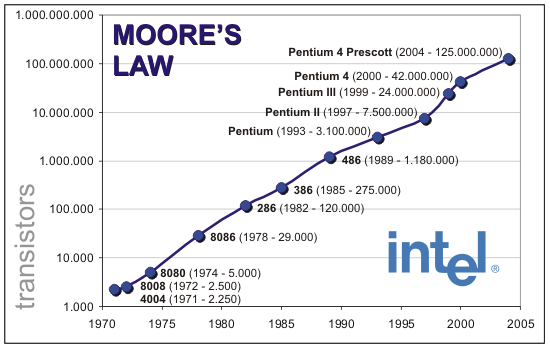

L'ITRS prépare l'après loi de Moore

C'est la section actualité de la très sérieuse revue scientifique Nature qui l'affirme : la loi de Moore est arrivée à son terme. Énoncée en 1965 par Gordon Moore, l'un des cofondateurs d'Intel, il s'agit d'une observation par laquelle la quantité de transistors dans les circuits intégrés doublait à peu près tous les ans. Une observation transformée en loi pour prédire que cette cadence pouvait être extrapolée pour les années à venir.

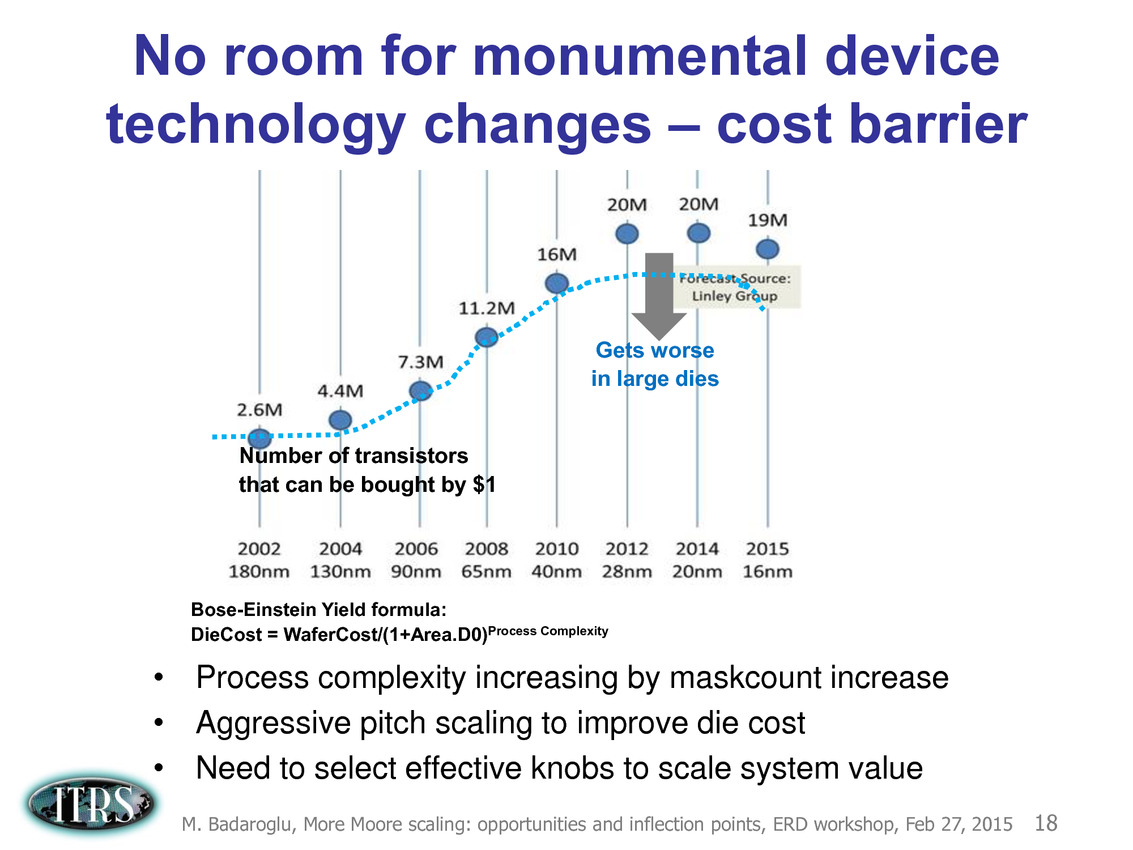

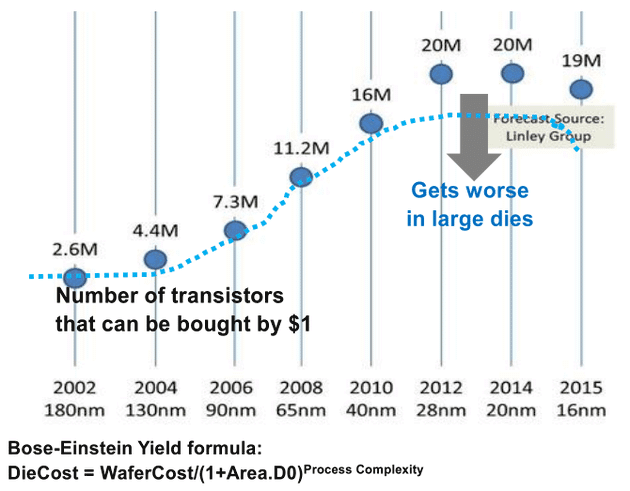

En 1975, la loi avait été révisée pour prendre la forme que l'on connaît actuellement, à savoir un doublement des transistors tous les deux ans. L'importance de la loi de Moore allait cependant au-delà de la simple prédiction puisqu'elle prenait en compte les coûts de fabrication : l'observation se fait sur les puces ayant le coût par transistor le plus faible (tentant donc de prendre en compte les questions de yields et de défauts en fonction de la taille des puces).

Plus qu'une prédiction, la loi de Moore a servie, particulièrement chez Intel, de guide au fil des années, prédisant à l'avance les budgets en nombre de transistors alloués aux ingénieurs, et poussant vers l'avant la nécessité d'investir dans de nouveaux process de fabrications, la fameuse stratégie du Tick-Tock poussée d'abord en interne par Pat Gelsinger au début des années 2000 avant d'être utilisée publiquement pour décrire les générations à venir.

De manière intéressante, au-delà d'Intel, c'est toute l'industrie du semi-conducteur qui s'est mise d'accord autour de la loi de Moore, à savoir non seulement les fondeurs, mais aussi et surtout les fournisseurs d'outils. Le besoin de coordination entre tous les acteurs aura conduit à l'élaboration d'une roadmap, d'abord appelée National Technology Roadmap for Semiconductors dès 1993, avant d'être renommée sous sa forme actuelle, l'International Technology Roadmap for Semiconductors (ITRS).

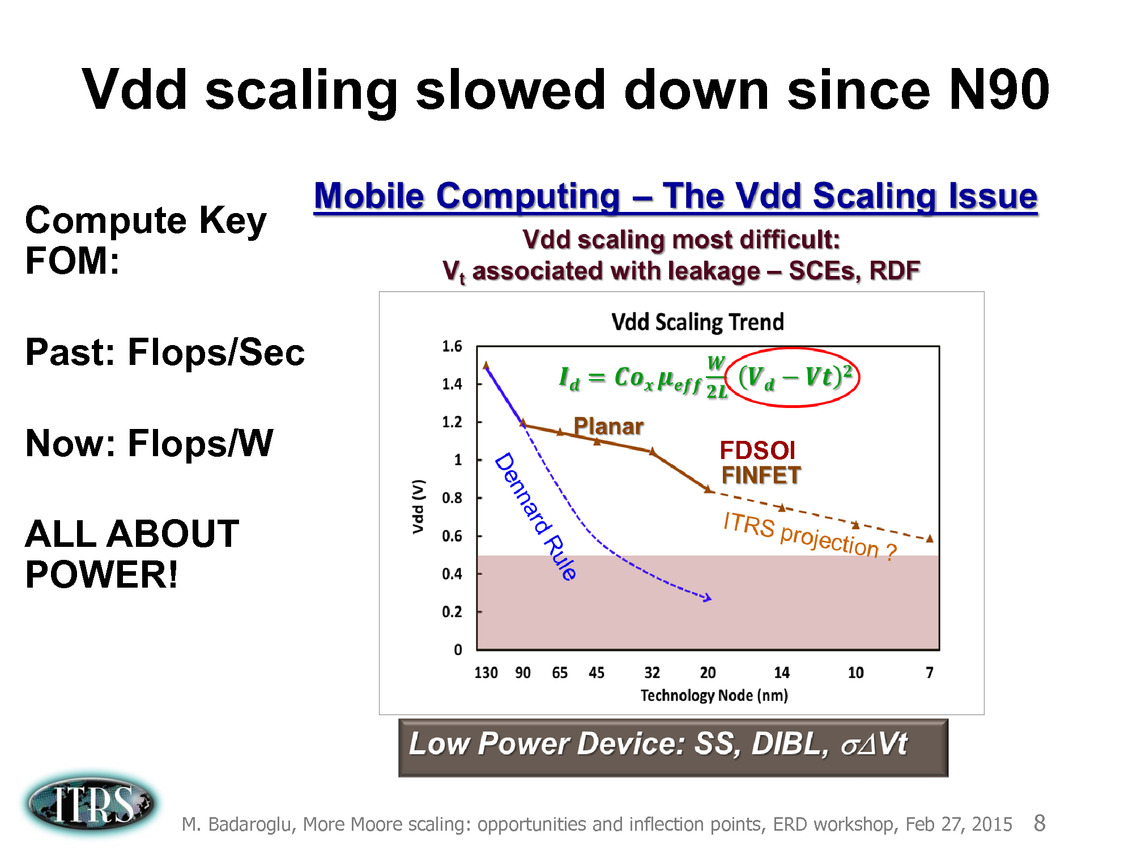

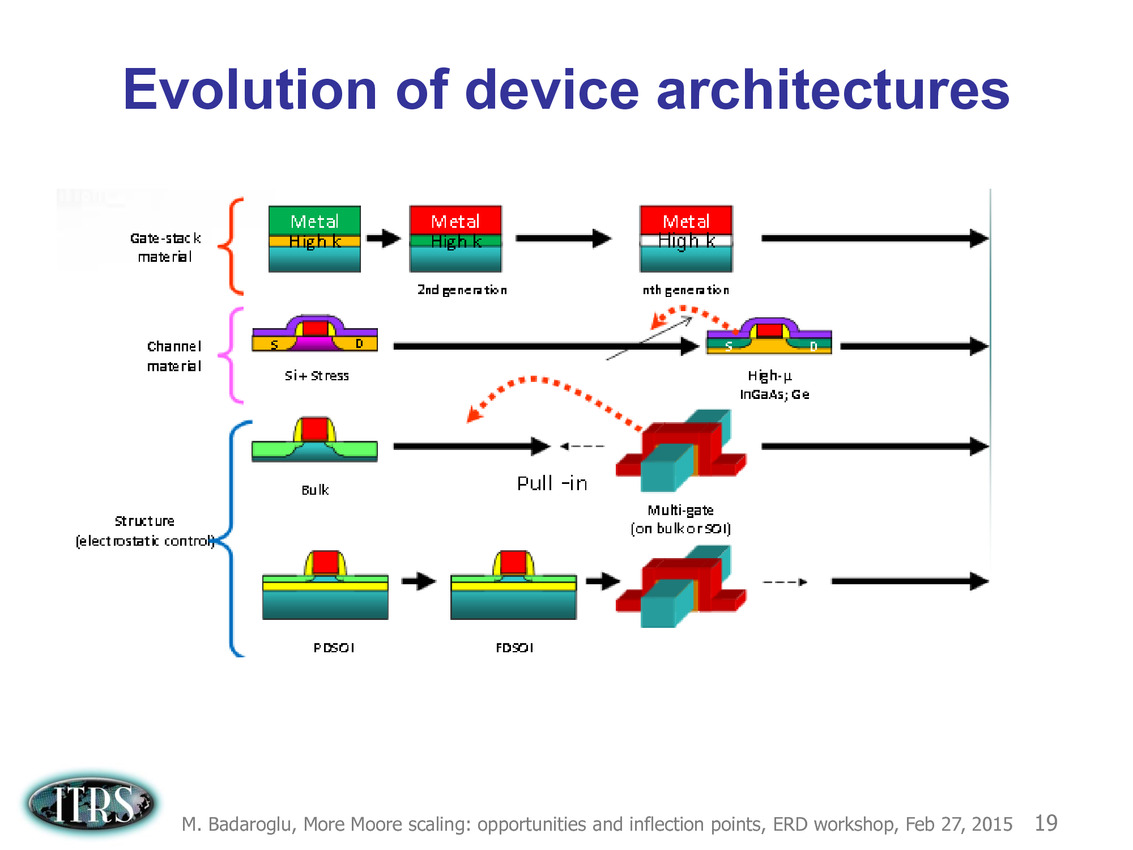

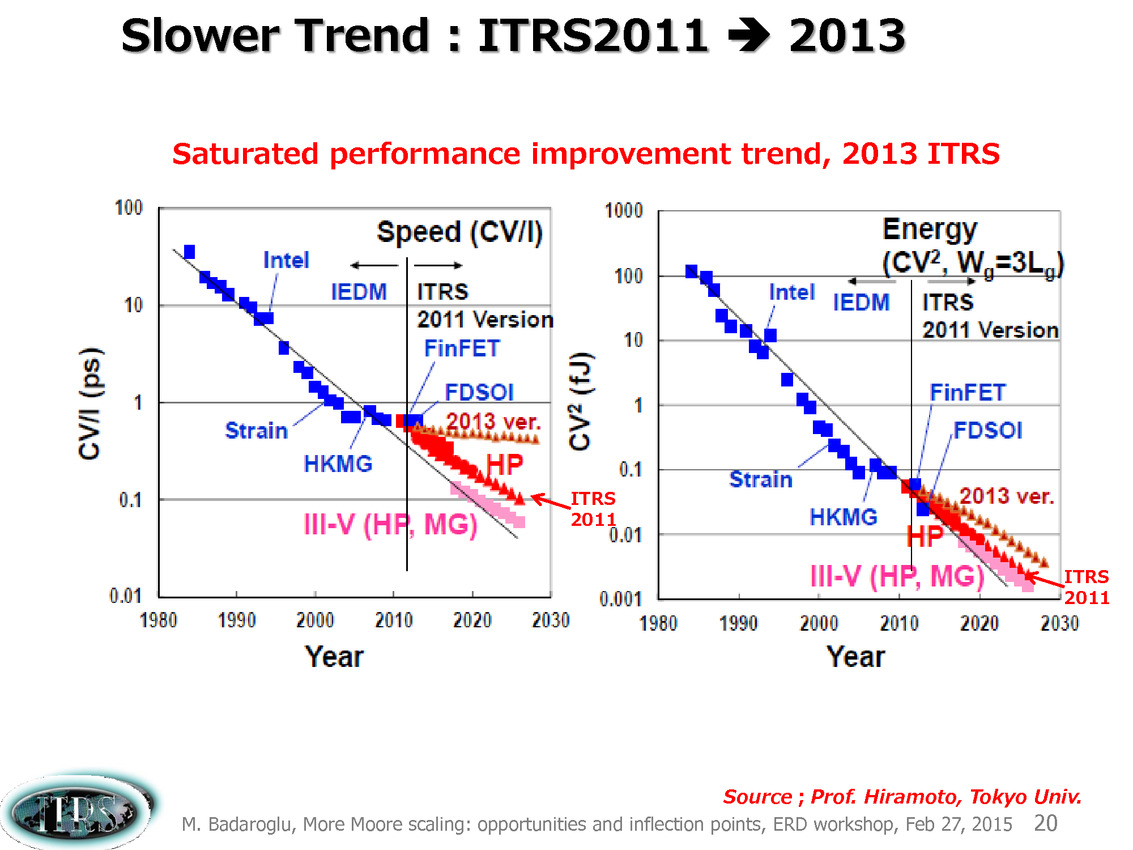

Le rôle joué par cette roadmap, dont la dernière version a été publiée en 2013 aura été particulièrement important ces dernières années où, passé le 90nm, les challenges techniques ont contraint à des changements d'approches importants. L'augmentation des performances par la fréquence, méthode classique aura atteint un plateau à cause de l'augmentation de la consommation, poussant dans le commerce les stratégies de multiplication des coeurs que l'on connaît. Le rôle de la roadmap, au-delà de la concertation, est de s'assurer de trouver des pistes pour continuer la cadence de réduction des coûts/augmentation des transistors de la loi de Moore.

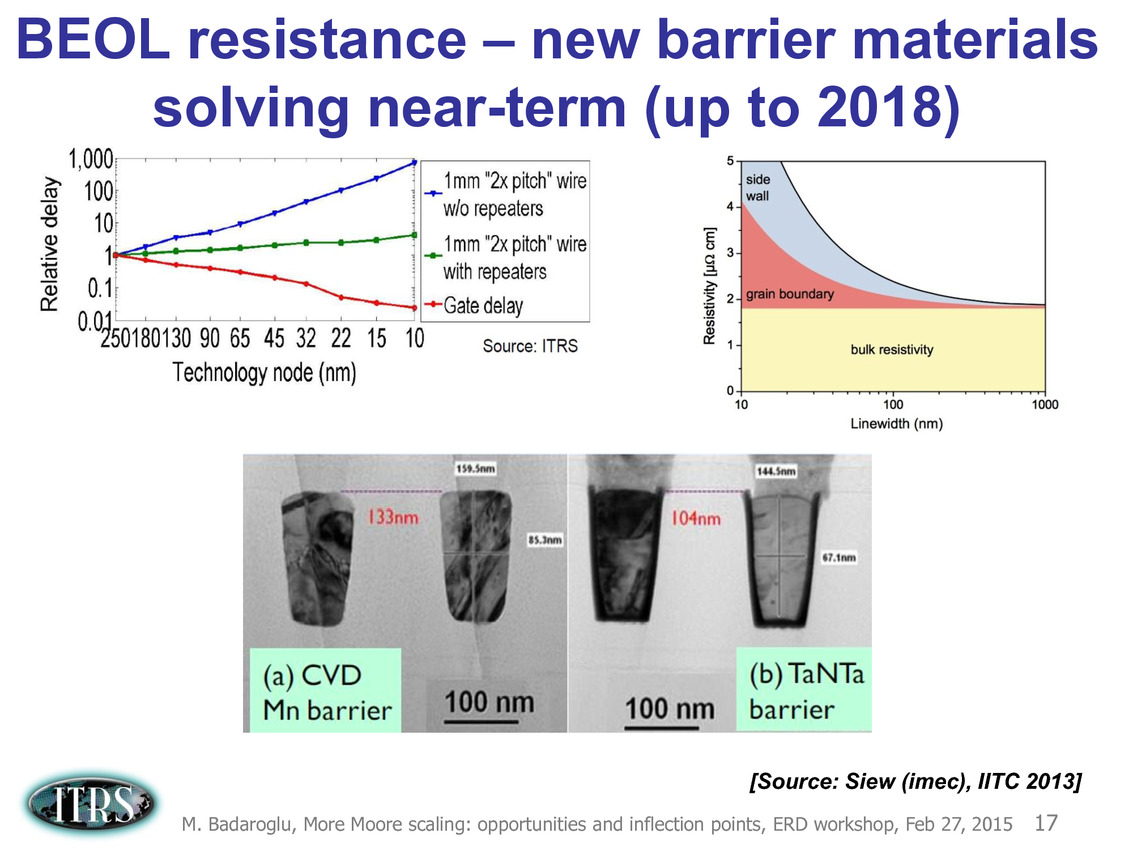

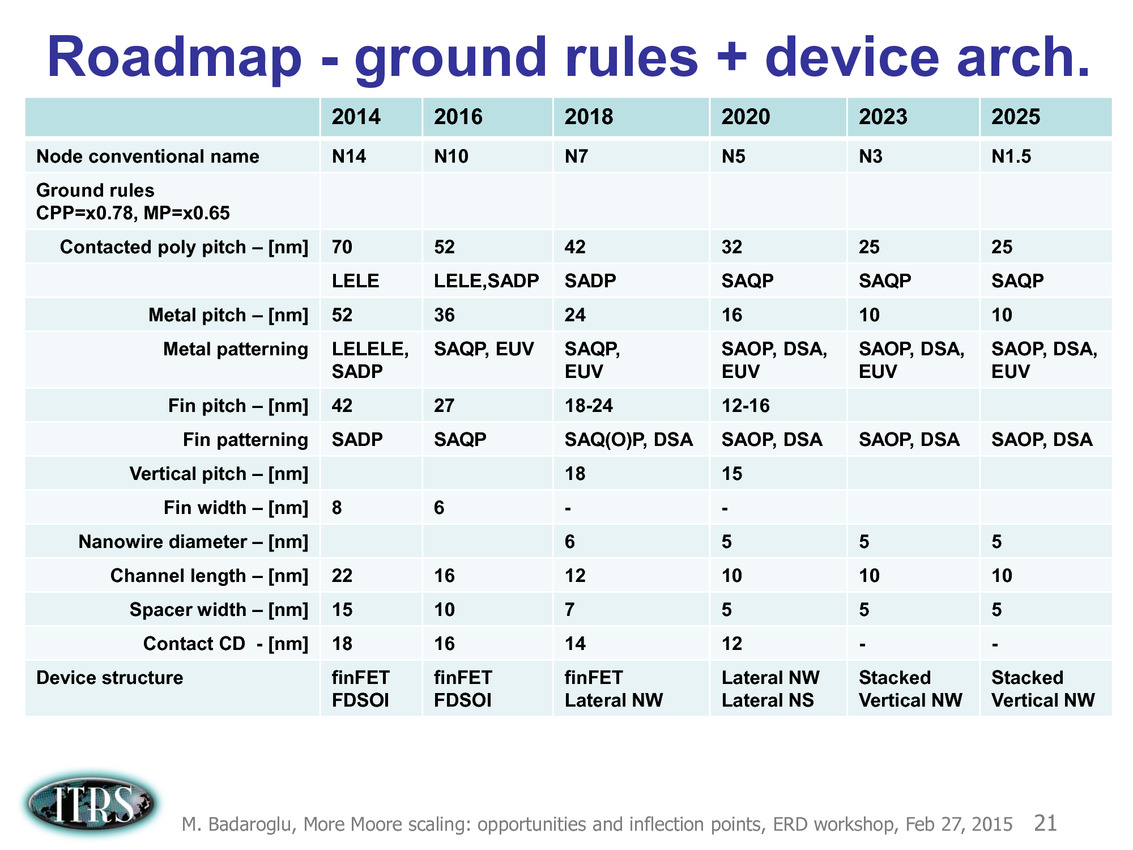

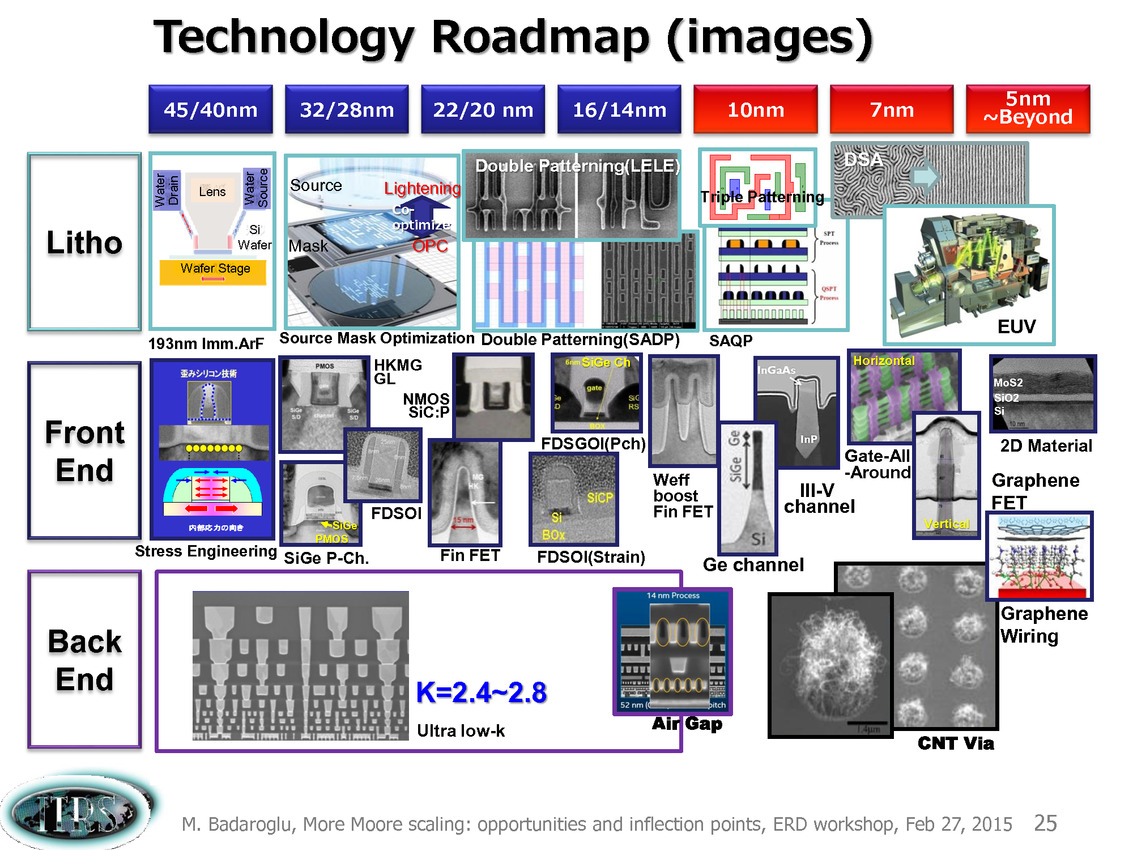

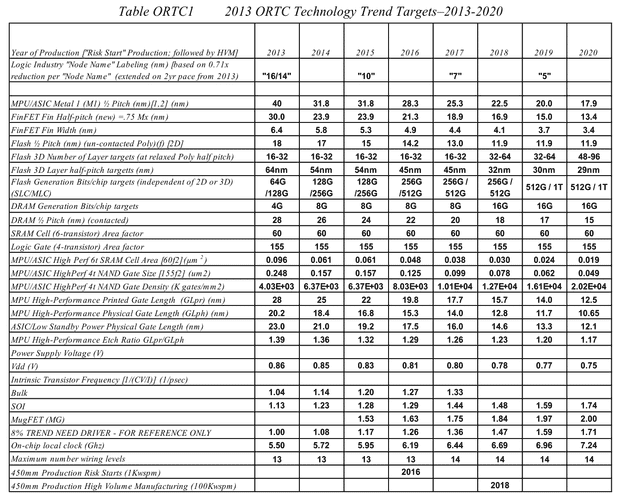

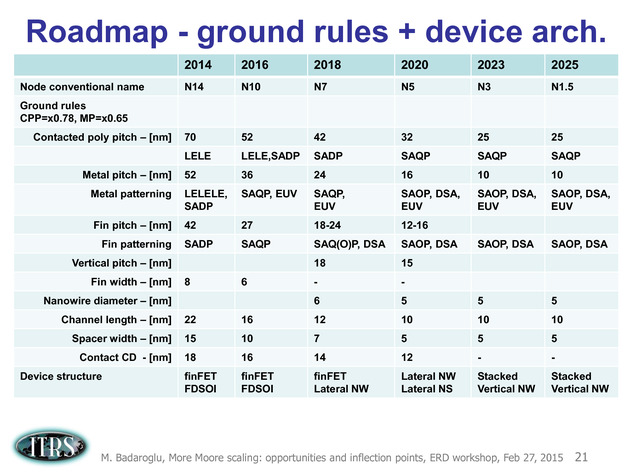

La dernière roadmap ci-dessus donnait des grandes lignes sur la manière de mettre à l'échelle les différents composants des transistors. Après les difficultés autour du 90nm, l'industrie est passé progressivement de la règle dite de la mise à l'échelle géométrique (on réduit tout dans des proportions identiques, le nom du node indiquant en général la taille de la porte) à celle de la mise à échelle par équivalence (equivalent scaling).

Etant donné que différentes parties composant les puces posent des problèmes différents, des règles d'équivalences ont été mises au point pour permettre de continuer a atteindre les buts de réduction des coûts/augmentation de densité imposé par la loi de Moore (on peut voir sur le tableau la couche d'interconnexion M1 et l'écart minimal entre deux transistors FinFET, en passant par des estimations des tailles de blocs fondamentaux comme la SRAM).

Pour 2016, la roadmap annonçait par exemple de la SRAM 6 transistors (6T) haute performance en 10nm autour de 0.048 µm2, ce qui n'est pas très éloigné de ce que présentait Samsung il y a une dizaine de jours de cela. En pratique cependant, on notera qu'on est globalement assez en retard sur la roadmap qui prévoyait des débuts de production à petite échelle en 10nm en 2015 (Risk Start dans la roadmap, suivi de HVM, fabrication en volume). Chez TSMC par exemple, la production risque est prévue pour la fin 2016 avec une production en volume pour 2017. Intel prévoit ses puces en volume pour 2017 également.

Évidemment depuis 2013 les choses se sont un peu plus compliquées et l'absence de roadmap en provenance de l'ITRS n'a pas forcément aidé. En pratique, la réduction des coûts s'est arrêtée, avec même un retour en arrière à 16nm signant de facto la fin de la loi de Moore, comme on peut le voir sur cette estimation ci-dessus tirée d'une présentation de l'ITRS en février 2015.

L'absence de nouvelle roadmap en provenance de l'ITRS aura même donné lieu à des divergences d'interprétations fortes, Intel titillant ses concurrents sur la question de la densité théorique. TSMC et Samsung ont fait pour rappel le choix de conserver un BEOL (Back End of Line, la partie basse d'une puce qui sert à l'interconnexion des transistors) commun entre le 20 et le 16nm pour accélérer la cadence de mise en production. En pratique chez TSMC, malgré le BEOL commun, le half pitch M1 reste tout de même dans les clous à 32nm (entre 40 et 31.8 sur la roadmap).

La densité pratique reste de toute manière très différente de ce que peuvent proposer des formules grossières comme celle utilisée par Intel (qui multipliait le pitch M1 par le pitch entre deux portes), qui pour exploiter les FinFET aura fait le choix d'utiliser pour certains de ses transistors critiques des structures plus larges composées de plusieurs fins (dans des proportions non négligeables même si la proportion exacte est rarement évoquée de manière précise par Intel).

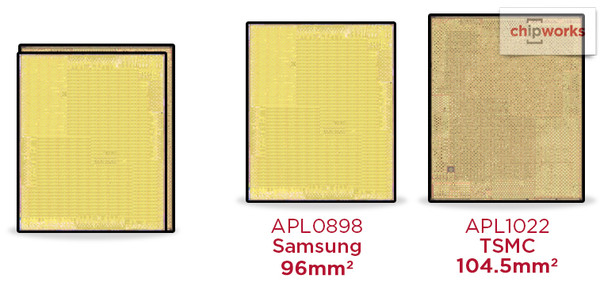

Cumulé a de multiples autres détails (différents types de blocs sont présents avec des densités différentes, de la SRAM aux blocs plus ou moins critiques) il est impossible de tirer grand-chose de la théorie. L'écart entre un Core M Broadwell 14nm fabriqué par Intel (82mm2 pour 1.3 milliards de transistors) et un A8 fabriqué par TSMC en 20nm (89 mm2 pour 2 milliards de transistors) montre qu'il est difficile de comparer quoique ce soit à moins de prendre deux puces strictement identiques. Cela aura été possible pour l'A9 d'Apple, dont la superficie atteint 96mm2 chez Samsung contre 104.5mm2 chez TSMC.

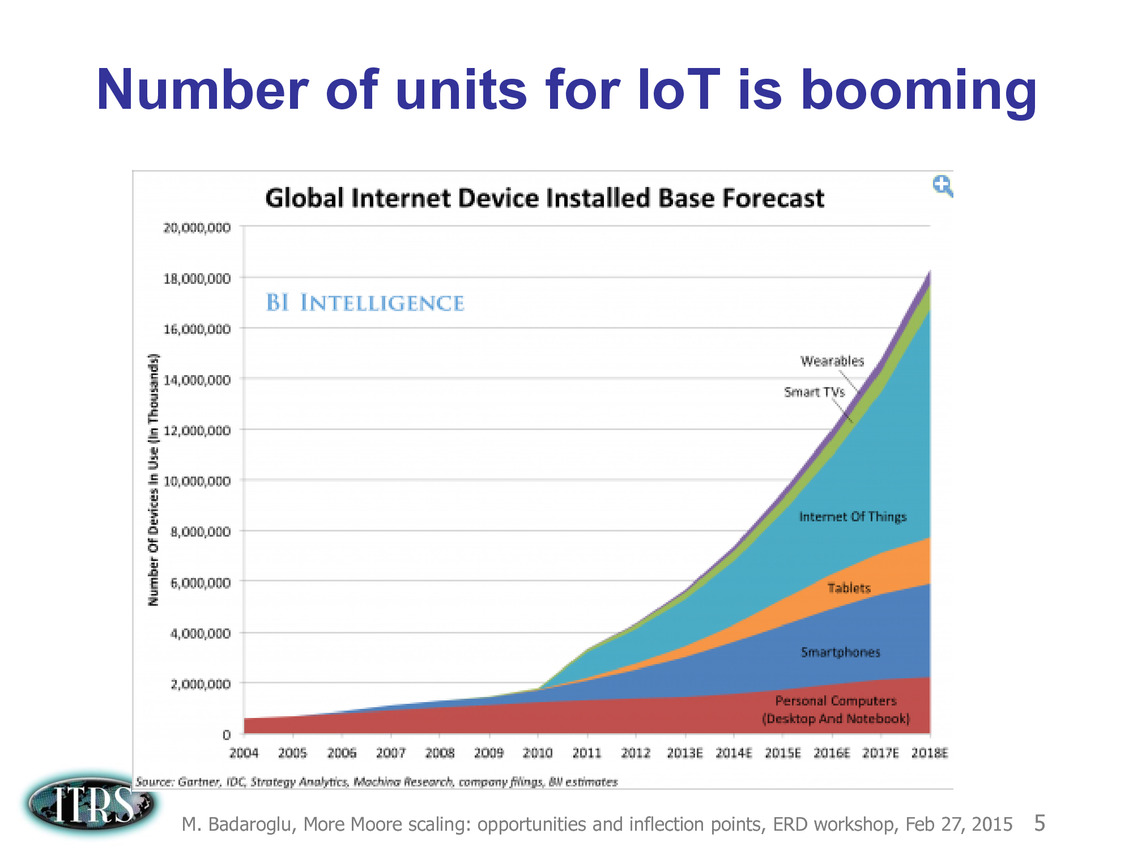

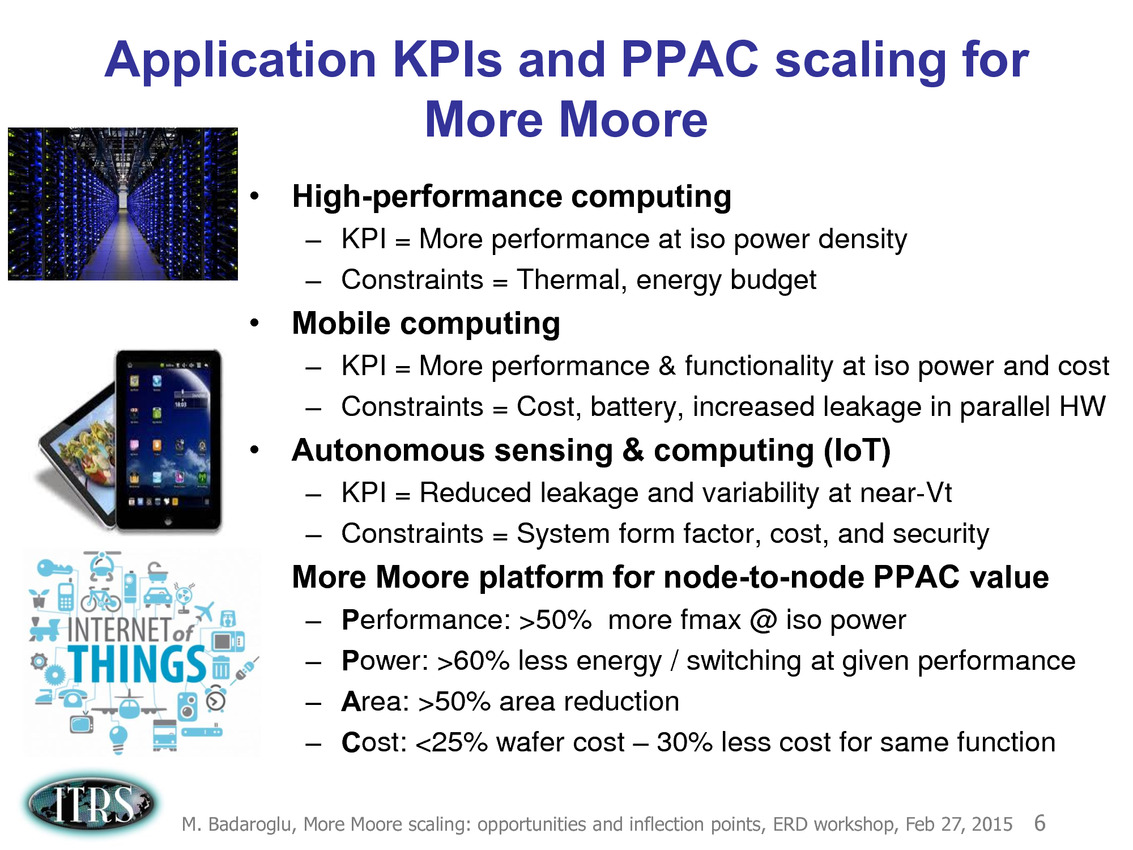

Le mois prochain, l'ITRS devrait donc enfin communiquer une nouvelle roadmap qui d'après Nature tirera définitivement un trait sur la question de la loi de Moore comme moteur d'évolution unique. D'après Nature, la prochaine roadmap se concentrera sur les applications pratiques, allant du smartphones aux puces serveurs et regardera les applications pratiques, que ce soit au niveau circuits d'alimentations, des capteurs nécessaires, ou d'autres blocs de siliciums répondant à des besoins particuliers.

La véritable question est de savoir ce que comportera réellement cette roadmap qui serait rebaptisée d'après Nature International Roadmap for Devices and Systems, abandonnant même le mot transistor !

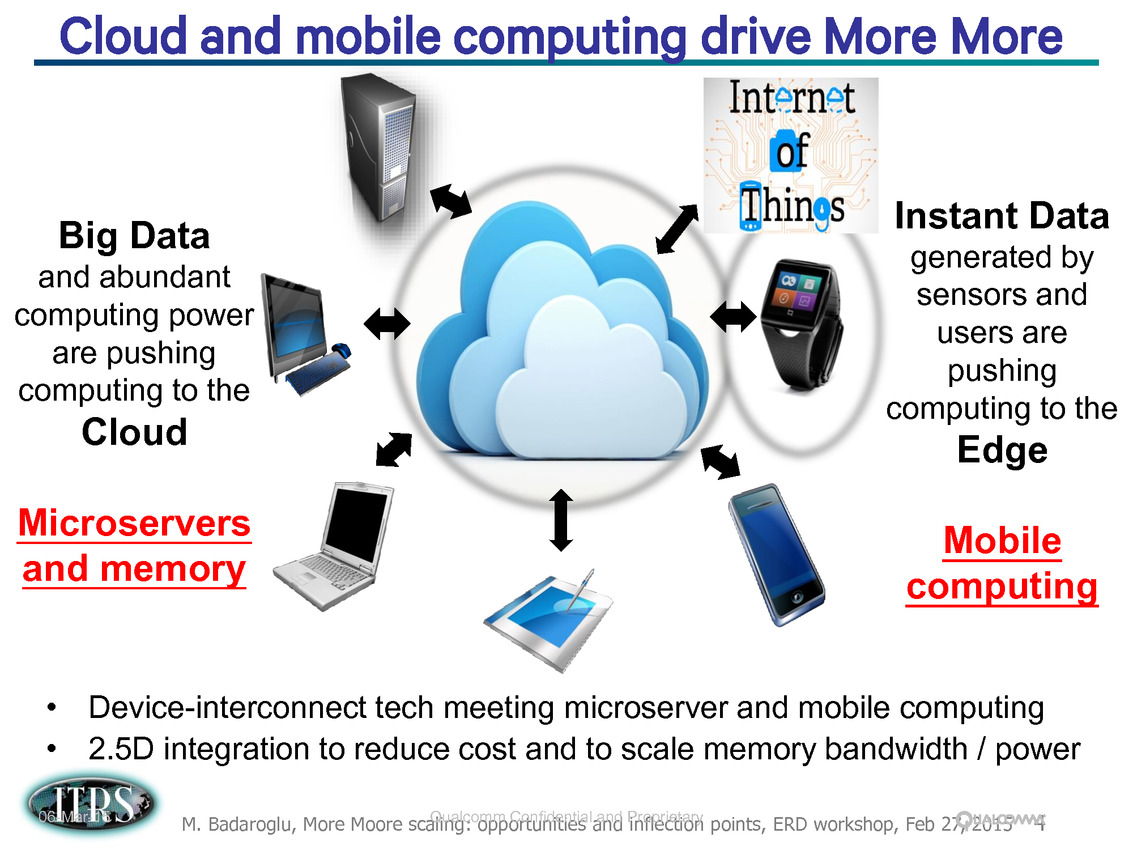

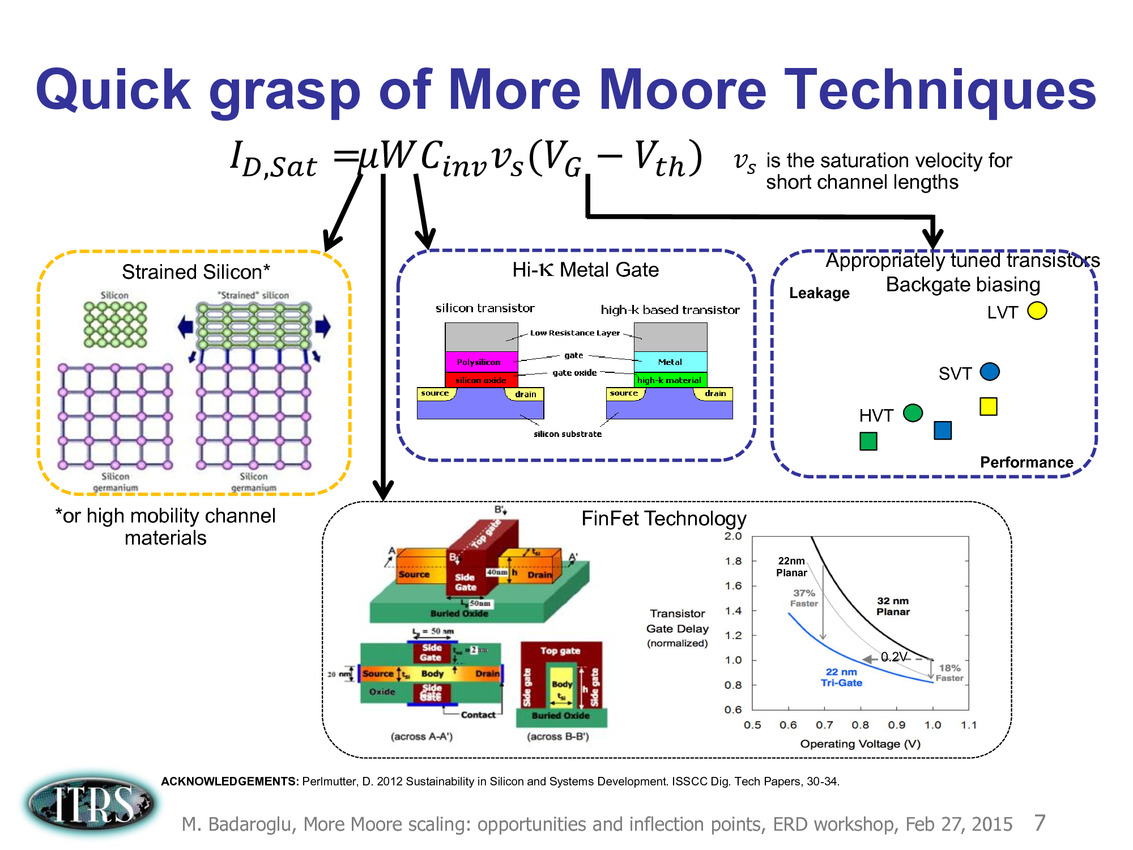

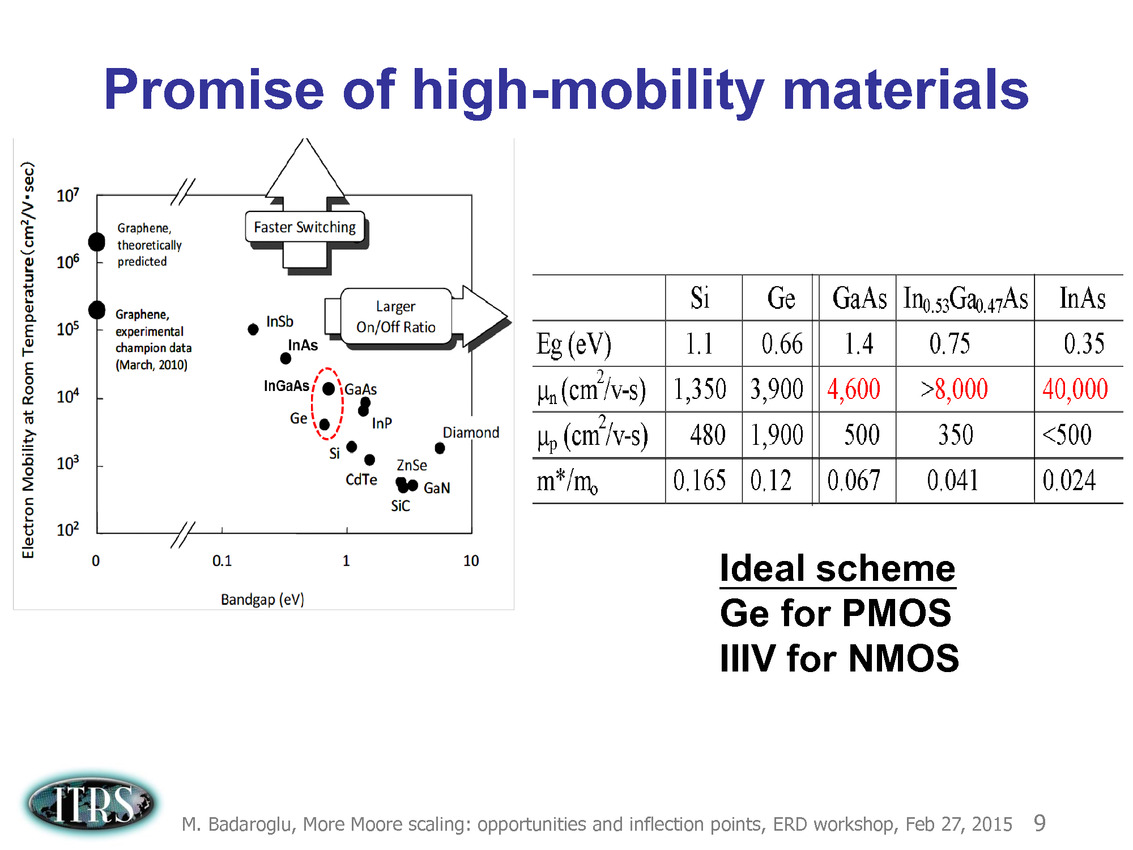

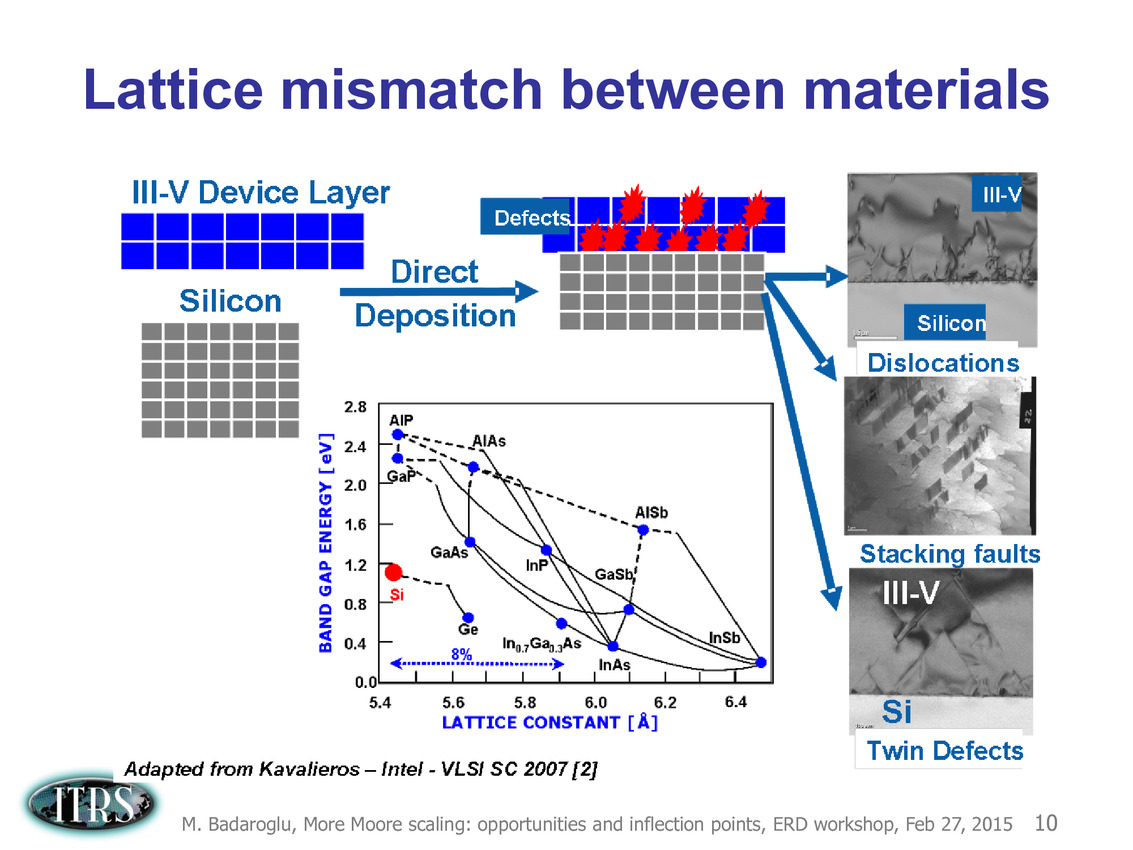

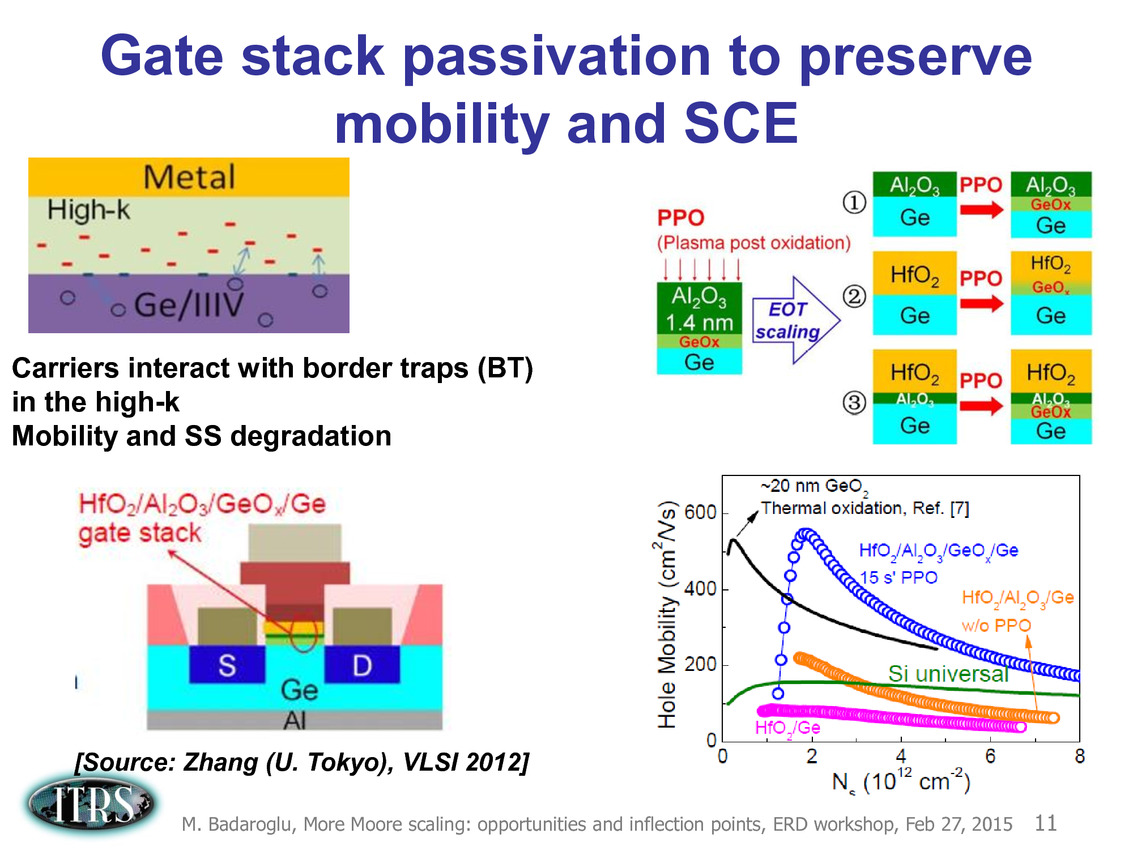

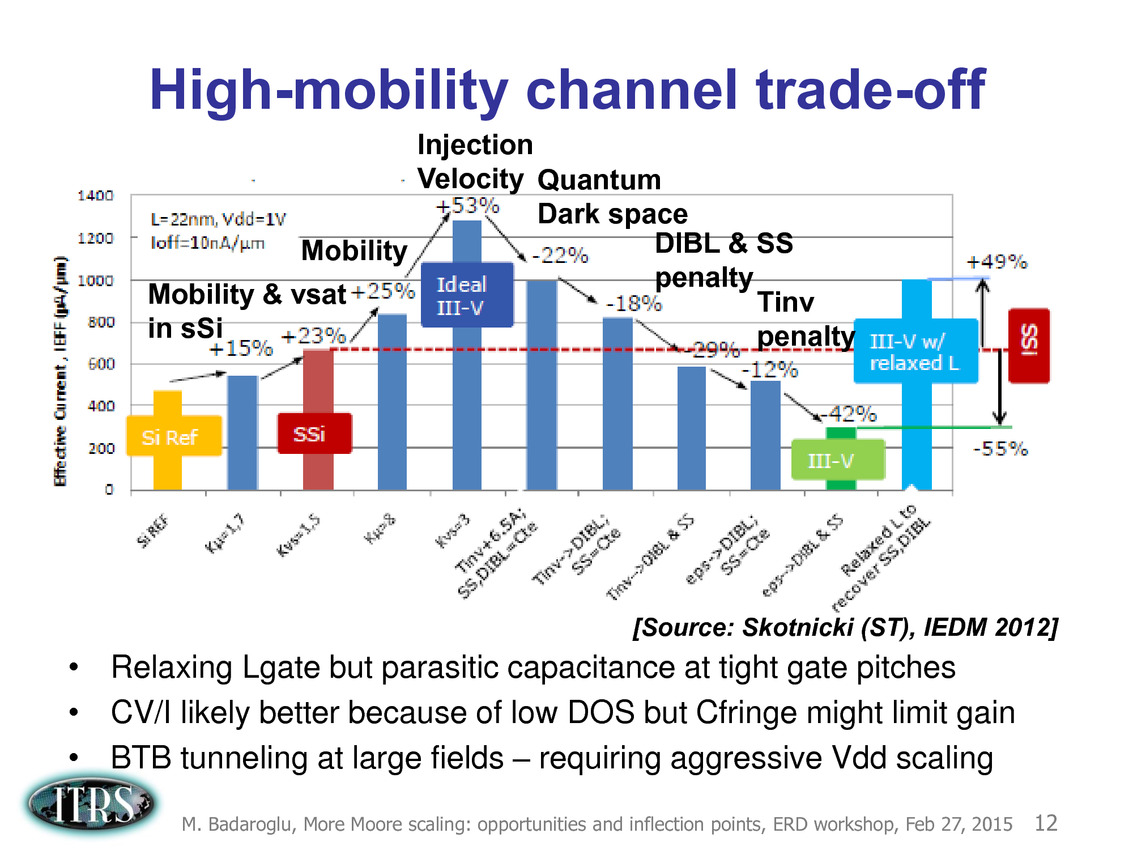

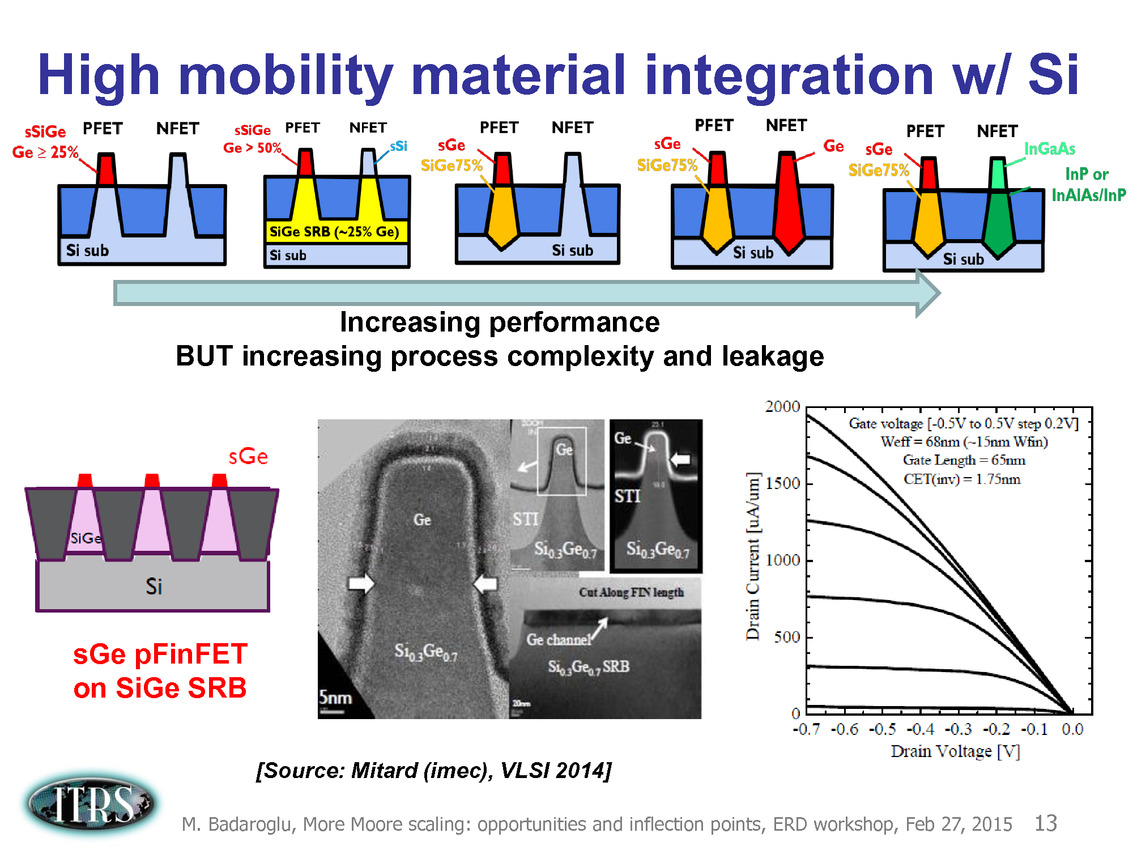

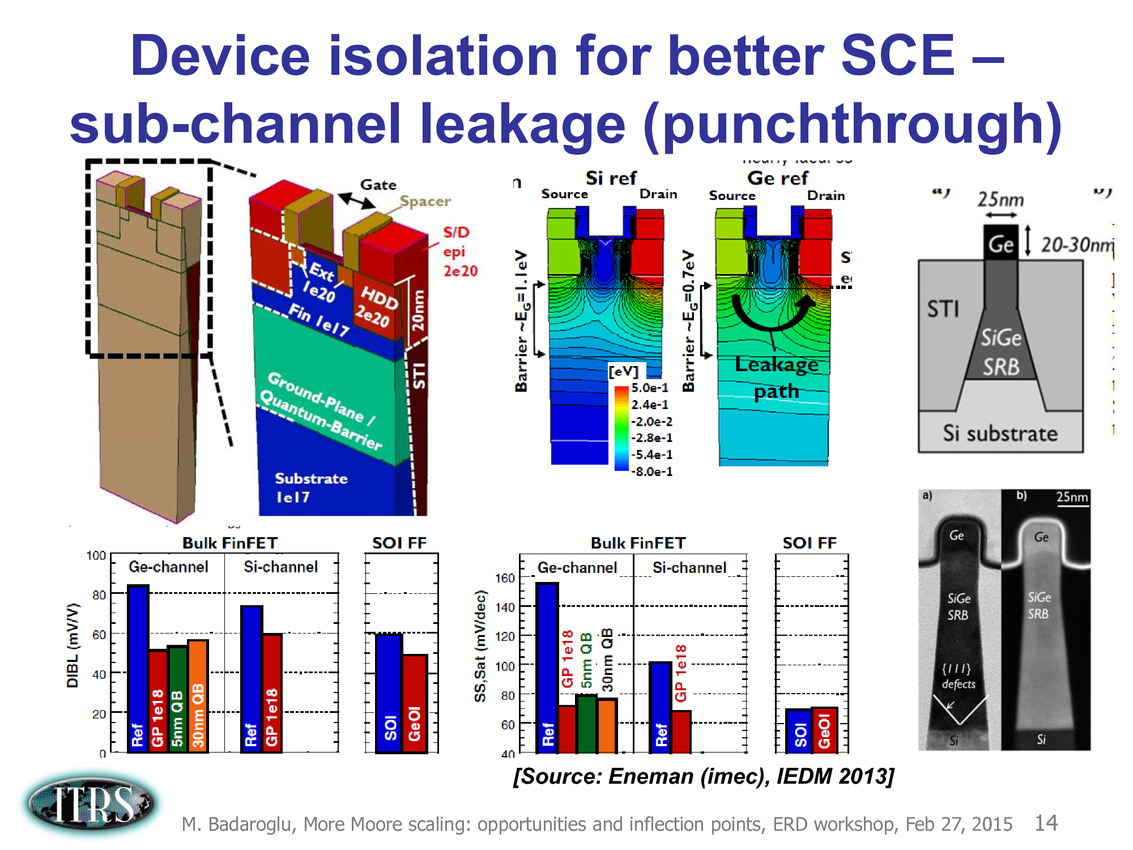

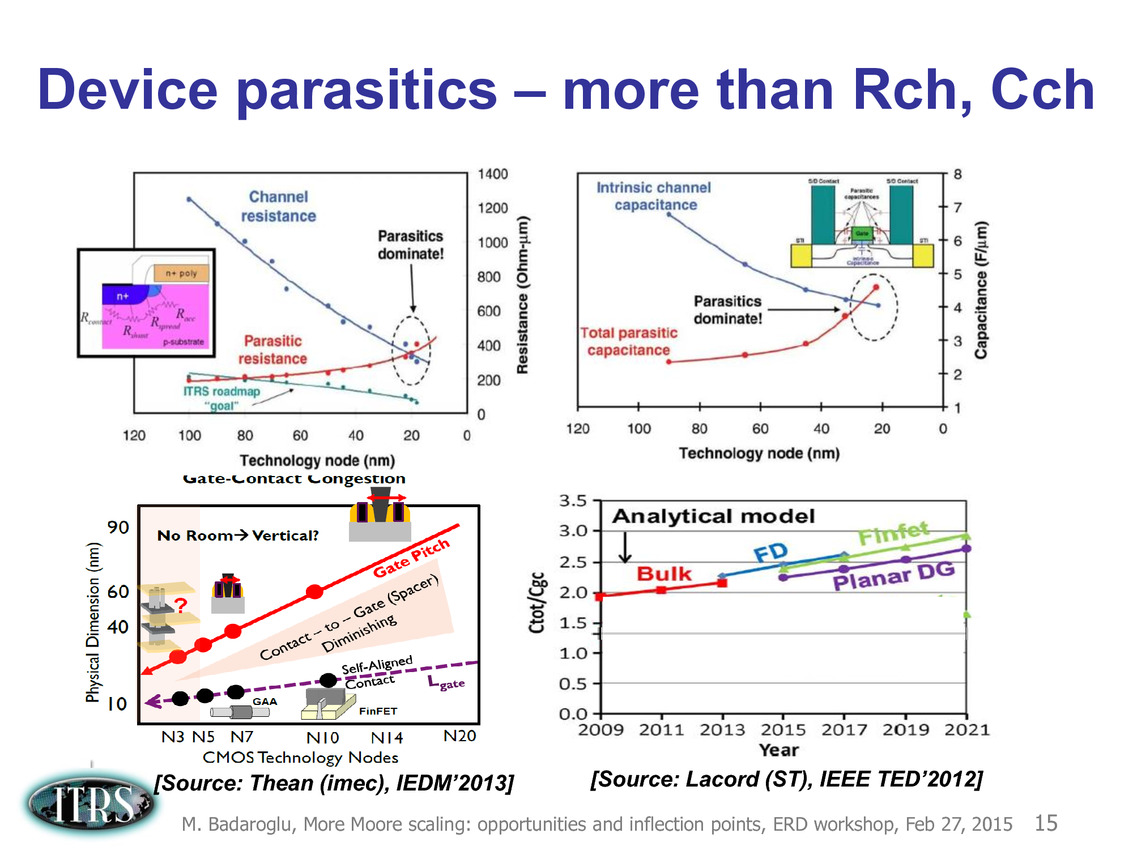

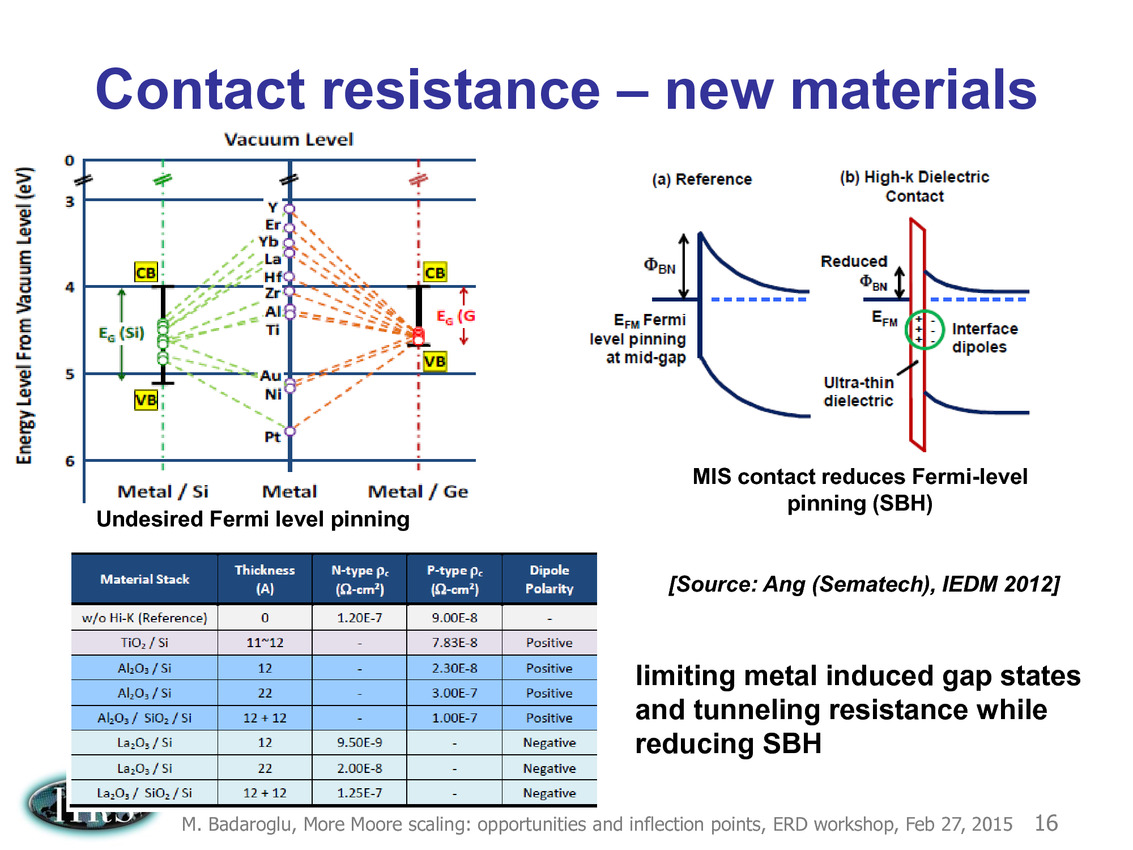

Ce que l'on sait, c'est que la réorganisation de l'ITRS en 2014 s'est faite autour de groupes de travaux, avec notamment un groupe baptisé « More Moore » pour évoquer les pistes techniques pour les prochains nodes, dont vous pouvez retrouver ci-dessous la dernière présentation datant de février 2015.

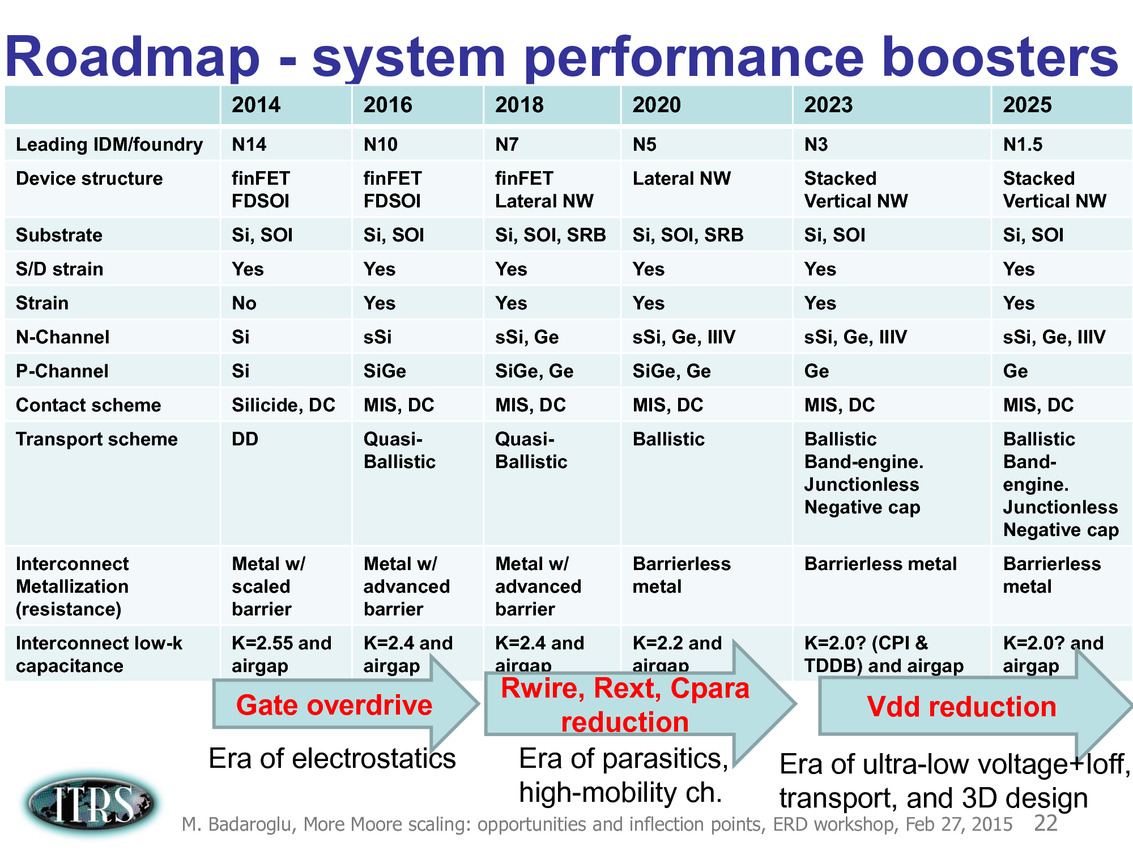

Une présentation intéressante qui évoque de multiples pistes et où l'on trouve un début de roadmap que nous avons remis ci-dessous :

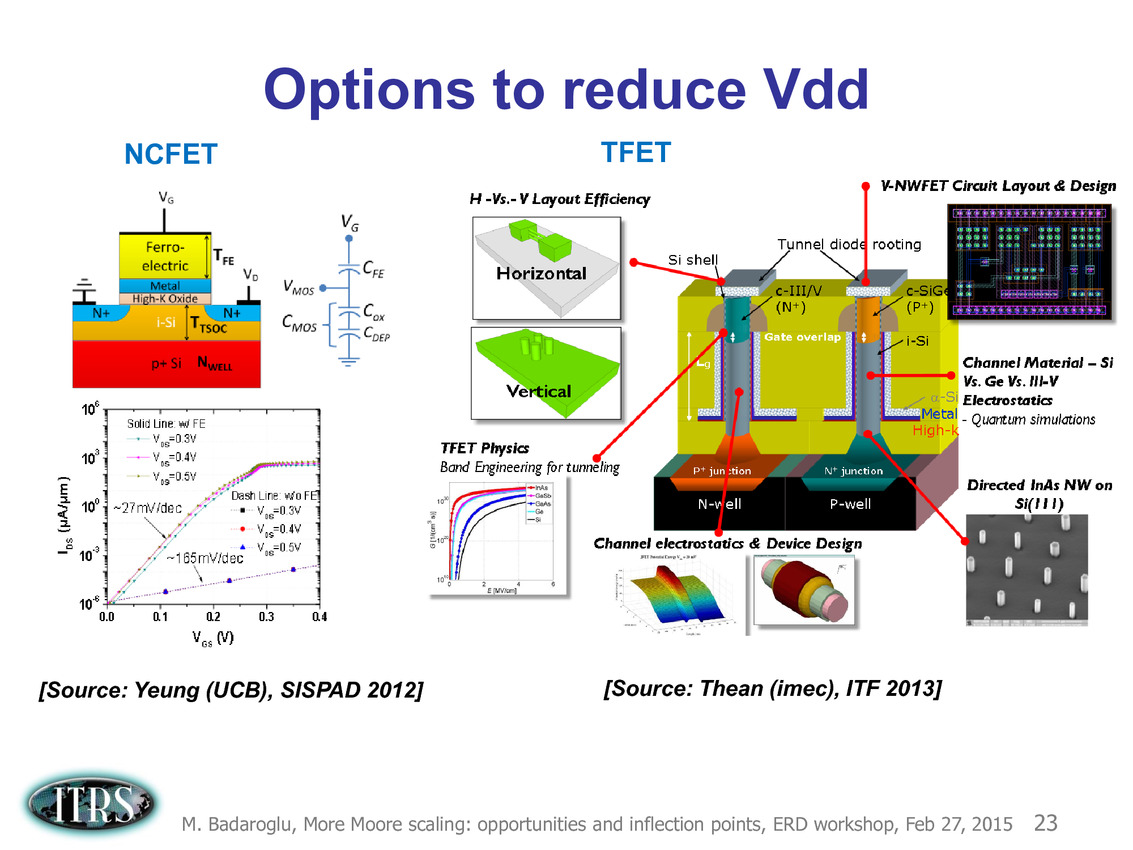

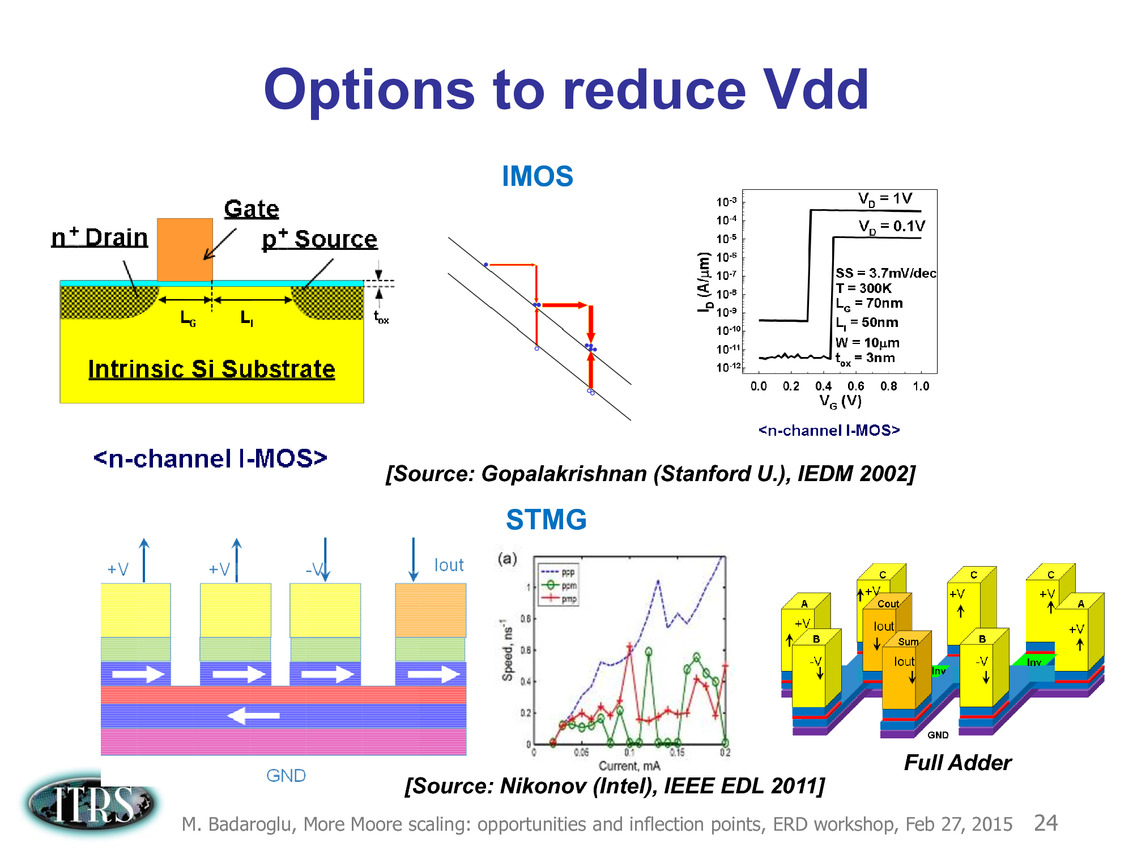

En pratique, après l'ère de la mise à l'échelle géométrique, et l'ère des équivalences, l'ITRS évoque l'ère du "3D Power Scaling" dont les meilleurs représentants sont la NAND 3D ou des technologies comme la mémoire HBM. Des techniques complexes à appliquer aux puces logiques même si la présentation évoque quelques pistes et alternatives.

On attendra donc le mois prochain pour en savoir un peu plus !

ASML confirme les retards sur l'EUV

Après Intel, c'est ASML qui dévoile à son tour ses résultats sur le troisième trimestre. L'occasion pour les dirigeants de la société de revenir sur la question de la lithographie EUV, technologie importante pour la fabrication des semi-conducteurs dans les prochaines années, et sur laquelle ASML a massivement misé.

En début d'année l'optimisme était de mise, évoquant un déploiement de l'EUV en cours de vie du node 10nm, et un déploiement complet à 7nm. ASML s'était même félicité d'avoir vendu 15 machines à Intel. Cependant en juillet TSMC avait refroidit les espoirs, indiquant que l'EUV était exclu à 10nm, et n'arriverait peut être qu'en cours de process 7nm.

Nous notions hier qu'Intel avait repoussé la livraison de certaines machines-outils de deux trimestres et il était facile de lire entre les lignes que l'EUV était en cause. Dans leur présentation aux analystes, ASML a indiqué qu'effectivement la livraison de plusieurs machines avait été repoussée, et que seulement 4 machines EUV seraient livrées en 2016 contre sept annoncées. Le choix de repousser l'insertion a 7 et 5nm fait que les commandes ont été repoussées, modifiées vers de nouvelles machines. Derrière la raison des reports, ASML évoque « l'incertitude de ses clients » sur le timing de leurs nodes à venir, ainsi que sur « leurs priorités à court terme ». On y verrait presque un petit tacle envers Intel dont la priorité principale est effectivement les yields en 14nm qui ont été confirmés comme en dessous des attentes hier par le constructeur.

ASML indique que cinq clients sont concernés par les livraisons de machines EUV dans les années à venir pour un total de 11 machines sur les générations 10 et 7nm. Un chiffre plus bas que le nombre de machines supposément vendues à Intel, il s'agissait cependant d'un contrat à long terme basé sur un certain nombre de critères de performances. Une partie de la commande d'Intel sera donc vraisemblablement repoussée sur le 5nm. Au milieu des questions/réponses, le CEO Peter Wennink a confirmé qu'ASML avait misé sur le fait que le 10nm serait un node EUV, ce qui ne sera pas le cas et décale de 6 à 12 mois les demandes de ses clients. Etant donné que l'écart entre deux nodes est plus proche de 24 mois en moyenne, on doutera un peu de cette assertion. En pratique Peter Wennink à confirmé que le déploiement de l'EUV se ferait à partir de 2018/2019 avec des livraisons pour les machines de production courant 2017.

En ce qui concerne les avancées sur les points bloquants derrière l'introduction de l'EUV, ASML est resté relativement muet. La question principale reste la vitesse d'exposition, qui était de 1000 wafers sur une période de 24h (il faut de nombreuses expositions pour réaliser une puce, dont la fabrication prend plusieurs semaines, la vitesse d'exposition est donc un point critique !), un peu en dessous du seuil minimal acceptable (50 à 100 exposition par heure, les machines « classiques » en font 250/h à titre de comparaison). Si ces chiffres semblent proche, l'autre problème est le taux de disponibilité des machines, nous notions la dernière fois que le générateur de goutes d'étain devait être changé tous les quatre jours et que sur une période de 8 semaines, le taux de disponibilité mesuré n'était que de 55%.

Côté rendement, les choses n'ont visiblement pas évolué puisque le même chiffre de 1000 sur une journée a été de nouveau évoqué. ASML indique cependant que sur des périodes de quatre semaines, plusieurs de ses clients ont atteint une disponibilité de plus de 70%. Si l'on pourrait y voir un progrès, le CEO d'ASML a noté qu'il s'agissait de meilleures situations et que la moyenne totale reste plus basse. Peter Wennink a également évoqué que les dernières générations de laser ont posé problème même si ces problèmes seraient résolus.

Le CEO s'est également félicité du fait que deux clients avaient indiqué la « nécessité » de l'EUV à 7nm, même si l'on notera que toutes les annonces que ce soit chez TSMC ou Intel étaient empruntes de prudence, quelque chose de compréhensible vu que des annonces identiques avaient été faites pour le 10nm ! On notera sur la question du 10nm qu'ASML a confirmé que Samsung, TSMC et Intel seront « proches » avec des livraisons à partir du second trimestre. Il a cependant été confirmé que le passage au 10nm serait « complexe » de par le fait que le multiple patterning était généralisé pour de nombreuses couches critiques et qu'il ne faudrait pas sous-estimer le temps nécessaire avant de voir en production ces puces sur le marché.

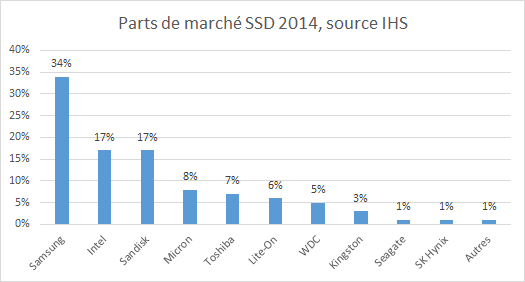

Samsung 1er du SSD avec 1/3 du marché

Selon les estimations du cabinet IHS publiées par ZD Net , Samsung est resté de loin le numéro un du SSD en 2014 avec 34% du marché mondial. Il est suivi par Intel et Sandisk qui se partagent chacun 17%, puis de Micron à 8%, Toshiba à 7%, Lite-On à 6%, WDC à 5%, Kingston à 3% et Seagate et SK Hynix à 1% chacun.

Nous ne disposons pas des estimations d'IHS pour les années précédentes, mais selon un autre institut (Gartner) le géant coréen était à 28,5% en 2013 contre 23,2% en 2012. Intel serait également en progression si un compare ces données après une baisse de 14,7% en 2012 à 13,1% en 2013 alors que Sandisk poursuit une croissance forte puisqu'il était à 5% en 2012 et 11,7% en 2013. Micron était pour sa part à 3,3% en 2012 et 6,9% en 2013, contre 9,2% et 5,6% pour Toshiba.