Les derniers contenus liés au tag MRAM

Toshiba perfectionne la MRAM

4 Mbits en MRAM chez Motorola

Roadmap MRAM

1eres puces MRAM chez Motorola

MRAM

La MRAM débarque sur un SSD PCIe

Alliance autour d'un nouveau bus mémoire

STT-MRAM 80% plus économe que la SRAM chez Toshiba

Hynix et Toshiba s'associent pour la MRAM

Nouvelle étape pour la MRAM !

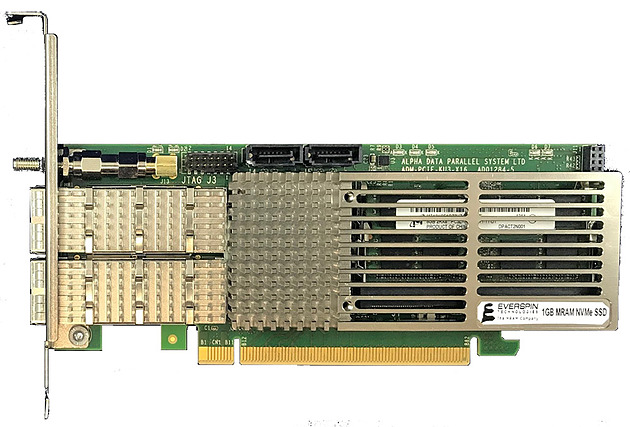

La MRAM débarque sur un SSD PCIe

La MRAM, dont on vous parle depuis 2000 tout de même, vient de faire son apparition sur un premier SSD, la carte fille PCI Express nvNITRO de Everspin. La MRAM est une mémoire non volatile n'utilisant pas une charge électrique mais magnétique pour stocker les bits contrairement à la DRAM, et dont on nous promet qu'elle réuni en une seule technologie les avantages de la DRAM, de la SRAM et de la NAND.

Les spécifications complètes ne sont pas dévoilées mais il est question d'une latence de 6µs pour un accès 4K là ou on Intel est par exemple à 20µs dans le meilleur des cas en NAND et 10µs en 3D XPoint. Côté IOPS on est à 1,5 millions d'accès en 4K aléatoire QD32 en lecture comme en écriture, les meilleurs SSD professionnels tels que le HGST Ultrastar SN260 étant à 1,2 millions en lecture mais 200K en écriture. Avec seulement une commande les chiffres sont tout de même de 175K et 150K IOPS en lecture/écriture.

La carte fille PCIe x8 Gen3 utilise un contrôleur basé sur un FPGA Xilinx UltraScale associé à 16 Go de DDR3 adressant de la MRAM au format SO-DIMM, elle dispose en plus de deux ports QSFP pour l'interfacer en réseau 10 ou 40 Gb ainsi que de deux ports SATA dont on ne connait pas trop l'usage. Le tout, clairement pas destiné à n'importe qui, est tout de même vendu 2800$ en version 1 Go ! En effet nvNITRO n'est pour le moment décliné qu'en versions 1 ou 2 Go de MRAM, du fait d'une capacité réduite de 32 Mo par puce. Everspin promet toutefois d'atteindre 4 à 16 Go cette année en utilisant sa ST-MRAM 128 Mo en cours de développement. Il faut un début à tout !

Alliance autour d'un nouveau bus mémoire

Plusieurs acteurs majeurs de l'industrie viennent d'annoncer une alliance dans le but de développer une nouvelle interface mémoire. Ils se sont regroupés au sein d'un consortium baptisé Gen-Z.

La page de description du consortium insiste sur un mode de fonctionnement transparent et ouvert. Le consortium en lui même est une organisation à but non lucratif (pour les puristes, une entreprise américaine de type "not for profit"). Le mode de développement sera transparent, et le standard final sera publié, disponible et utilisable gratuitement.

Techniquement il s'agit de proposer une nouvelle manière d'interconnecter la mémoire, ou plutôt les multiples types de mémoires qui pourront coexister à l'avenir.

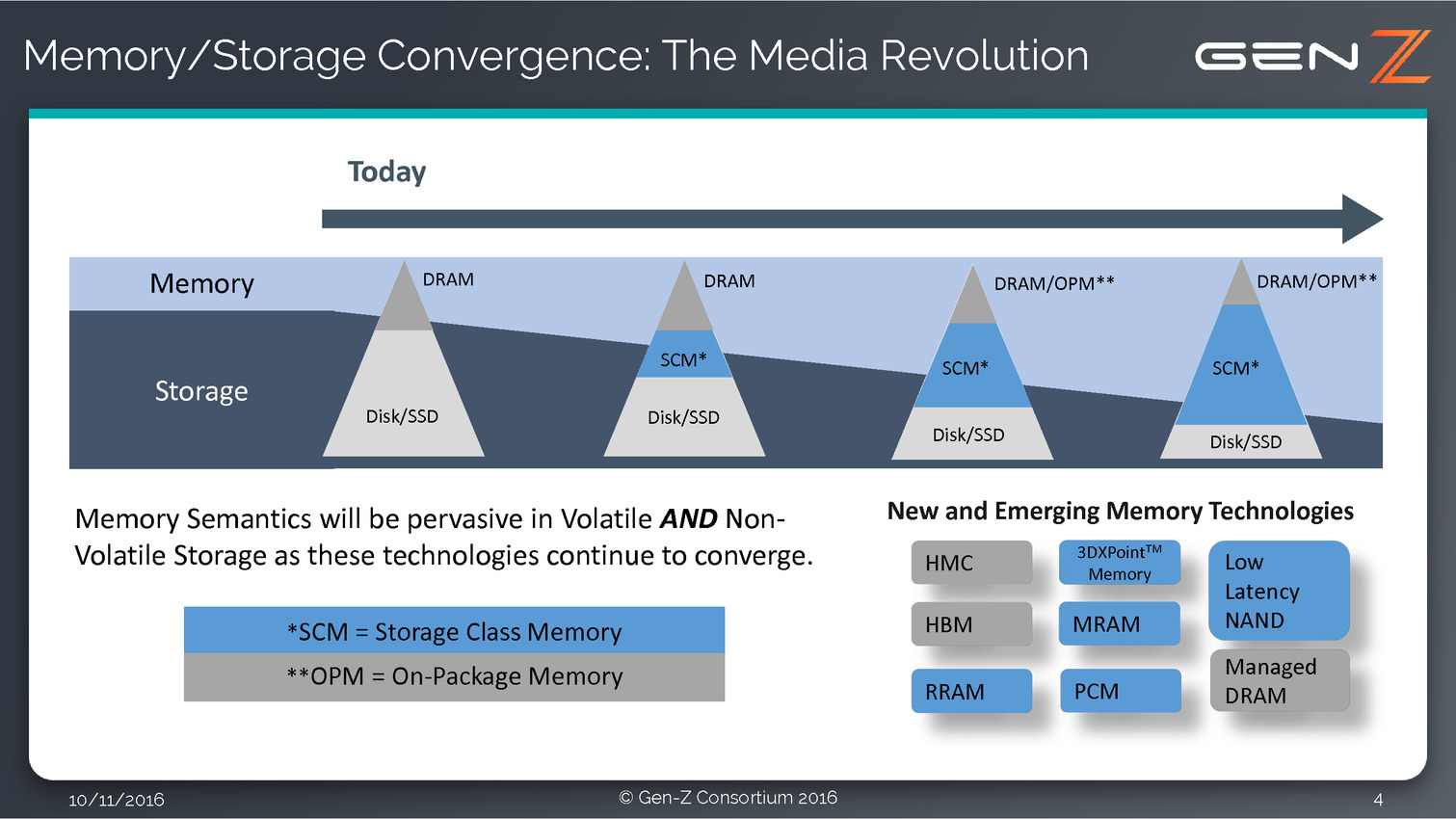

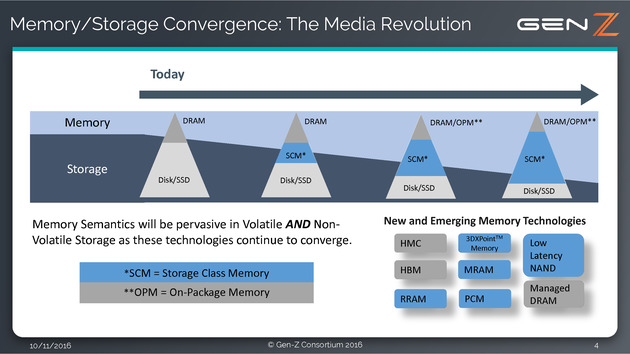

Le consortium prend l'exemple des nouveaux "types" de mémoires, appelés SCM (Storage Class Memory) comme peuvent l'être les RRAM, MRAM, ou les implémentations commerciales annoncées comme 3D XPoint chez Intel/Micron ou la Z-NAND de Samsung. Ces nouveaux types de mémoires viennent s'ajouter à la mémoire traditionnelle (DRAM) qui voit aussi arriver de nouvelles variantes (HBM ou HMC).

L'idée de base du consortium est de proposer une interface avec des commandes très simples, proches de celles utilisées pour la DRAM, mais qui puissent être utilisées aussi bien au sein d'un package, sur la carte mère, ou au delà (communication entre serveurs dans un data center). Le tout se doit de rester compatible avec l'existant, y compris les systèmes d'exploitations qui pourront exploiter ces nouvelles mémoires de manière transparente. Un but assez noble tant la question de comment adresser ce nouveau tiers de mémoire avait été évitée jusqu'ici.

Le consortium annonce qu'il utilisera entre autre le protocole IEEE 802.3 (Ethernet) comme protocole de communication interne (on pourra aussi utiliser Ethernet pour la couche physique de transport). En plus des protocoles, un nouveau connecteur devrait être annoncé pour tenter de standardiser ces futurs types de mémoire, il supportera jusque 112 GT/s.

Les objectifs fixés sont particulièrement audacieux, et on ne pourra que se féliciter de voir tant d'acteurs majeurs de l'industrie s'associer pour tenter de proposer un nouveau standard :

L'absent le plus notable est Intel, et il est difficile de ne pas voir cette alliance comme formée contre la firme de Santa Clara qui a tendance à développer ses bus de manière propriétaires, particulièrement pour tout ce qui touche au monde serveur.

Il est tout de même intéressant de voir que Micron, partenaire d'Intel sur 3D Xpoint est présent dans le consortium (3D Xpoint est même mentionné dans les slides de présentation). Il sera intéressant de suivre l'évolution de ce standard qui pourrait apporter des solutions concrètes aux problématiques d'interconnexions.

Vous pouvez retrouver la présentation du consortium ci dessous :

STT-MRAM 80% plus économe que la SRAM chez Toshiba

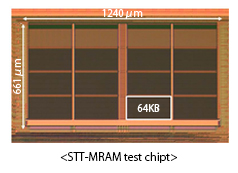

Avec la Resistive RAM (RRAM ou ReRAM) et la Phase-change RAM (PRAM), la Spin-transfer torque magnetic RAM (STT-RAM ou STT-MRAM) est l'une des mémoires non-volatiles en développement depuis des années et qu'on annonce comme révolutionnaire, pouvant remplacer selon les besoins la DRAM, la SRAM et la NAND.

Avec la Resistive RAM (RRAM ou ReRAM) et la Phase-change RAM (PRAM), la Spin-transfer torque magnetic RAM (STT-RAM ou STT-MRAM) est l'une des mémoires non-volatiles en développement depuis des années et qu'on annonce comme révolutionnaire, pouvant remplacer selon les besoins la DRAM, la SRAM et la NAND.

Lors de l'ISSCC 2015 Toshiba a présenté une puce prototype de 1 Mb qui a pour intérêt d'avoir une vitesse suffisante pour remplacer la SRAM pour un cache de dernier niveau (LLC), avec un temps d'accès de 3.3ns, tout en ayant une consommation réduite de 80% par rapport à la SRAM actuelle. Déjà l'an passé lors de la conférence VLSI une consommation en baisse de 60% avait été évoquée, on est donc au-delà grâce notamment à un usage plus intensif du power gating. C'est bien entendu surtout sur des SoC très basse consommation que ce type de gain aura un intérêt.

A terme Toshiba dit viser une baisse de 90% de la consommation par rapport à la SRAM classique d'ici à la fin de son année fiscale soit le 31 mars 2016. Reste à savoir quand tout ceci sera utilisé sur des produits commerciaux !

Hynix et Toshiba s'associent pour la MRAM

Le sud-coréen Hynix et le japonais Toshiba viennent d'annoncer leur collaboration pour le développement de la MRAM. Une fois le développement terminé, les deux compagnies entendent également coopérer au sein d'une joint-venture pour la production de la dite mémoire. Hynix et Toshiba indiquent qu'ils ont également étendus leur accord de licence croisé et de sous-traitance.

Cette alliance est assez étonnante puisque Hynix et Samsung avaient annoncés en 2008 la création d'une joint-venture 100% sud-coréenne vouée au co-développement et la standardisation de la MRAM. Ce projet est semble-t-il tombé à l'eau, alors que l'accord Hynix Toshiba intervient une semaine après la publication d'une nouvelle avancée de Toshiba dans le domaine de la MRAM.

Ce type d'alliance est assez habituel dans le secteur de la mémoire puisqu'il permet de réduire les risques liés au développement d'une nouvelle technologie et d'en accélérer la mise au point. Dans le domaine de la mémoire Flash NAND par exemple, Toshiba et SanDisk collaborent au sein de Flash Forward, alors qu'Intel et Micron sont regroupés sous IM Flash.

Nouvelle étape pour la MRAM !

Après la PRAM, c'est autour d'une autre arlésienne, la MRAM, de franchir une étape significative dans son développement. Pour rappel, cette mémoire non volatile n'utilise pas une charge électrique pour stocker les bits contrairement à la DRAM, mais une charge magnétique, à l'instar les disques durs. Depuis ses débuts, elle est présentée comme la mémoire idéale, capable de remplacer la DRAM, la SRAM et la NAND.

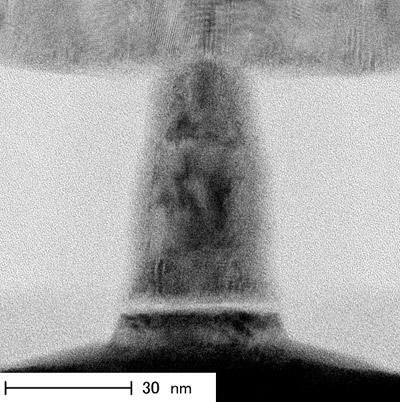

La lecture des données utilise le principe de la magnétorésistance à effet de tunnel, en mesurant la différence de potentiel entre deux couches ferromagnétiques. L'écriture se fait en modifiant le spin des électrons dans une des ces deux couches.

L'avancée présentée par Toshiba se situe au niveau de l'élément de base d'une mémoire STT-MRAM (spin torque transfert MRAM) qui intègre ces deux couches ferromagnétiques, le MTJ (magnetic tunnel junction). Ce nouveau MTJ nécessite en effet une intensité 6 fois plus faible pour l'écriture, alors que l'écart de résistance entre les états correspondants aux bits 0 et 1 passe de 15 à 200%, ce qui permet de fiabiliser la lecture.

Toshiba annonce ainsi qu'il a pu réduire l'intensité nécessaire pour écrire un MTJ de 50nm à 9µA, et qu'un MTJ de 30nm devrait être parfaitement fonctionnel. Selon le constructeur, les prévisions de l'ITRS (International Technology Roadmap for Semiconductors) sur la STT-MRAM ne tablaient pas sur de telles performances avant 2024.

Cette avancée ouvre la voie à la commercialisation d'ici 3 à 4 ans de puces STT-MRAM offrant des densités de l'ordre d'un Gigabit. Toshiba vise une production en volume dans un processus de fabrication antérieur d'une génération par rapport à celui utilisé sur la DRAM, ce qui ne l'empêche pas d'indiquer que les coûts de production des STT-MRAM et DRAM devraient être proches. Rendez-vous en 2015 pour voir si la promesse est tenue !