Les contenus liés au tag PRAM

Afficher sous forme de : Titre | FluxDu retard et de la PRAM pour 3D XPoint

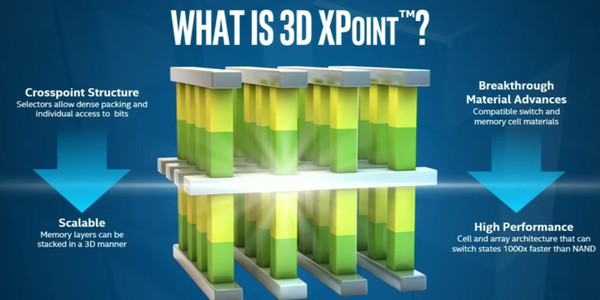

Annoncé en juillet 2015, la mémoire 3D XPoint est pour rappel une nouvelle technologie mémoire annoncée par Intel et Micron. Cette mémoire est censée offrir un compromis entre DRAM et NAND, que ce soit en termes de coût mais aussi de vitesse, tout en conservant la persistance de données de cette dernière. Elle pourrait ainsi être utilisée au sein de SSD offrant 5 à 8x plus d'IOPS mais aussi sur des DIMM. Combiné à de la DRAM, la ReRAM qui est certes un peu moins rapide permet en effet d'offrir pour un même tarif une capacité doublée.

Mais alors qu'il était initialement question d'un lancement commercial en 2016, Guy Blalock le co-DG d'IM Flash (joint-venture Intel/Micron) a indiqué qu'il faudrait encore 12 à 18 mois afin de pouvoir lancer la production en volume alors que les échantillons seraient presque prêts. Il faut dire que 3D Xpoint nécessiterais de nombreux nouveaux matériaux, dont certains ne sont trouvables que chez un seul fournisseur.

De plus à l'instar de ce qui se passe avec la migration vers la 3D NAND, le coût de la transition des chaines de fabrication de NAND classique vers 3D XPoint explose tout comme l'espace nécessaire pour assurer un bon débit du fait de nombreuses étapes supplémentaires dans la fabrication. Pour ne rien arranger les futures transitions vers les 3D Xpoint de seconde et troisième génération qui nécessiteront peut-être l'EUV devraient être aussi couteuses, alors que côté 3D NAND le coût sera divisé par 2.

Voilà qui tempère quelque peu les annonces en fanfare de l'été dernier, alors qu'à l'époque Intel et Micron avaient indiqués que la 3D Xpoint était en production ! Il ne s'agissait donc en aucun cas d'une production de puces finales et en volume. Au passage, Guy Blalock a enfin confirmé ce qui se cache derrière la 3D Xpoint, à savoir un matériau de type chalcogénure associé à un switch Ovonyx : on a donc à faire à de la PRAM (Phase-change memory) et non de la ReRAM.

Ovonyx est une société crée en 1999 entre autre par un ancien dirigeant de Micron et qui a longuement travaillé sur la PRAM et qui a vendu de nombreuses licences pour utiliser ses brevets à des entreprises tierces, Intel a investi dans la société en 2000 et 2005 et Micron a racheté des parts de la société en 2012. En juillet 2012 Micron avait annoncé être le premier à fabriquer une puce PCM en volume, à l'époque une puce de 128 Mo fabriquée en 45nm qui était combinée avec 64 Mo de LPDDR2 avant de mettre ensuite de côté la PCM pour plusieurs années. Espérons que 3D XPoint aura droit à un meilleur sort !

3 millions d'IOPS pour un SSD HGST en PRAM

HGST, filiale de Western Digital, annonce avoir mis au point un prototype de SSD capable d'atteindre le chiffre faramineux de 3 millions d'IOPS sur un SSD. Ce chiffre a été obtenu en aléatoire avec des accès en lecture de 512 octets, HGST annonce par ailleurs une latence de 1.5 µs. A titre de comparaison, ce SSD est donc environ 30 fois plus rapide que les meilleurs SSD SATA.

Pour arriver à de tels résultats le prototype de HGST utilise de la mémoire à changement de phase, ou PRAM, au sein d'un SSD utilisant une interface PCie x4 Gen2. Fabriquées en 45nm, les puces de PRAM utilisée affichent une densité de 1 Gb, bien loin des puces présentées par Samsung en 2011 qui étaient en 20nm pour une capacité de 8 Gb.

Histoire de remettre (un peu) les pieds sur terre, HGST a lancé simultanément un nouveau SSD PCie x8 Gen3, le FlashMAX III. Décliné en versions 1100, 1650 et 2200 Go, la version 1100 Go affiche un débit de 2.7 Go /s en lecture et 1.4 Go /s en écriture pour 549 000 IOPS en lecture et 295 000 IOPS en écriture (53 000 soutenues sur un SSD plein). La latence est cette fois de 20 µs, pour une endurance en écritures aléatoire de 2 écritures complètes par jour pendant 5 ans.

Une puce PRAM 8-Gbit chez Samsung

Les ingénieurs de Samsung effectueront la présentation d'une nouvelle puce de type PRAM en février prochain lors de la conférence dédiée aux circuits intégrés, l'ISSCC qui se tiendra du 19 au 23 février prochain à San Francisco. La technologie PRAM, également dite de mémoire à changement de phases est une technologie mémoire non volatile qui présente comme avantages théoriques principaux une augmentation drastique de la bande passante et de la durée de vie, tout en réduisant le cout de la remise à zéro d'une cellule, particulièrement gourmand sur les technologies Flash. L'implémentation pratique sous la forme de produits reste cependant assez limitée même si IBM (voir cette actualité précédente) et Samsung investissent assez fortement sur le sujet.

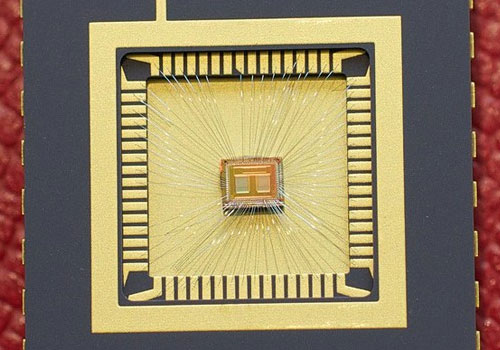

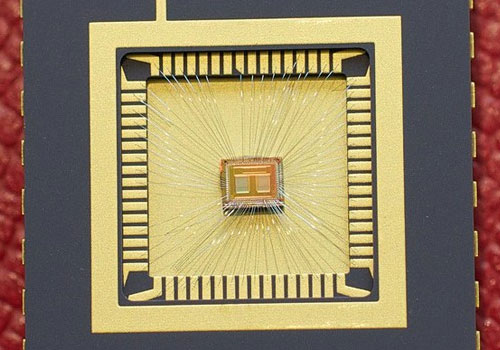

Un prototype de PRAM d'IBM en 90nm

Après avoir fait la démonstration d'une puce PRAM gravée en 58nm l'année dernière, Samsung annonce ici avoir produit une puce PRAM en 20nm, un bond en avant significatif pour la technologie. Côté densité, la puce atteint 8 Gbit, là ou le modèle 58nm atteignait simplement 1 Gb. La tension d'alimentation de la puce reste à 1.8V et atteint une bande passante de 40 Mo /s. La puce continue d'utiliser en effet une interface mémoire LPDDR2-N, équivalente à celle utilisée dans les smartphones. Le reste des caractéristiques techniques et des avancées seront dévoilées en partie la semaine prochaine par Samsung lors d'une réunion de l'IEDM.

Nouvelle étape pour la PRAM !

La mémoire à changement de phase, appelée également PCM (Phase-change Memory) ou PRAM (Phase-change Random Access Memory), vient de franchir une nouvelle étape avec la mise au point par IBM d'un prototype capable de stocker 2 bits mémoires dans une cellule. Ce pas est important puisqu'il permet à la PCM d'avoir une meilleure densité et donc coût par bit inférieur, comme c'est le cas pour la Flash MLC qui stocke également deux bits par cellule.

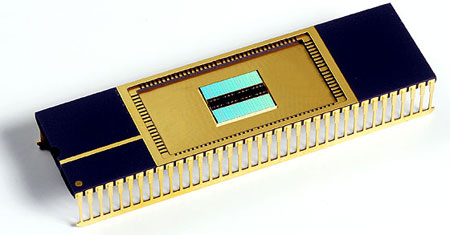

Pour l'instant on est toutefois loin d'une commercialisation et le prototype est une puce de 64 Mo gravée en 90nm, contre 25nm pour les dernières mémoires Flash. IBM vise pour le moment 2016 pour des applications serveurs, et a donc le temps de transposer la technologie sur des process plus fins d'ici là.

Comme la mémoire Flash NOR ou NAND, la PCM est non volatile et est donc capable de conserver les données même si elle n'est plus alimentée. Chaque cellule contient du chalcogénure, un matériau capable de passer d'un état vitreux (molécules en désordre) à un état cristallin (molécules rangées selon un motif). Ces deux états diffèrent par leur propriété électrique et la mesure de la résistance permet donc de lire les données qui sont écrites en changeant l'état par échauffement.

L'avancée d'IBM consiste donc à stocker gérer des états intermédiaires pour un total de 4 états correspondants à 00, 01, 10 ou 11 en termes binaires. Haris Pozidis, qui a mis au point la technologie, estime qu'il sera à terme possible de stocker 3 bits par cellules, voir 4 en changeant de matériaux.

Un problème à régler en urgence reste la gestion de l'évolution de la résistance des cellules au fil du temps. En utilisant des états intermédiaires, une telle mémoire est plus sensible à l'évolution de la résistance offerte par une cellule au fil du temps et qui peut entrainer des erreurs de lecture (lire 00 par exemple alors qu'on avait stocké 01). Pour contourner le problème IBM à mis au point un algorithme qui ne se base pas sur la résistance absolue pour mesurer l'état mais sur la résistance relative entre les cellules. Ceci permet à IBM d'annoncer un taux d'erreur d'environ 1 pour 100 000 après 37 jours à température ambiante, ce qui devrait permettre d'atteindre les 1 pour 10^15 (1 millions de milliards) avec une correction d'erreur, mais pour le moment l'algorithme n'as été utilisé que sur une puce de test plus petite et sur seulement 200 000 cellules.

Les promesses de la mémoire PCM sont multiples par rapport à la Flash, puisque IBM annonce des vitesses en écriture améliorées par un facteur de 100 avec une latence en écriture de seulement 10 microsecondes et une endurance d'au moins 10 millions de cycles. Reste maintenant à voir si ces promesses seront tenues en pratiques d'ici 2016 !

Pour rappel Samsung fabrique depuis 2009 de la PRAM , mais pour l'instant avec des spécifications qui la limite aux applications mobiles. Hynix et Micron travaillent également sur ce type de mémoire.

Samsung fabrique (enfin) la PRAM

Samsung vient dannoncer avoir débuté la production de sa mémoire à changement de phase (ou PRAM, pour Phase-change RAM). Fabriquée en 60nm, cette puce arrive 3 ans après le premier prototype fonctionnel et avec un an sur le planning initial. Destiné dans un premier temps aux appareils mobiles du fait dune consommation réduite, cette mémoire non-volatile pourrait à terme remplacer les mémoires Flash NOR dans ces appareils.

Quid des SSD ? Il nest pour le moment - et pas avant longtemps - pas question de concurrencer les mémoires Flash NAND, car même si la PRAM est meilleure par certains aspects, notamment parce quelle est plus endurante (100 millions décritures) et permet une reprogrammation des cellules par bit, leur vitesse décriture bien que 7 à 10x supérieure à la NOR est encore trop faible en comparaison à la NAND, tout comme leur densité.