Les contenus liés au tag DDR4

Afficher sous forme de : Titre | FluxCES: La DDR4 en démo chez Crucial

Le JEDEC publie (enfin !) la spec. DDR4

Quelques détails sur Haswell-EP/EN

La DDR4 débarque chez Micron

La DDR4 en 2014 pour Intel ?

Haswell-E : 8 coeurs et DDR4 en Core i7 ! (MAJ)

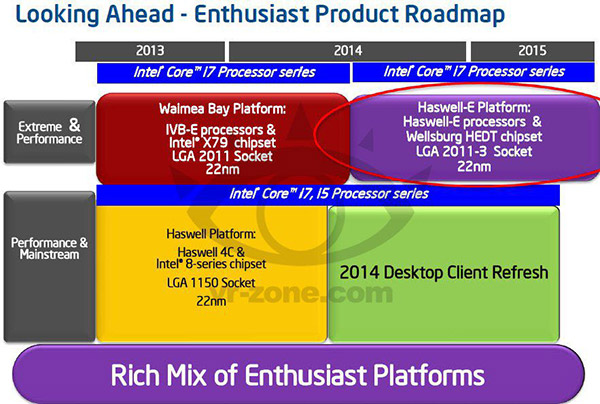

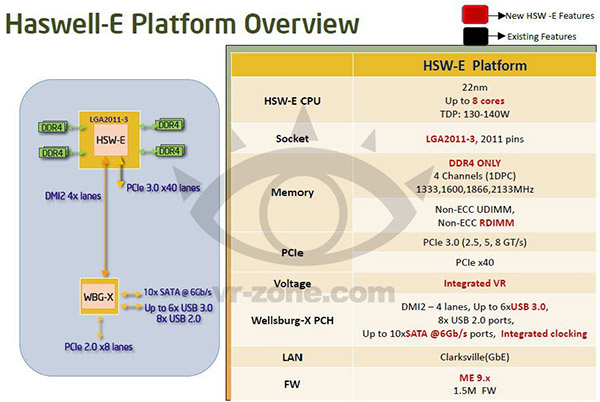

VR-Zone a publié quelques informations sur Haswell-E, prévu pour fin 2014, en provenance d'une roadmap Intel. Alors que les Sandy Bridge-E et Ivy Bridge-E sont déclinés en versions 4 et 6 curs en Core i7 LGA 2011, cette fois on aura droit à des versions 6 et 8 curs, avec un cache L3 qui sera toujours de 2.5 Mo par cur et qui pourra donc atteindre 20 Mo.

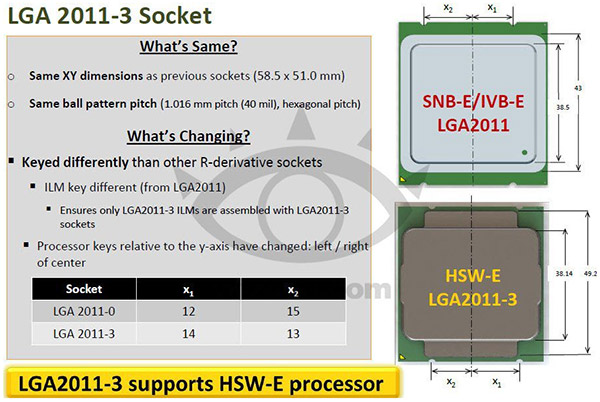

Ce changement sera pour rappel accompagné d'un nouveau Socket, qu'Intel nomme LGA 2011-3, et de cartes mères utilisant un nouveau chipset au nom de code de Wellsburg (X99 Express). Le processeur en reste à la gestion de 40 lignes PCIe Gen3, contre 16 sur LGA 1150, alors que le TDP sera de 130 à 140 watts.

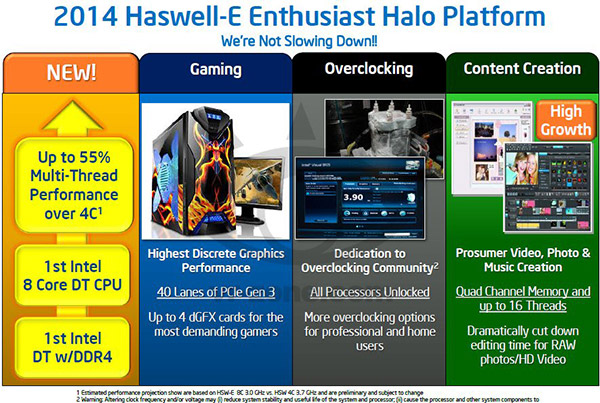

En sus du nombre de curs, cette plate-forme appelée Halo sera la première à accueillir la DDR4 ! Cette mémoire sera gérée sur 4 canaux, mais comme d'habitude Intel est assez conservateur en termes de vitesse puisque seule la DDR4-2133 est évoquée. En pratique toutefois les plates-formes LGA actuelles validées pour la DDR3-1600 ou DDR3-1866 vont bien plus haut et on peut s'attendre à la même chose.

Côté performances Intel annonce jusqu'à 55% de performances pour les Core i7 Haswell-E 8 curs par rapport aux Core i7 Haswell 4 curs, leur fréquence étant moindre dans cette estimation de performances : 3 GHz d'un côté contre 3.7 GHz de l'autre.

Si Intel précise qu'il ne ralentit pas ("We're Not Slowing Down !!"), on notera toutefois que les Ivy Bridge-E dans leur version Xeon existeront en versions 12 curs, et que les rumeurs font état de versions 14 curs pour Haswell-E. Ainsi, si en SNB-E les i7 avaient 75% des curs des Xeon, on sera à 50% avec les IVB-E et 57% en HSW-E. L'absence de ralentissement dépend donc du point de référence !

Mise à jour :

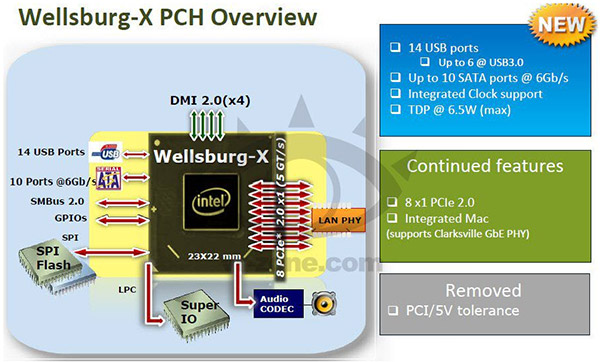

Voici quelques extraits supplémentaires de la documentation Intel, le premier fait état des différences physiques entre LGA 2011 et LGA 2011-3 (mêmes dimensions et densité de pins, mais détrompeurs placés différemment et un IHS qui évolue), le second parle des nouveautés du X99 Express ou Wellsburg-X : passage de 6 à 10 SATA, tous en 6 Gb/s contre 2 auparavant, et support de l'USB 3.0 sur 6 ports. Malheureusement la connexion avec le CPU se fait toujours en DMI 2.0 à 2 Go /s dans chaque sens. Enfin le dernier est un récapitulatif de la plate-forme, on notera la mention de 1DPC pour la DDR4, ce qui confirme le support d'une seule barrette DDR4 par canal du fait d'un bus point à point.

Computex: La DDR4 gagne 4 pins et de la Flash

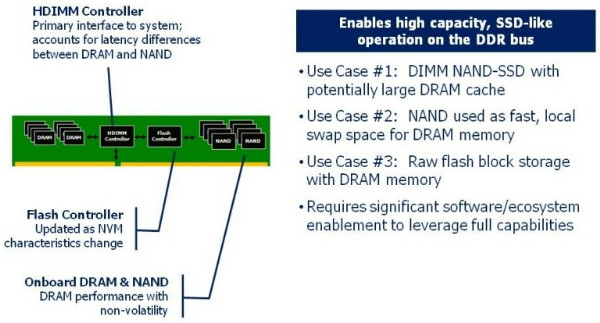

Initialement prévue sur un format DIMM 284 pins, la mémoire DDR4, toujours en cours de finalisation, est passée au format DIMM 288 pins nous explique Crucial/Micron. L'ajout de ces 4 pins supplémentaires a été décidé il y a quelques mois par le Jedec pour pouvoir alimenter le module en 12v. Pourquoi du 12v ? Pour pouvoir y placer de la Flash en plus de la DRAM et transformer le module en Hybrid DIMM.

Cela ne veut bien entendu pas dire que tous les modules DDR4 embarqueront de la Flash. Cette modification du futur standard est destinée à permettre cette possibilité et non à la généraliser. D'ailleurs, cette évolution en demandera bien d'autres, notamment au niveau du système d'exploitation, pour pouvoir être fonctionnelle et ainsi permettre de connecter un SSD directement au CPU. Avec un contrôleur adapté lui aussi présent sur le module, la partie DRAM DDR4 fera alors office de cache naturel.

Cette approche pourrait permettre de simplifier certains systèmes et d'apporter des gains de performances. Utilisée différemment, dans le monde professionnel, elle pourra également améliorer la fiabilité : ajoutez quelques condensateurs et en cas de coupure du système le contrôleur pourra transférer les données présentes en DRAM vers la Flash.

Notre interlocuteur chez Crucial n'était cependant pas certain que ce changement aurait une influence sur le format physique et nous a indiqué qu'il était possible que ces 4 pins n'allongent pas le module mémoire puisqu'un peu de place avait été réservé à côté du détrompeur (de quoi ajouter jusqu'à 4 pins de chaque côté du module si nous l'observons bien).

DDR4 pour 2014, devant la DDR3 en 2015 ?

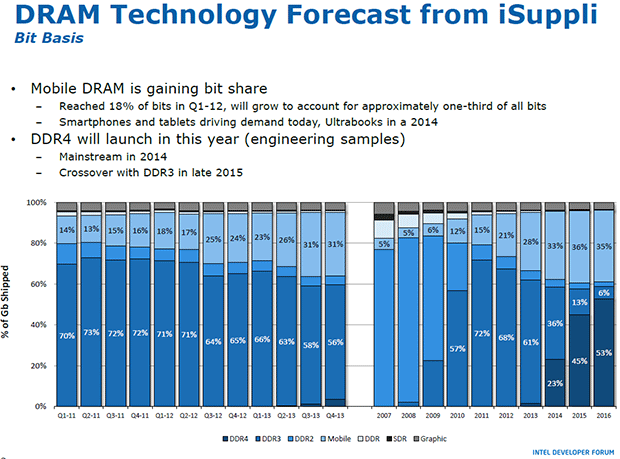

Selon les chiffres d'iSuppli publiés par Intel à l'occasion de l'IDF, la mémoire DDR4 devrait prendre son envol au cours de l'année 2014, avec pas moins de 23% de parts de marché en termes de Gb livrés. Dès 2015, elle prendra l'avantage sur la DDR3 et deviendra le type de DRAM le plus vendue avec 45% du marché.

Une transition finalement assez rapide puisque la DDR3, lancée en 2007, n'était pas passée devant la DDR2 avant 2010 d'après le même graphique.

Ces chiffres nous paraissent toutefois très optimistes. En effet, la répartition par trimestre montre que dès la fin de l'année 2013 la DDR4 occupera 3% du marché, alors qu'à notre connaissance aucune plate-forme ne devrait être disponible pour l'utiliser.

Même l'an prochain, il n'est pour le moment question de l'adoption de la DDR4 que sur Haswell-EX. Intel l'utilisera-t-il finalement sur les Broadwell 14nm BGA, avant une arrivée sur Desktop en 2015 avec Skylake ? Wait & see !

Quelques détails sur les LPDDR4, DDR4 et Wide I/O

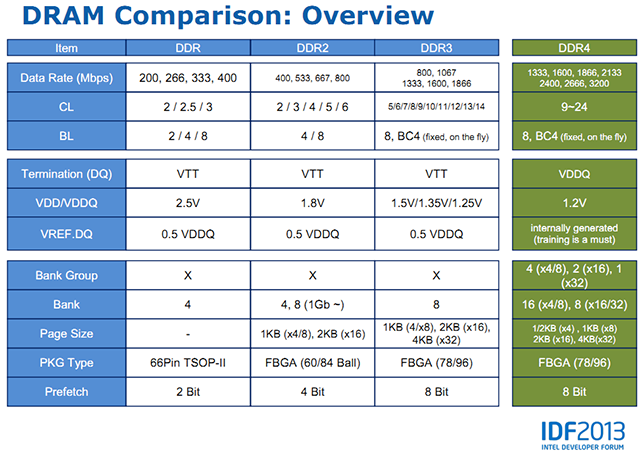

L'IDF de Pékin était aussi l'occasion pour Intel et ses partenaires d'évoquer les futurs standards mémoires DDR4 et LPDDR4. D'abord côté Intel ou l'on pouvait trouver ce slide qui compare les différentes versions de DDR :

Par rapport à la présentation que nous avions faite précédemment, on peut noter quelques petits changements. Notamment la mention des modes 3200 MT/s qui n'étaient que très peu évoquées dans la spécification originelle de la DDR4. Intel évoque ainsi des latences qui pourront atteindre 24 cycles. Pour le reste il s'agit des informations dont nous disposions déjà, pour rappel un des intérêts techniques principaux de la DDR4 tient dans l'organisation de l'adressage mémoire sous forme de groupes capables d'exécuter des instructions de manière indépendante.

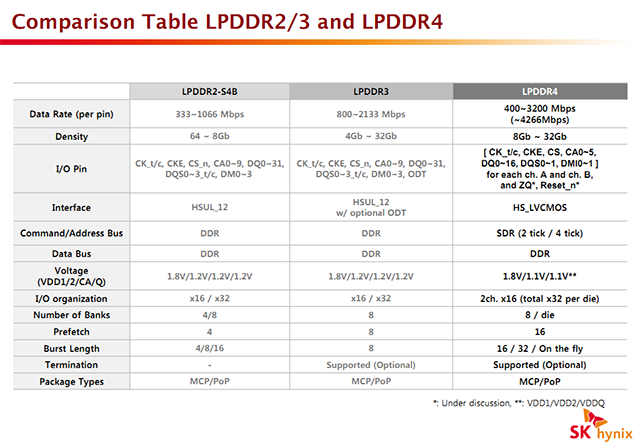

La LPDDR4 est également évoquée dans une présentation donnée par la société Hynix. Encore au rang de pré-standard pour le JEDEC, Hynix indique que la version finale devrait être ratifiée d'ici à la fin de l'année. Notez que si les noms se ressemblent, les standards LP ne sont pas identiques aux standards DDR classiques, à l'image de ce que l'on connait bien avec la GDDR par exemple. Les choix techniques effectués peuvent différer, l'objectif des standards LP étant de minimiser au maximum la consommation.

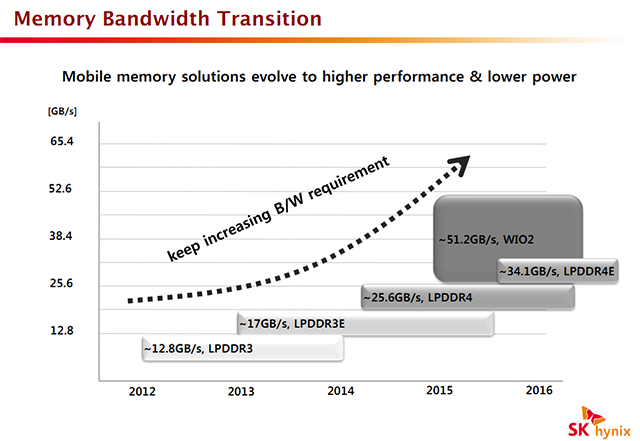

Comme toujours augmenter la bande passante est l'objectif, elle est doublée par rapport à la LPDDR3. On notera d'ailleurs sur ce graphique l'arrivée attendue d'un autre standard, Wide I/O 2. Un premier standard Wide I/O avait en effet été publié par le JEDEC fin 2011, il vise a standardiser la pratique dite du die stacking de mémoire, à savoir superposer des dies de mémoires par-dessus un SoC, le tout étant relié par le biais de TSV. La première version de Wide I/O avait avant tout pour but de régler les problèmes techniques autour de la solution et est relativement conservatrice en termes de débits, pouvant atteindre 17 Go/s (via une généreuse interface 512 bits !). La seconde version, attendue pour 2015 (le standard est encore loin d'être finalisé), visera des débits significativement plus élevés, pouvant atteindre 51 Go/s.

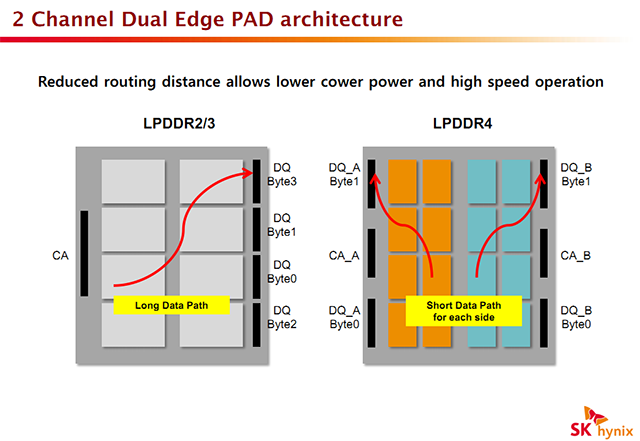

En ce qui concerne la LPDDR4, on notera au niveau des détails que la tension de base baisse de 1.2 à 1.1V par rapport à la LPDDR3, et une tension de terminaison qui est divisée par 3 (de 1.2V à 0.4V). Une réduction du routage fait également partie des objectifs attendus, ce qui devrait avoir pour conséquence un changement assez drastique dans le packaging.

Pour le reste, Hynix nous parait particulièrement optimiste en indiquant que la LPDDR4 sera disponible pour la mi-2014. Il faudra voir si cet enthousiasme sera partagé par le reste de l'industrie !

15, 12 et 10 coeurs pour les futurs Xeon

CPU-World donne quelques informations sur les futurs processeurs Intel Xeon gravés en 22nm destinés aux systèmes multi-Socket, l'occasion de faire le point sur ce qui est prévu au cours des prochains trimestres sur ce segment.

On commence par le très haut de gamme Xeon E7 v2 (Ivy Bridge-EX) destiné à la plate-forme Brickland et qui débarquera au quatrième trimestre 2013. Alors que les précédents Xeon E7 se "limitaient" à 10 curs et 30 Mo de cache L3, on passera cette fois à 15 curs et 37,5 Mo de cache L3. Le processeur supportera en sus 32 lignes PCI-Express 3.0 et pourra être utilisé dans des machines intégrant jusqu'à 8 sockets. Côté mémoire chaque processeur pourra être connecté à 4 Scalable Memory Buffers (SMB) pouvant gérer au total 24 barrettes DDR3-1600, mais une prochaine génération de ces SMB prévus sur Brickland ajoutera le support de la DDR4.

A titre d'information un Xeon E7-8870 (10 curs, 30 Mo de L3, 2,4 GHz, 130W) se monnaye tout de même 4616$. La plate-forme Brickland introduite à l'occasion de ce lancement devrait être compatible avec les futurs Haswell-EX (Xeon E7 v3) ainsi que leurs successeurs, une compatibilité qu'on aimerait voir sur d'autres gammes.

Les Xeon E5-2600 v2 et E5-4600 v2 (Ivy Bridge-EP) seront pour leur part destiné aux plates-formes Romley-EP 2 et 4 Socket déjà utilisée par Xeon E5-2600 et E5-4600 actuels (Sandy Bridge-EP). Prévus respectivement pour le troisième trimestre 2013, comme les Core i7 Ivy Bridge-E, et le premier trimestre 2014 ces processeurs Socket 2011 intégreront jusqu'à 12 curs pour 30 Mo de cache L3, contre 8 curs et 20 Mo actuellement. Ils disposeront également de 40 lignes PCI-Express 3.0 et de 4 canaux DDR3-1866.

Toujours sur la plate-forme Romley mais "-EN" 2 Socket 1356, le Xeon E5-2400 v2 (Ivy Bridge-EN) est pour sa part prévu pour le premier trimestre 2014. Cette version bridée de l'E5-2600 v2 sera limitée à 10 curs, 3 canaux DDR3 et 24 lignes PCI-Express.

Il faut noter que les futurs Haswell-EP et Haswell-EN (ainsi que d'éventuels Haswell-E en Core i7), prévus pour le second semestre 2014, utiliseront une nouvelle plate-forme dénommée Grantley utilisant un Socket R succédant au 2011. Le nombre de curs maximum devrait être porté de 12 à 14 et le cache L3 de 30 à 35 Mo. On restera à 40 lignes PCI-Express 3.0 alors que le contrôleur mémoire supportera officiellement la DDR4-2133 sur 4 canaux.

Enfin le nouveau chipset Wellsburg C610 gravé en 32nm (contre 65nm pour les actuels X79/C600) intégrera notamment la gestion de 10 ports SATA 6 Gbps et de 6 ports USB 3.0 pour un TDP de 7 watts, contre 8 watts pour un C602J (équivalent du X79) et 12 watts pour un C606 (avec la SCU ajoutant 8 SATA/SAS 3G active).

Malheureusement les 8 lignes PCI-Express gérées par le chipset seront toujours de type Gen2 et l'interconnexion avec le processeur se fera à toujours en DMI 2.0 ce qui correspond à un lien PCI-Express 4x Gen2 à 2 Go /s dans chaque sens : c'est loin d'être suffisant si on utilise pleinement tous les SATA. Ce choix est assez étrange alors que le chipset C606 intégrait en sus du lien DMI 2.0 un lien supplémentaire à 4 Go /s pour les 8 ports SATA/SAS 3G gérés par la SCU.