Les contenus liés au tag DDR4

Afficher sous forme de : Titre | FluxLe JEDEC évoque la DDR4

Hynix produit ses premières DDR4

Samsung premier sur la DDR4

La DDR4 se dévoile

CES: La DDR4 en démo chez Crucial

La DDR4, qui succèdera à la DDR3 sur la plateforme serveur Haswell-EX l'an prochain, et un peu plus tard du côté desktop, commence à se montrer. Lors de notre passage chez Micron/Crucial, nous avons ainsi pu observer une plateforme DDR4 fonctionnelle. Il s'agissait d'un système de test fourni par Intel, sans plus de précisions, et qui permet un monitoring avancé des modules mémoire.

La DDR4, que nous avions décrite plus en détail ici, est prévue avec des débits qui commenceront à 1600 MT/s ("1600 MHz") et monteront selon Crucial jusqu'à 3200 MT/s, voire plus, probablement avec une petite augmentation de la tension. Face à de la mémoire DDR3 qui atteint également des débits importants, l'intérêt principal de la DDR4 proviendra dans un premier temps de sa tension inférieure (1.2V contre 1.5V pour la DDR3 et 1.35V pour la DDR3L) et de diverses autres optimisation destinées à réduire la consommation. Un peu plus tard une variante basse consommation de la DDR4 verra également le jour avec une tension de 1V, 1.05V ou 1.1V, Crucial précisant que des discussions autour de cette tension étaient toujours en cours.

La démonstration, avec mémoire ECC, se limitait à un débit de 2133 MT/s, le maximum autorisé par la plateforme fournie par Intel, mais Crucial nous a précisé que dans ses labos le débit maximal actuellement défini par le JEDEC, 2400 MT/s, ne posait pas de soucis sur ces modules qui pouvaient par ailleurs fonctionner à 2600 MT/s.

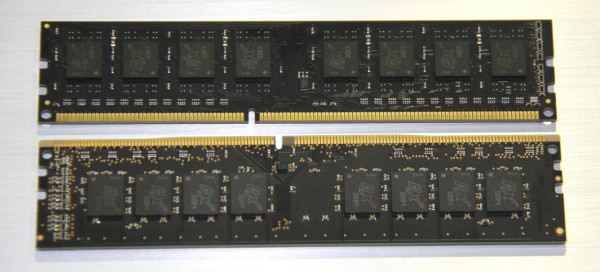

Petite particularité du format DIMM DDR4, illustré ici dans sa version grand public, sans ECC, les extrémités de son connecteur sont biseautées. Crucial explique que ce détail était important compte tenu de la densité plus élevée des pins et du placement plus central du détrompeur, sans quoi la pression exercée lors du montage devenait trop forte.

La DDR3 en haut et la DDR4 en bas.

Le JEDEC publie (enfin !) la spec. DDR4

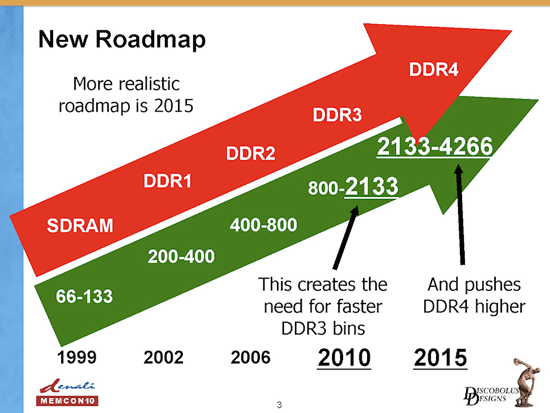

Attendue dans un premier temps fin 2011, puis pour la mi 2012, c'est finalement mardi dernier que le JEDEC - le consortium des différents acteurs de l'industrie informatique qui détermine les standards mémoires - a publié la spécification de ce qui sera le prochain standard mémoire de nos machines : la DDR4. Comme nous l'indiquions précédemment, là ou l'écart entre la publication de la DDR, DDR2 et DDR3 avait été entre chaque de quatre années, il aura fallu plus de sept ans entre la publication de la spécification de la DDR3 et celle de la DDR4.

Une longévité fortement accrue et qui s'est traduite par l'arrivée de barrettes qui dépassent très largement les objectifs d'origines de la DDR3 : on voit des modèles annoncés au-delà de la DDR3-2600 quand la spécification de la DDR3 ne validait officiellement les modules ne montant que jusqu'à 1600 (à l'origine, la spécification ayant été modifiée pour aller jusque 2133). Le JEDEC, qui n'aimait en général pas particulièrement ces dépassements (qui avaient existés auparavant, on se souvient par exemple de la DDR2-1066 là ou 800 était le maximum autorisé) à d'ailleurs fermé les yeux sur ces barrettes même si le communiqué reconnait que la DDR3 à "dépassé ses objectifs originaux de performances" et qu'il est probable que la DDR4 fasse de même.

Nous avions déjà évoqué dans une actualité précédente quelques unes des grandes lignes techniques qui devaient être utilisées pour la DDR4, à savoir l'utilisation de transferts de largeurs variables (32, 64 ou 128 bits effectifs par transfert au lieu de 64 uniquement pour la DDR3) ou l'implémentation du concept DBI (Data Bit Inversion) qui permet de simplifier certains transferts en inversant les bits dans le but de limiter la consommation.

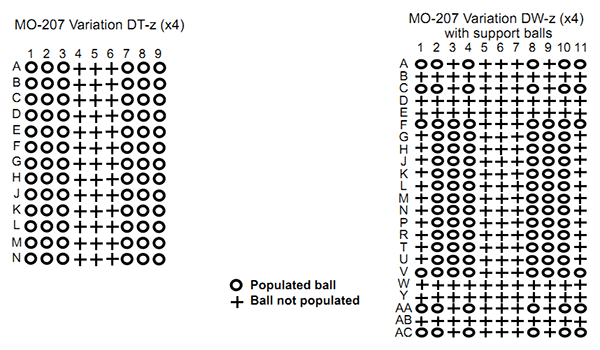

Version x4/x8 classique à gauche et version x16

L'organisation de l'adressage évolue avec l'apparition de groupes de banques indépendants les un des autres au sein puces. On trouve ainsi 2 groupes de 4 banques sur les puces x16 et 2 groupes de 4 banques sur les puces x16,, une nouveauté qui est à la base de l'amélioration des débits.

D'autres petits détails sont présents comme l'adaptation à la température de la puce qui doit pouvoir au minimum supporter 85°, un mode additionnel de fonctionnement jusqu'à 95° est également présent, dans ce cas les puces mémoires forceront un rafraichissement des données plus régulier pour éviter toute perte d'information (et plantage). Un mode de rafraichissement plus lent (période plus longue entre deux opérations) est également prévu pour un fonctionnement sous les 45°.

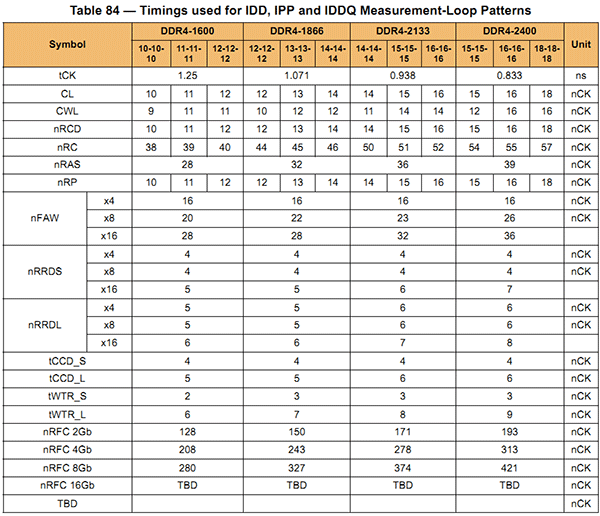

Du côté des débits, la DDR4 démarrera officiellement avec la DDR4-1600 (1600 MT/s) avec pour objectif d'atteindre 3200 MT/s d'ici à la fin de vie du standard. Les latences, exprimées en cycles paraitront forcément élevées même si l'on notera qu'elles sont assez proches de celles de la DDR3 actuelle (CAS 10 à 12 pour la DDR4-1600 au lieu de CAS9 couramment aujourd'hui pour la DDR3-1600). Ramenées en nanosecondes, ces latences restent très faibles et les multiples changements au niveau du fonctionnement interne font qu'il serait particulièrement faux de juger la DDR4 sur ces simples chiffres de latences.

Côté tensions, comme nous l'indiquions on passera de 1.5V à 1.2V pour la tension d'alimentation, sachant que des modules basse consommation (1.05V) sont également prévus (à l'image des barrettes DDR3 1.35V) sur le long terme. Une seconde tension de support à 2.5V (VPP) est également présente même si elle ne jouera qu'un rôle additionnel.

Nous nous devons enfin de noter que la spécification reste encore par endroit incomplète. Ainsi, si de manière normale certains timings ne sont pas encore définis au delà de 2400 MT/s, une (grande) partie de la spécification des timings électriques n'est pas du tout définie et ce pour toutes les fréquences de fonctionnement. Bien entendu cette première version de la spécification est amenée à évoluer d'ici à ce que les produits soient disponibles. La DDR4 est attendu pour rappel par Intel côté serveur pour 2014, et côté desktop pour 2015 au mieux comme nous l'indiquions ici .

Quelques détails sur Haswell-EP/EN

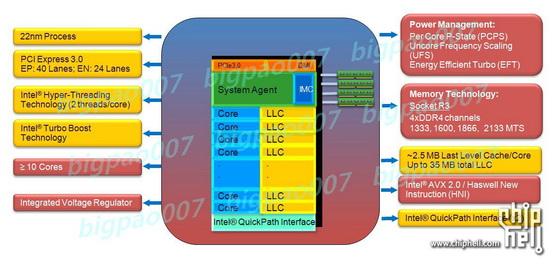

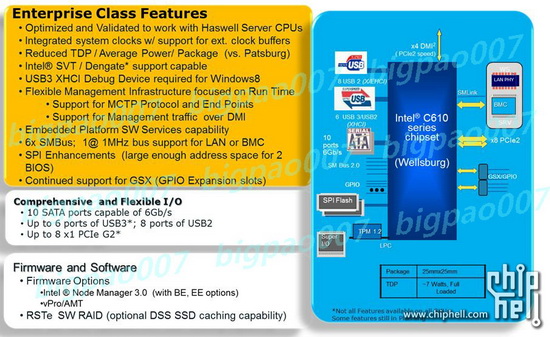

Nos confrères de CPU-World reviennent sur quelque slides qui ont été publiés sur le forum Chiphell et qui offrent quelques détails sur Haswell-EP/EN, la déclinaison Xeon bi-socket de l'architecture Haswell.

Côté caractéristiques on notera tout d'abord, comme nous l'avions indiqué un peu plus tôt, l'arrivée de la mémoire DDR4 sur cette plateforme, toujours gérée sur quatres canaux. Les puces pourraient disposer de plus de 10 curs (jusque 14 ?) avec jusque 35 Mo de cache commun, soit un maximum de 2.5 Mo/coeur.

Côté chipset, le C610 (Wellsburg) ferait suite à l'actuel C602 (Patsburg) et l'on noterait parmi les nouveautés la gestion de dix ports Serial ATA 6 GB/s ainsi que l'introduction d'un contrôleur USB 3.0 gérant 6 ports en simultanée. Rappelons que si Haswell est attendu dans sa déclinaison classique pour 2013, cette version haut de gamme EP/EN n'est elle pas attendue avant 2014.

La DDR4 débarque chez Micron

Après Samsung et Hynix il y a plus d'un an, Micron vient d'annoncer qu'il avait terminé le développement de son premier module de DDR4. Co-développée avec Nanya, cette barrette de 4 Go utilise 8 puces de 512 Mo de DDR4 fabriquées en 30nm. A terme Micron déclinera la DDR4 sur les formats RDIMM, LRDIMM, 3DS, SODIMM et UDIMM (classique et ECC), à des vitesses allant de la DDR4-2400 à la DDR4-3200.

La norme DDR4 est en cours de finalisation par le JEDEC et Micron annonce qu'il débutera la production en volume à compter du dernier trimestre 2012. Côté plate-forme il faudra attendre un peu puisque selon les dernières rumeurs Intel ne supportera pas la DDR4 avant 2014 sur serveurs et 2015 sur PC de bureau.

La DDR4 en 2014 pour Intel ?

Selon VR-Zone , Intel pourrait adopter la DDR4 dès début 2014 au sein de la plate-forme Haswell-EX. Destinée aux serveurs, cette plate-forme utilisera l'architecture Haswell 22nm qui sera introduite en 2013 sur LGA 1150, mais ira plus loin puisqu'il pourrait y avoir jusqu'à 16 curs par Socket, soit un besoin en bande passante énorme.

Côté desktop il ne faut toutefois pas attendre la DDR4 avant 2015 puisque la plate-forme LGA 1150 destinée à accueillir les Haswell au cours du premier semestre 2013 en restera à la DDR3. Broadwell, qui est un "tick" d'Haswell, c'est-à-dire une architecture proche mais portée sur un nouveau process 14nm, devrait a priori conserver cette infrastructure et donc la DDR3. Il faudra donc attendre la suite prévue pour 2015 pour un passage en DDR4. En attendant afin de satisfaire les besoins de l'IGP en terme de bande passante Intel aurait pour rappel l'intention de faire appel à un cache L4.